DAQ/Online: Lessons from DESY run Readiness for CERN beam test

Paul Dauncey

Imperial College London

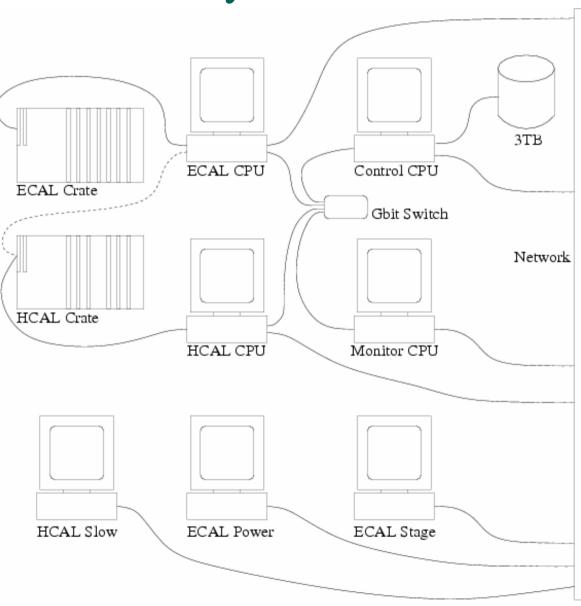

## DAQ hardware layout

## DESY run: reminder of the dates...

- ECAL modules

- Arrived on Mon 15 May

- Crate, trigger hardware installation

- Started on Fri 12 May

- Continued until Thu 18 May

- DAQ software setup

- Started on Sat 20 May

- Continued until Sun 21 May

- System stable from Mon 22 May onwards

- I.e. one week after ECAL modules arrived

- Ran until Wed 31 May

- Even after delay of one week, system not complete...

## My main conclusion from the DESY run

- The run almost didn't happen

- Many things were extremely marginal

- A fortunate accident that it worked at the last minute

- IMHO, main cause was lack of an overall coordinator

- No central setting of priorities

- No fixed start time of hardware setup

- ECAL packed up and not calibrated with cosmics after run

- ECAL stage PC shipped back to Paris and not left for further tests

- Late purchases of crate, cables, scintillators, etc.

- Everyone did what they thought was best

- But need an objective view to decide what is most important

## Issues from the DESY run (not complete)

#### • Hardware

- New TDC (for CERN use) did not have chamber inputs

- Single crate, not two crate system as will be used at CERN

- Veto scintillator with analogue-only readout; cannot veto events with beam hits previous to trigger

- Collimators not optimised

- Firmware

- 500 event limit as no time to test newer firmware

- Software

- New TDC not read out so no tracking data in CERN format

- No spill-mode running

- Some speed-ups not implemented

### What we learned

- Hardware takes at least one week to assemble

- Main delay seems to be getting a reliable trigger

- Saturates my time so no software work possible in parallel

- Once system is ready, it is reasonably stable

- 3 runs out of ~180 in stable period ended abnormally

- All 3 due to loss of socket connection to ECAL stage PC

- Only socket not going through the local hub

- Could be bug at either end or external network glitch

- This is why ECAL stage PC was shipped back from Paris

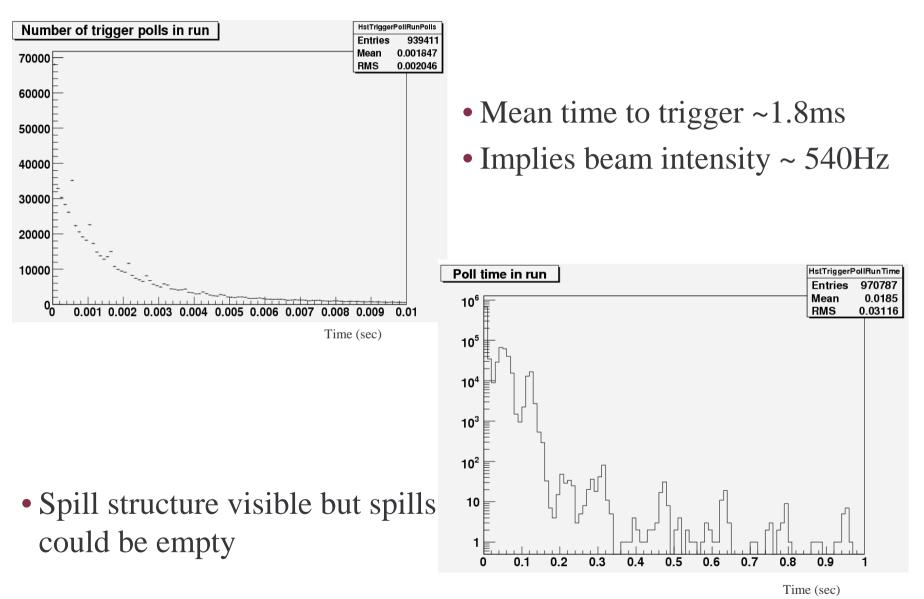

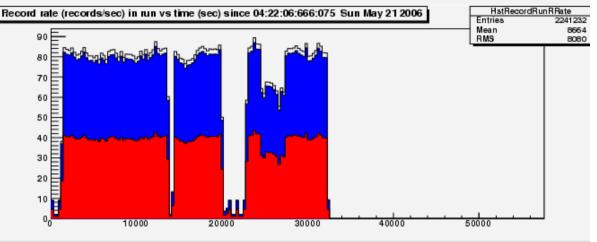

## Data rates at DESY

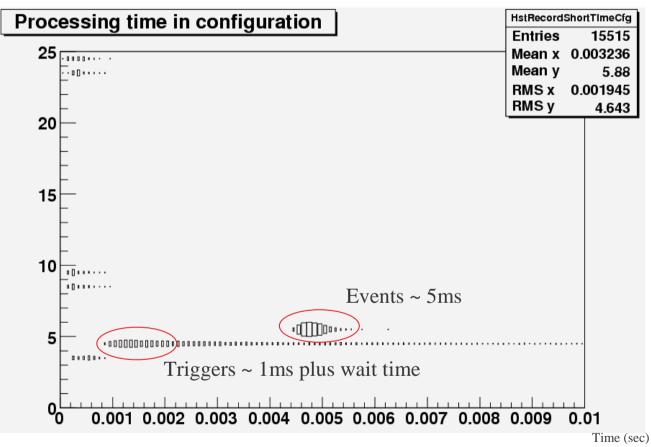

## Data rates (cont)

• Trigger processing is done separately from event readout

- Total average time for trigger wait and processing ~3ms

- Total average time for whole processing ~8ms

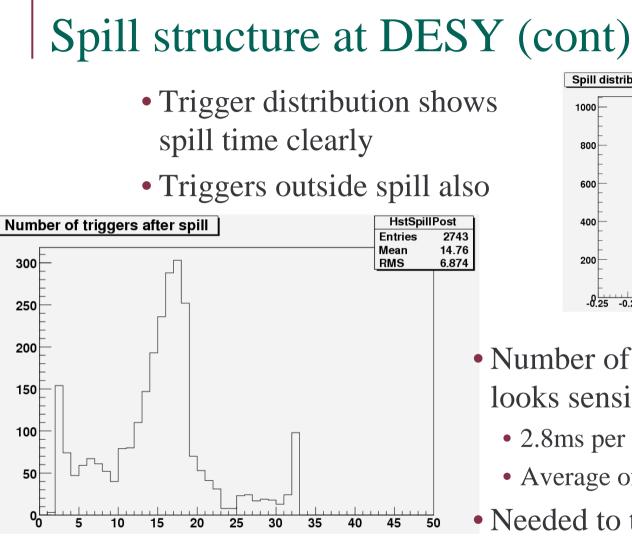

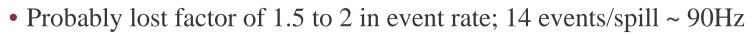

## Spill structure at DESY

• So why only 40Hz rate at DESY?

- The DESY beam is not continuous

- Has a spill structure which can change with machine settings

- Usually 160ms period with beam for (usually) 40ms within this; 25%

- Only found this out after ECAL installation

- Spill signal not wired into crate until the end of hardware setup

- Spill size completely different from CERN

- 16.8 sec period, beam for 4.8 sec

• No time to do this; spills ignored

- Number of triggers taken per spill looks sensible

- 2.8ms per trigger, 40ms spill

- Average of ~14 events expected

- Needed to tune rate

- Too many taken would miss next spill

## Preparations for CERN

- Since end of ECAL run have tried to put together "CERN system"

- Not yet achieved this

- Remaining issues:

- Hardware setup; no solid trigger distribution

- New TDC not yet proven

- HCAL slow PC communication not yet stable

- ECAL stage only just back at DESY

- Not the final trigger scintillators (so no HOLD measurement)

- Also DAQ work to be done on

- CRCs

- Firmware

- Software

# CERN tracking

- We can borrow CERN delay wire chambers

- Got a CAEN V767 TDC out from CERN loan pool

- 128 (!) channels, 800µs range, 0.75ns LSB, 32kword buffer

- TDC is complex and painful to use

- Full setup takes 7 sec (!), including 2 sec wait after reset

- Trigger is rounded to 25ns clock so need independent fiducial signal

- Not yet proved reliable as no good trigger yet

- Is 32kword buffer sufficient for 2000 events?

- Each event has header and end-of-buffer word

- Also need to read out fiducial signal

- Leaves average of 13 words per event

- Delay wire chambers have two channels/chamber

- Requested four x-y planes = 16 channels

- Buffer not sufficient to even store single hit/event, let alone noise

- With four planes of chambers must borrow a second TDC

DAQ - Paul Dauncey

## CRCs: from my talk at Montreal

- "Need to determine exact size of the problem

- How many bad channels now exist? Must use a VFE PCB to be sure

- Need systematic test of every FE connector input; who will do this?

- If problems seen, need to check alternative FE connector

- Also check if input is connected through to first stage of ADC circuit

- Adding bridging wires for broken traces can be done

- Probably best for Adam to do this; need to be done in the UK

- Do we return boards to the UK? Need to be sure enough left at DESY

- Need (realistic) schedule for ECAL/AHCAL module delivery"

- Nothing has been done on this; no progress

- I got a realistic (? to what level?) module schedule yesterday

## Firmware still to do

- Now have a version with 2000 event buffer

- Solution found for the limitation on storage size within FPGA...

- ... which has introduced a bug into the FE header data

- This only shows up for disabled (unused) FEs before enabled FEs

- Currently, engineer working on a fix; timescale unknown

- Workaround would be to enable a few extra FEs so no gaps

- Very recently have a version allowing trigger and ADC data to be mixed within one (slot 12) CRC

- Trigger event (history) data takes FE0

- Without this change, other seven FEs are unusable

- This version has not yet been tested at all

## Software still to do

- Online monitoring speedup

- Can limit run rate; mainly due to ROOT memory handling

- Have rewritten several parts to use shared memory instead

- Trigger code reorganise

- This is the part which is hacked around for different run types

- Has organically grown (into a mess); no longer reliable

- ECAL slow PC interface

- No work on this yet; plan is made but need to implement

- HCAL slow PC interface for CERN beam data

- Mainly working but new data for beam energy, etc, at CERN

- Data integrity checking code

- Need to be more sophisticated and check data structures more systematically

- Performance speed-ups

- Read-ahead for events; need to predict when event readout will occur

- Tune up for rate of scalar counter reads, histogram refresh rates, etc.

- Work with CERN spill timing structure

- Fake timing in software

- Tune parameters to optimise number of events taken

#### DAQ - Paul Dauncey

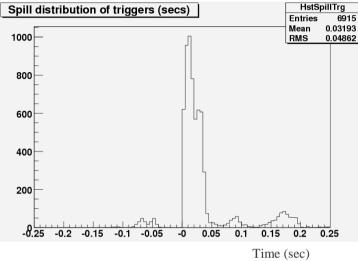

## Beam rates at CERN

- If the changes get done in time...

- Time to take an event

- Time waiting for a trigger = 1/r, r = beam rate

- Time processing trigger =  $t_t$

- Time reading out event =  $t_e$

- Limits on events per spill

- Maximum number of triggers in 4.8s spill =  $4.8/(1/r + t_t)$

- Maximum number of events in 16.8 spill period =  $16.8(1/r + t_t + t_e)$

- Maximum number of events in buffer = 2000

- High intensities give out-of-time hits

- A hit within t<sub>o</sub> before trigger leaves energy

- Probability of no out-of-time hit =  $exp(-t_or')$

- r' is beam rate into whole calorimeter, not just trigger scintillator

- Guesstimate r' ~ 2r?

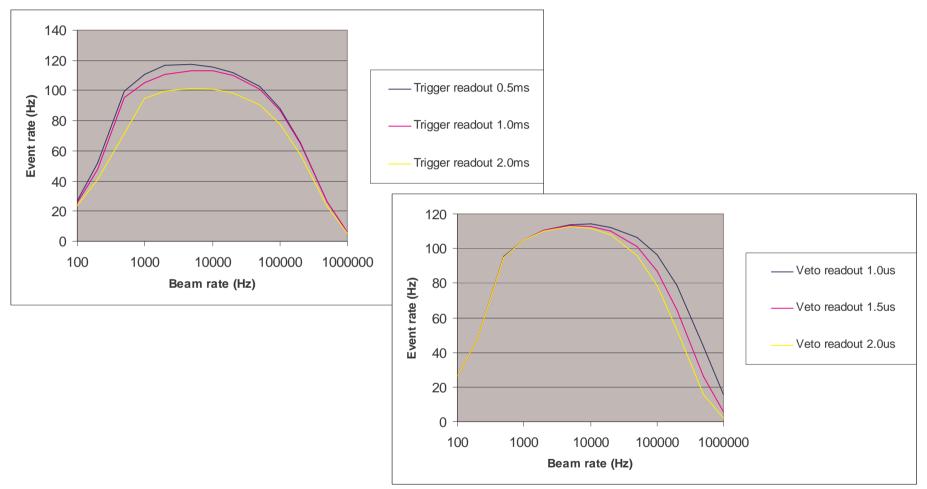

## Beam rates at CERN (cont)

- Some possible values

- Times:  $t_t = 1$ ms,  $t_e = 7.5$ ms,  $t_o = 1.5$ µs

- Gives an indication of event rate as a function of beam intensity

## Beam rates at CERN (cont)

- Optimal beam intensity is 3-10kHz in all cases

- Event readout most sensitive parameter but still hope to get 100Hz

## Summary

- There is still a lot of work to be done

- We will not have a reliable and efficient DAQ at CERN without this being completed

- Time has to be scheduled for all aspects of the installation

- Including time for DAQ development

- This is always the last thing to be prioritised...

- ...but the first thing to be criticised

- Essential to appoint a coordinator to oversee this

- Person has to be in place straight away