# Technical Information Manual

Revision n. 4 2 July 2003

MOD. V767

128 CH. GENERAL PURPOSE MULTIHIT TDC

**NPO:** 0000197:V767x.MUTx/04

# **TABLE OF CONTENTS**

| 1. | DESCRI         |                 |                                        |          |

|----|----------------|-----------------|----------------------------------------|----------|

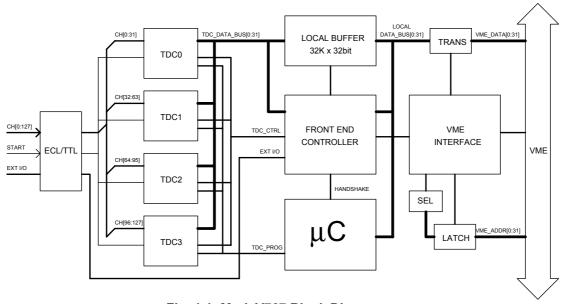

|    | 1.1.           | <b>FUNCTION</b> | AL DESCRIPTION                         | 6        |

|    | 1.2.           |                 | S OF OPERATION                         |          |

|    |                |                 | FOP TRIGGER MATCHING                   |          |

|    |                |                 | FART TRIGGER MATCHING                  |          |

|    |                |                 | FART GATING                            |          |

|    |                |                 | ONTINUOUS STORAGE                      |          |

|    |                |                 | OMMON STOP EMULATION                   |          |

|    |                |                 |                                        |          |

|    | 2.1.           |                 | 3                                      |          |

|    | 2.2.           |                 | COMPONENTS                             |          |

|    |                |                 | COMPONENTS                             |          |

|    |                |                 | RISTICS OF THE SIGNALS                 |          |

|    |                |                 |                                        |          |

|    |                |                 | QUIREMENTS                             |          |

| -  |                | _               |                                        |          |

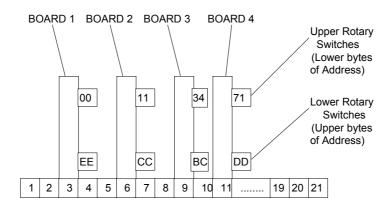

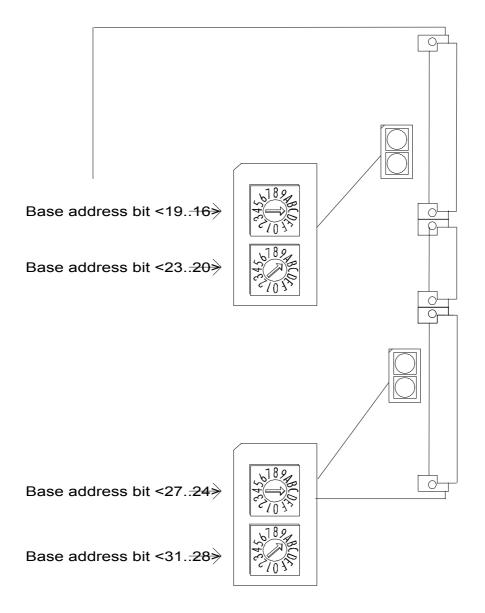

|    | 3.1.           |                 | NG CAPABILITY                          |          |

|    |                |                 | DDRESSING VIA BASE ADDRESS             |          |

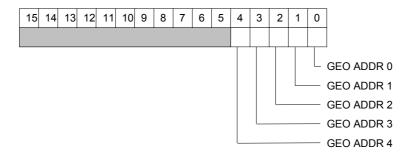

|    |                |                 | DDRESSING VIA GEOGRAPHICAL ADDRESS     |          |

|    |                |                 | ASE/GEO ADDRESSING EXAMPLE             |          |

|    |                | 3.1.4. M        | CST/CBLT ADDRESSING                    | 2        |

|    |                |                 | CST/CBLT ADDRESSING EXAMPLE            |          |

|    | 3.2.           |                 | ER CAPABILITY                          |          |

|    |                |                 | TERRUPT STATUS/ID                      |          |

|    |                |                 | TERRUPT LEVEL                          |          |

|    |                |                 | TERRUPT GENERATION                     |          |

|    | 0.0            |                 | TERRUPT REQUEST RELEASE                |          |

|    |                |                 | ISFER CAPABILITY                       |          |

|    |                |                 | JFFER                                  |          |

|    |                |                 | IICAL REGISTER                         |          |

|    |                |                 | GISTER                                 |          |

|    |                |                 | REGISTER                               |          |

|    | 3.8.           |                 | LEVEL REGISTER                         |          |

|    | 3.9.           |                 | VECTOR REGISTERGISTER 1                |          |

|    |                |                 |                                        |          |

|    | 3.11.          | ADDDECC F       | REGISTER 1                             | ئ∠<br>م  |

|    | 3.12.<br>3.13. | ADDRESS L       | DECODER REGISTER 32DECODER REGISTER 24 | ე∠<br>ექ |

|    |                |                 | RESS REGISTER                          |          |

|    | 3.14.          |                 | OT RESET REGISTER                      |          |

|    |                |                 | TROL REGISTER                          |          |

|    | 3.17.          |                 | GISTER 2                               |          |

|    | -              |                 | REGISTER 2                             | -        |

|    | 3.19.          |                 | INTER REGISTER                         |          |

|    |                |                 | NT COUNTER REGISTER                    |          |

|    |                |                 | ANDSHAKE REGISTER                      |          |

|    |                |                 | EGISTER                                |          |

|    |                |                 | SISTER                                 |          |

|    |                |                 | HIGH REGISTER                          |          |

|    |                |                 | LOW REGISTER                           |          |

|    | 3.26.          |                 | TRIGGER REGISTER                       |          |

|    |                |                 | )                                      |          |

|    |                |                 | MING CAPABILITY                        |          |

|    |                |                 | DES                                    |          |

|    |                | 4.2.1. EN       | NABLE MEMORY TEST MODE (CODE 01xx)     | 4/       |

|    |                | 4.2.2. DI       | SABLE MEMORY TEST MODE (CODE 02xx)     | 4/       |

|    |                |                 | EAD MEMORY TEST ON/OFF (CODE 03xx)     |          |

|    |                |                 | ON MODE OPCODES                        |          |

|    | _              |                 | ET STOP TRIGGER MATCHING (CODE 10xx)   |          |

|    |                |                 | ET START TRIGGER MATCHING (CODE 11xx)  |          |

|    |                | _               | ,                                      |          |

|      | 400                                                                                                                                                                                          | OFT OTART CATING (CORE 40)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                              |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

|      | 4.3.3.                                                                                                                                                                                       | SET START GATING (CODE 12xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                              |

|      | 4.3.4.                                                                                                                                                                                       | SET CONTINUOUS STORAGE (CODE 13xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

|      | 4.3.5.                                                                                                                                                                                       | READ ACQUISITION MODE (CODE 14xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 45                                                                                           |

|      | 4.3.6.                                                                                                                                                                                       | LOAD DEFAULT CONFIGURATION (CODE 15xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                              |

|      |                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                              |

|      | 4.3.7.                                                                                                                                                                                       | SAVE USER CONFIGURATION (CODE 16xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                              |

|      | 4.3.8.                                                                                                                                                                                       | LOAD USER CONFIGURATION (CODE 17xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                              |

|      | 4.3.9.                                                                                                                                                                                       | ENABLE AUTO LOAD (CODE 18xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 45                                                                                           |

|      | 4.3.10.                                                                                                                                                                                      | DISABLE AUTO LOAD (CODE 19xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                              |

|      | 4.3.11.                                                                                                                                                                                      | READ AUTO LOAD (CODE 1Axx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                              |

| 4.4  | -                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                              |

| 4.4. |                                                                                                                                                                                              | EL ENABLE OPCODES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                              |

|      | 4.4.1.                                                                                                                                                                                       | ENABLE CHANNEL nn (CODE 20nn)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                              |

|      | 4.4.2.                                                                                                                                                                                       | DISABLE CHANNEL nn (CODE 21nn)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 46                                                                                           |

|      | 4.4.3                                                                                                                                                                                        | READ STATUS CHANNÈL nn (CODÉ 22nn)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

|      | 4.4.4.                                                                                                                                                                                       | ENABLE ALL CHANNELS (CODE 23xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                              |

|      |                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                              |

|      | 4.4.5.                                                                                                                                                                                       | DISABLE ALL CHANNELS (CODE 24xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 46                                                                                           |

|      | 4.4.6.                                                                                                                                                                                       | WRITE ENABLE PATTERN (CODE 25xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 47                                                                                           |

|      | 4.4.7.                                                                                                                                                                                       | READ ENABLE/DISABLE WORDS (CODE 26xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 47                                                                                           |

| 4.5. | TRIGGE                                                                                                                                                                                       | R OPCODES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                              |

| 1.0. | 4.5.1.                                                                                                                                                                                       | SET WINDOW WIDTH (CODE 30xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                              |

|      | -                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                              |

|      | 4.5.2.                                                                                                                                                                                       | READ WINDOW WIDTH (CODE 31xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                              |

|      | 4.5.3.                                                                                                                                                                                       | SET WINDOW OFFSET (CODE 32xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 48                                                                                           |

|      | 4.5.4.                                                                                                                                                                                       | READ WINDOW OFFSET (CODE 33xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 49                                                                                           |

|      | 4.5.5.                                                                                                                                                                                       | SET TRIGGER LATENCY (CODE 34xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                              |

|      | 4.5.6.                                                                                                                                                                                       | READ TRIGGER LATENCY (CODE 35xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                              |

|      |                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                              |

|      | 4.5.7.                                                                                                                                                                                       | ENABLE SUBTRACTION OF TRIGGER TIME (CODE 36xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                              |

|      | 4.5.8.                                                                                                                                                                                       | DISABLE SUBTRACTION OF TRIGGER TIME (CODE 37xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 49                                                                                           |

|      | 4.5.9.                                                                                                                                                                                       | ENABLE OVERLAPPING TRIGGERS (CODE 38xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 49                                                                                           |

|      | 4.5.10.                                                                                                                                                                                      | DISABLE OVERLAPPING TRIGGERS (CODE 39xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 40                                                                                           |

|      | 4.5.11.                                                                                                                                                                                      | READ TRIGGER CONFIGURATION (CODE 3Axx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                              |

| 4.0  |                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                              |

| 4.6. |                                                                                                                                                                                              | OPCODES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                              |

|      | 4.6.1.                                                                                                                                                                                       | ENABLE READOUT OF START TIME (CODE 40xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                              |

|      | 4.6.2.                                                                                                                                                                                       | ENABLE READOUT OF 4 START TIMES (CODE 41xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 50                                                                                           |

|      | 4.6.3.                                                                                                                                                                                       | DISABLE READOUT OF START TIME (CODE 42xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                              |

|      | 4.6.4.                                                                                                                                                                                       | ENABLE SUBTRACTION OF START TIME (CODE 43xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                              |

|      | 4.6.5.                                                                                                                                                                                       | DISABLE SUBTRACTION OF START TIME (CODE 44xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                              |

|      |                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                              |

|      | 4.6.6.                                                                                                                                                                                       | ENABLE EMPTY START (CODE 45xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                              |

|      | 4.6.7.                                                                                                                                                                                       | DISABLE EMPTY START (CODE 46xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 50                                                                                           |

|      | 4.6.8.                                                                                                                                                                                       | READ START CONFIGURATION (CODE 47xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 50                                                                                           |

| 4.7. | ADJUST                                                                                                                                                                                       | OPCODES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                              |

|      | 4.7.1.                                                                                                                                                                                       | SET CHANNEL NN ADJUST (CODE 50nn)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 51                                                                                           |

|      | 4.7.2.                                                                                                                                                                                       | READ CHANNEL NN ADJUST (CODE 51nn)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 51                                                                                           |

|      |                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                              |

|      | 4.7.3.                                                                                                                                                                                       | SET GLOBAL OFFSET (CODE 52xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                              |

|      | 4.7.4.                                                                                                                                                                                       | READ GLOBAL OFFSET (CODE 53xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 52                                                                                           |

|      | 4.7.5.                                                                                                                                                                                       | ENABLE CHANNEL ADJUST (CODE 54xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 52                                                                                           |

|      | 4.7.6.                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                              |

|      |                                                                                                                                                                                              | DISABLE CHANNEL AD ILIST (CODE 55xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2                                                                                            |

|      |                                                                                                                                                                                              | DISABLE CHANNEL ADJUST (CODE 55xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

|      | 4.7.7.                                                                                                                                                                                       | RESET ALL ADJUSTS (CODE 56xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 52                                                                                           |

|      | 4.7.7.<br>4.7.8.                                                                                                                                                                             | RESET ALL ADJUSTS (CODE 56xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 52<br>52                                                                                     |

| 4.8. | 4.7.7.<br>4.7.8.                                                                                                                                                                             | RESET ALL ADJUSTS (CODE 56xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 52<br>52<br>52                                                                               |

| 4.8. | 4.7.7.<br>4.7.8.                                                                                                                                                                             | RESET ALL ADJUSTS (CODE 56xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 52<br>52<br>52                                                                               |

| 4.8. | 4.7.7.<br>4.7.8.<br>EDGE D<br>4.8.1.                                                                                                                                                         | RESET ALL ADJUSTS (CODE 56xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 52<br>52<br>52                                                                               |

| 4.8. | 4.7.7.<br>4.7.8.<br>EDGE D<br>4.8.1.<br>4.8.2.                                                                                                                                               | RESET ALL ADJUSTS (CODE 56xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 52<br>52<br>52<br>52                                                                         |

| 4.8. | 4.7.7.<br>4.7.8.<br>EDGE D<br>4.8.1.<br>4.8.2.<br>4.8.3.                                                                                                                                     | RESET ALL ADJUSTS (CODE 56xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 52<br>52<br>52<br>52<br>52<br>52<br>52                                                       |

| 4.8. | 4.7.7.<br>4.7.8.<br>EDGE D<br>4.8.1.<br>4.8.2.<br>4.8.3.<br>4.8.4.                                                                                                                           | RESET ALL ADJUSTS (CODE 56xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                              |

| 4.8. | 4.7.7.<br>4.7.8.<br>EDGE D<br>4.8.1.<br>4.8.2.<br>4.8.3.                                                                                                                                     | RESET ALL ADJUSTS (CODE 56xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 52<br>52<br>52<br>52<br>52<br>52<br>52<br>52                                                 |

| 4.8. | 4.7.7.<br>4.7.8.<br>EDGE D<br>4.8.1.<br>4.8.2.<br>4.8.3.<br>4.8.4.                                                                                                                           | RESET ALL ADJUSTS (CODE 56xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 52<br>52<br>52<br>52<br>52<br>52<br>52<br>53<br>53                                           |

| 4.8. | 4.7.7.<br>4.7.8.<br>EDGE D<br>4.8.1.<br>4.8.2.<br>4.8.3.<br>4.8.4.<br>4.8.5.                                                                                                                 | RESET ALL ADJUSTS (CODE 56xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 52<br>52<br>52<br>52<br>52<br>52<br>52<br>53<br>53                                           |

| 4.8. | 4.7.7.<br>4.7.8.<br>EDGE D<br>4.8.1.<br>4.8.2.<br>4.8.3.<br>4.8.4.<br>4.8.5.<br>4.8.6.<br>4.8.7.                                                                                             | RESET ALL ADJUSTS (CODE 56xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 52<br>52<br>52<br>52<br>52<br>52<br>52<br>53<br>53                                           |

|      | 4.7.7.<br>4.7.8.<br>EDGE D<br>4.8.1.<br>4.8.2.<br>4.8.3.<br>4.8.4.<br>4.8.5.<br>4.8.6.<br>4.8.7.<br>4.8.8.                                                                                   | RESET ALL ADJUSTS (CODE 56xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 52<br>52<br>52<br>52<br>52<br>52<br>52<br>53<br>53<br>53                                     |

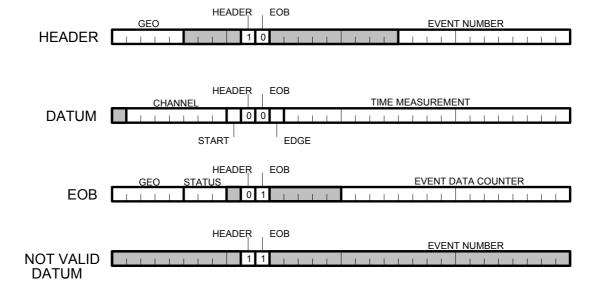

| 4.8. | 4.7.7.<br>4.7.8.<br>EDGE D<br>4.8.1.<br>4.8.2.<br>4.8.3.<br>4.8.4.<br>4.8.5.<br>4.8.6.<br>4.8.7.<br>4.8.8.<br>DATA RI                                                                        | RESET ALL ADJUSTS (CODE 56xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 52<br>52<br>52<br>52<br>52<br>52<br>52<br>53<br>53<br>53                                     |

|      | 4.7.7.<br>4.7.8.<br>EDGE D<br>4.8.1.<br>4.8.2.<br>4.8.3.<br>4.8.4.<br>4.8.5.<br>4.8.6.<br>4.8.7.<br>4.8.8.<br>DATA RI                                                                        | RESET ALL ADJUSTS (CODE 56xx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 52<br>52<br>52<br>52<br>52<br>52<br>53<br>53<br>53<br>53                                     |