# CMOS Monolithic Active Pixel Sensors (MAPS)

for future vertex detectors

... but not just

Dr Renato Turchetta CMOS Sensor Design Group CCLRC - Technology

SNIC 2006

# **Outline**

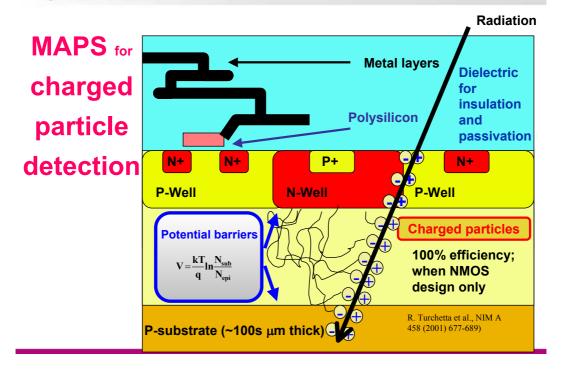

Introduction. MAPS for charged particle detection

Results so far

3T-pixel

Pipeline pixels

Digital sensors/pixels

MAPS in an experiment

**STAR**

**Belle**

ILC: vertex and calorimetry

Conclusion

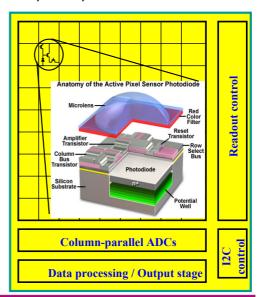

### **CMOS Monolithic Active Pixel Sensor (MAPS)**

(Re)-invented at the beginning of '90s: JPL, IMEC, ...

- Standard CMOS technology

- > all-in-one detector-connectionreadout = *Monolithic*

- small size / greater integration

- low power consumption

- radiation resistance

- > system-level cost

- Increased functionality

- increased speed (column- or pixel- parallel processing)

- ➤ random access (Region-of-Interest ROI readout)

SNIC 2006

Digital mammography

# CMOS sensors in digital cameras

# 3T pixel

Baseline (minimum) design.

Low noise detection of MIPs first demonstrated in 2001.

Since then, with a number of technologies/epi thickness:

AMS 0.6/14, 0.35/∞, 0.35/14, 0.35/20, AMIS (former MIETEC) 0.35/4, 0.25/2, TSMC 0.35/10, 0.25/8, 0.25/∞, UMC 0.18/∞

IBM

Noise <~ 10 e- rms

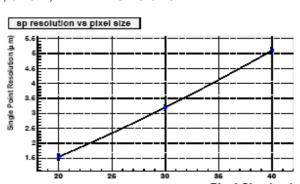

Spatial resolution 1.5 µm

@ 20  $\mu$ m pitch, with full analogue readout

Good radiation hardness

Low power

Speed: rolling shutter

can be a limit

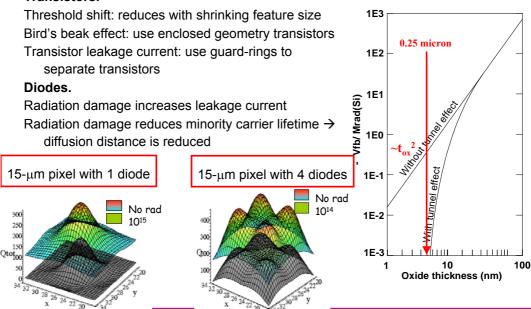

### **Radiation hardness**

#### Transistors.

SNIC 2006

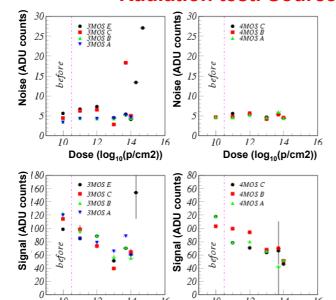

### Radiation test. Source results

- Test with parametric test sensor RAL\_HEPAPS2.

Designed in TSMC 0.25/8, inpixel transistors with 0.35equivalent oxide thickness

- Several types of pixels

- Noise seems to increase slightly with dose.

- Signal decreases with dose.

- Leakage current increase only noticeable beyond 10<sup>14</sup> p/cm<sup>2</sup>

# Pipeline pixels

Flexible Active Pixel Sensor (FAPS, RAL): TSMC 0.25/8, 10 memory cell per pixel; 28 transistors per pixel; 3 sub-arrays of 40x40 pixels @ 20  $\mu$ m pitch, sampling rate up to 10 MHz. Noise ~ 40 e- rms, single-ended readout

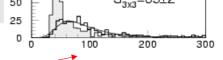

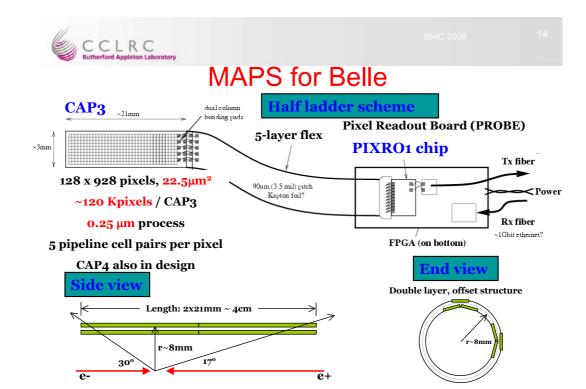

Continuous Acquisition Pixel (CAP, Hawaii): three versions (CAP1/2/3) in TSMC 0.35/8 and 0.25/8, 5 pairs cell/pixel in CAP3 40-50 e- rms single ended  $\rightarrow$  20-25 differential

MIMOSA12 (Strasbourg) in AMS 0.35/14: 4 pairs/pixel

SNIC 2006

10

# **Digital readout**

- Several imagers designed by RAL with column-parallel ADC: single-slope (10-bit) and successive approximation (up to 14-bit)

- Mimosa 8 (Saclay)

- Test in lab: 55Fe results

- Pixel noise ~ 15 e-

- CDS ending each column

- ⇒ Pixel-to-pixel dispersion ~ 8 e-

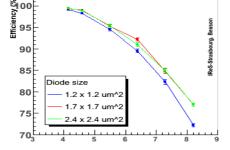

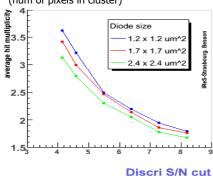

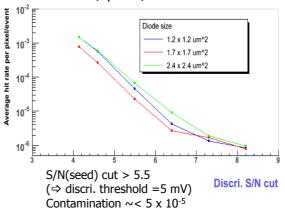

- Test beam results (DESY, 5GeV e-)

- S/N (MPV) ~ 8.5 9.5

- Efficiency > 98%

- TSMC 0.25  $\mu$ m fab. process with ~ 8  $\mu$ m epitaxial layer

- Pixel pitch: 25 μm

- 3 sub matrices with 3 diode size: 1.2 x 1.2  $\mu$ m<sup>2</sup>, 1.7 x 1.7  $\mu$ m<sup>2</sup>, 2.4 x 2.4  $\mu$ m<sup>2</sup>

- 24 // columns of 128 pixels with 1 discriminator per column

Discri. S/N cut

### Average hit multiplicity

(num of pixels in cluster)

# **Column comparator**

Temp. =

$$20^{\circ}$$

C; r.o. =  $40 \text{ MHz}$

Fake Hit rate / pixel / event

SNIC 2006

12

# In-pixel digitisation

- OPIC (On-Pixel Intelligent CMOS Sensor).

Designed by RAL within UK MI3 consortium

- In-pixel ADC (single-slope 8-bit)

- In-pixel TDC

- · Data sparsification

Test structure. 3 arrays of 64x72 pixels @ 30  $\mu$ m pitch Fabricated in TSMC 0.25/8 PMOS in pixel  $\rightarrow$  sub-100% efficiency Starting point for R&D on ILC-ECAL Calice

Image obtained with the sensor working in TDC mode with sparse data scan. White pixels are those

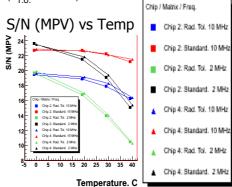

### MAPS for STAR

MimoSTAR-2 (France)

- AMS 0.35 µm OPTO. 30 µm pitch

- 2 matrices 64 x 128, JTAG architecture

- Rad. hard structure (based on Mimosa 11)

To be installed in STAR (2006)

⇒ Ionising radiation tolerant pixel validated at temperature up to + 40 °C

Temperature. C

⇒ No active cooling needed at int. time ~< O(1 ms)

MimoSTAR-3L in design in AMS 0.35: 200 kpixels,  $t_{r.o.}$  = 2 ms, 2 cm<sup>2</sup>

Efficiency vs Temp

\$\infty\text{Test-beam results} (DESY, 5 GeV e-)

\$\sigma\text{2 r.o. time (2 and 10 MHz)}

\$\infty\text{800 μs and 4 ms}\$

\$\infty\text{99.8.} \(

\begin{array}{c}

\text{100 kms} \\

\text{99.2 final f

### MAPS for ILC

Vertex: R&D in France (MIMOSA family) and UK (RAL\_HEPAPS family)

MIMOSA family: latest is n. 15. Several prototypes with different technologies and pixel architectures: 3T, column-parallel comparator, pipeline pixel. Good S/N, radiation hardness, spatial resolution, detection efficiency, ... demonstrated

RAL\_HEPAPS family: latest is n.4. First demonstrator (FAPS) of pipeline architecture. Fast, column-parallel ADC demonstrated within LCFI- CPCCD

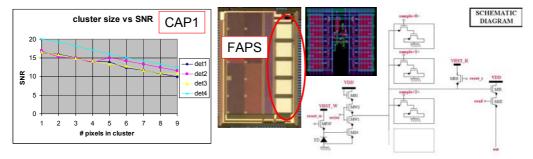

RAL\_HEPAPS 4: large format. 3 versions, each with 1026x384 pixels (0.4M pixel), 15  $\mu$ m pitch, 3T pixel. D1: single diode, enclosed geometry transistors. D2: double-diode.

D4: four-diode

ENC <~ 15 e- rms (reset-less)

5 MHz line rate Rad-hard: > Mrad

ECAL Calice): R&D just starting in the UK for large area, digital MAPS

SNIC 2006

1

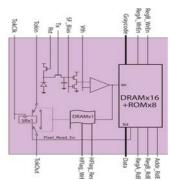

# Large area sensors

Stitched sensors likely to be needed for ILC: Vertex and ECAL (Calice)

Reticle. Size limited to ~ 2 cm. Reticle is stepped-and repeated → gaps between reticles

**CCD foundry.** Sometimes large chips are required → different programming of stepping to have no gap ⇔ 'stitching'

Driven by design of CMOS sensors as replacement of 35 mm film. At a few foundries, it is now possible to design stitched (seamless) sensors → 'wafer-scale'

Foundry choice rapidly widening

### **Conclusions**

CMOS MAPS first proposed as detectors for particle physics in 1999

100% efficiency detection demonstrated in 2000

Since then, good performance in terms of S/N, detection efficiency, radiation hardness, spatial resolution demonstrated with 3T

New sensors architecture developed: pipeline pixels, digital sensors, digital pixels

R&D for MAPS at Belle and STAR well underway. They could be the first experiments to have a MAPS-based vertex detector

Development at ILC in progress for both Vertex and ECAL. They are likely to need stitched sensors

SNIC 2006

18

# Acknowledgements

- M. Barbero and G. Verner, Haiwaii, for CAP and Belle

- W. Dulinski, Strasbourg, and N. Fourches, Saclay, for MIMOSA

N. Allinson + MI3 collaboration A. Fant

J. Crooks A. Clark

P. Gasiorek

N. Guerrini

T. Anaxagoras R. Halsall

M. Key-Charriere

M. Prydderch

S. Martin

M. French

G. Villani

M. Tyndel

P. Allport

G. Casse A. Evans

D. Prior

J. Velthuis

P. Dauncey N. Watson

+ ... all the others I forgot to mention!