# The Level-1 Trigger of the CMS experiment at the LHC and the Super-LHC

Andrew W. Rose

High Energy Physics Blackett Laboratory Imperial College London

A thesis submitted for the degree of Doctor of Philosophy of the University of London and the Diploma of Imperial College

#### **Abstract**

The Compact Muon Solenoid experiment at the Large Hadron Collider at CERN observes proton-proton collisions at a centre of mass energy of 14 TeV and a frequency of 40 MHz. This results in a raw data rate exceeding 40 PByte per second, which must be reduced to a rate of 100 MByte per second before storage. This is achieved in two stages, a hardware trigger (Level-1 Trigger) and a software trigger (Higher Level Trigger).

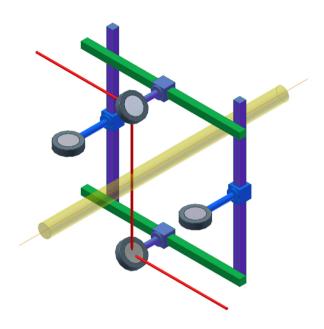

The Global Calorimeter Trigger is a central component in the Level-1 Trigger, selecting interesting 'physical' events from the background of events by identifying patterns of calorimetric energy patterns and features. The development of the Global Calorimeter Trigger required the use of several modern telecommunication technologies and is discussed here, with particular emphasis on the design and testing of the Source Card.

Although the Large Hadron Collider has yet to start operation, design of an upgraded accelerator (called the Super Large Hadron Collider) is already under way. This upgrade will improve on the design luminosity of the LHC by a factor of 10, increasing the number of collisions per bunch crossing by the same factor. Such an increase would require changes to both the algorithms and the architecture of the Level-1 trigger, in particular requiring the inclusion of tracking information. Investigations into several aspects of trigger upgrades, in particular tracking triggers, are included here with a case study into the identification of electrons in high pile-up environments.

#### Acknowledgements

This thesis would not have been possible without the time, thoughts, help and advice of many different people.

In particular, my thanks go to...

Costas, my supervisor, for all the help and guidance he has provided over the last few years and for introducing me to High Energy Physics in the first place. John Jones, for the enormous amount of time, advice and education given when learning to use FPGAs, VHDL, USB, the IDAQ and everything else. Gregory Iles, Magnus Hansen, Matt Stettler and Matt Noy, their advice, firmware and hardware experience were invaluable! Alex Tapper, Rob Frazier and Jim Brooke, again, their experience with all things software was invaluable! Mark Raymond for his ability to listen to any problem and draw a circuit diagram that will solve it. Sarah Greenwood, Maria Khaleeq, Vera Kasey, Dave Price and 'Oz' in the electronic workshop for their help and advice, and having the patience to make all the various fiddly hardware modifications! Jan Troska for his help testing the Source Card optical links. Pam Klabbers, for her help in the RCT to Source Card integration tests. Geoff Hall, Anders Ryd, Harry Cheung, Mark Pesaresi, Laura Fields and everyone else working on the tracker upgrade. Jamie Ballin and Adam Dobbs for always being free to discuss a problem, an idea, CMS software or anything else over a cup of coffee. Dave Lee, for letting me stick my nose in and design the FETS laser-wire readout board and for also being ready with a cup of coffee. Everyone else at Imperial who had an answer when I needed it.

And final my thanks to Bekka and to my family for all their support, both emotional and physical, over the last four years, but especially for those occasions when I was too tired, busy or stressed to notice it at the time.

Again, to you all, my deepest thanks,

A.R.

## **Contents**

| Abs        | tract    |                                        | 1  |  |  |

|------------|----------|----------------------------------------|----|--|--|

| Ack        | nowled   | lgements                               | 2  |  |  |

| Con        | Contents |                                        |    |  |  |

| List       | of Figu  | ires                                   | 8  |  |  |

| List       | of Tab   | les                                    | 15 |  |  |

| Chapter 1. |          | Introduction                           | 16 |  |  |

| 1.1        | The St   | andard Model of Particle Physics       | 17 |  |  |

|            | 1.1.1    | The Standard Model Lagrangian          | 18 |  |  |

|            | 1.1.2    | Searches for the Higgs Boson           | 25 |  |  |

|            | 1.1.3    | Objections to the standard model       | 27 |  |  |

| 1.2        | The La   | arge Hadron Collider (LHC)             | 31 |  |  |

| 1.3        | The C    | ompact Muon Solenoid (CMS)             | 36 |  |  |

|            | 1.3.1    | The Silicon Tracker                    | 36 |  |  |

|            | 1.3.2    | The Electromagnetic Calorimeter (ECAL) | 39 |  |  |

|            | 1.3.3    | The Hadronic Calorimeter (HCAL)        | 40 |  |  |

|            |          |                                        |    |  |  |

| 0.0 | Conte   | nts                                                 | 4  |

|-----|---------|-----------------------------------------------------|----|

|     | 1.3.4   | The Muon Detectors                                  | 40 |

|     | 1.3.5   | The CMS Trigger System                              | 41 |

|     | 1.3.6   | The CMS Level-1 Trigger                             | 43 |

|     | 1.3.7   | The CMS Level-1 Trigger Software                    | 44 |

| Cha | pter 2. | The CMS Calorimeter Trigger System                  | 46 |

| 2.1 | The C   | alorimeter Trigger Algorithms                       | 48 |

|     | 2.1.1   | The Electromagnetic Candidate Algorithm             | 48 |

|     | 2.1.2   | The Jet Candidate Algorithm                         | 50 |

|     | 2.1.3   | Other calorimeter trigger tasks                     | 51 |

| 2.2 | The C   | alorimeter Trigger System                           | 53 |

|     | 2.2.1   | The Calorimeter Trigger-Primitive Generators (TPGs) | 53 |

|     | 2.2.2   | The Regional Calorimeter Trigger (RCT)              | 54 |

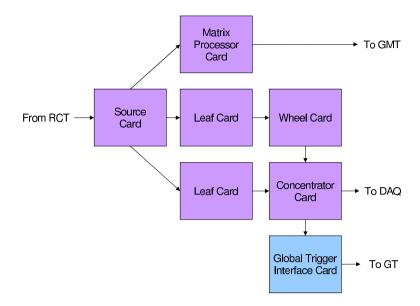

|     | 2.2.3   | The Global Calorimeter Trigger (GCT)                | 56 |

|     | 2.2.4   | The Global Trigger (GT)                             | 57 |

| 2.3 | Design  | n choices for the GCT                               | 59 |

| Cha | pter 3. | The Global Calorimeter Trigger Source Card          | 67 |

| 3.1 | The G   | CT Source Card                                      | 67 |

| 3.2 | Design  | n of the Source Card                                | 70 |

|     | 3.2.1   | Low level hardware design                           | 70 |

|     | 3.2.2   | Serial link design                                  | 71 |

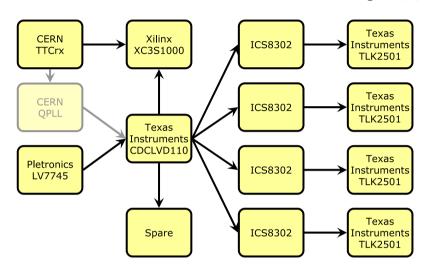

|     | 3.2.3   | Clock system design                                 | 72 |

|     | 3.2.4   | Power system design                                 | 74 |

|     | 3.2.5   | USB interface                                       | 76 |

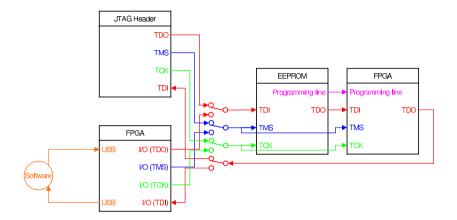

|     | 3.2.6   | JTAG interface                                      | 77 |

| 0.0 | Conte   | nts                                                         | 5   |

|-----|---------|-------------------------------------------------------------|-----|

|     | 3.2.7   | The Source Card Firmware Design                             | 79  |

|     | 3.2.8   | The Source Card Front Panel Design                          | 82  |

| 3.3 | Stand-  | -alone Testing of the GCT Source Cards                      | 82  |

|     | 3.3.1   | Bit Error Rate (BER) Tests and Poisson Statistics           | 84  |

|     | 3.3.2   | Cable testing                                               | 85  |

|     | 3.3.3   | Source Card ECL front end                                   | 87  |

|     | 3.3.4   | Optical Link Tests                                          | 91  |

|     | 3.3.5   | TTCrx and QPLL tests                                        | 98  |

| 3.4 | Integr  | ation of the GCT Source Cards                               | 101 |

|     | 3.4.1   | Integration of the GCT Source Cards with the RCT            | 101 |

|     | 3.4.2   | Integration of the GCT Source Cards with the GCT Leaf Cards | 104 |

| Cha | pter 4. | The Global Calorimeter Trigger Schema                       | 107 |

| 4.1 | Data-I  | Flow Architecture                                           | 107 |

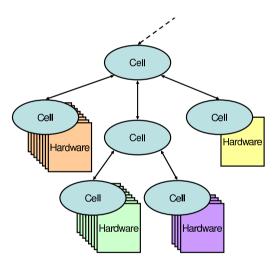

| 4.2 | Contro  | ol Architecture                                             | 115 |

|     | 4.2.1   | USB Architecture                                            | 115 |

|     | 4.2.2   | TTC Architecture                                            | 120 |

| Cha | pter 5. | The Global Calorimeter Trigger Software                     | 121 |

| 5.1 | Softwa  | are Architecture                                            | 121 |

|     | 5.1.1   | Software Structure                                          | 121 |

|     | 5.1.2   | The Trigger Supervisor                                      | 126 |

|     | 5.1.3   | Source Card Capture-file Interface                          | 130 |

| 0.0 | Conte                                             | ents                                                  | 6   |

|-----|---------------------------------------------------|-------------------------------------------------------|-----|

| Cha | pter 6.                                           | The Super-LHC, Super-CMS and the Level-1 Trigger      | 134 |

| 6.1 | Repla                                             | cement of the Regional Calorimeter Trigger            | 136 |

| 6.2 | Calor                                             | imeter-seeded tracker readout                         | 142 |

| 6.3 | A Self                                            | f-contained Tracking Trigger for CMS at the SLHC      | 149 |

|     | 6.3.1                                             | Reducing the tracker data volume                      | 150 |

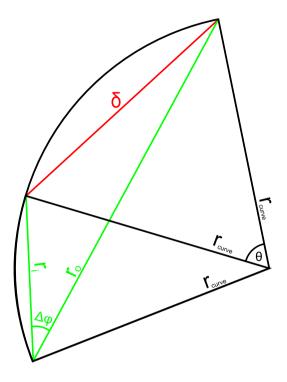

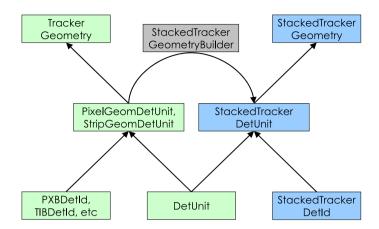

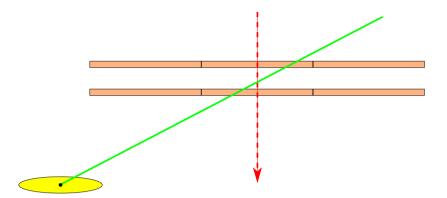

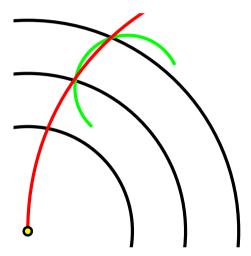

|     | 6.3.2                                             | The theoretical basis of the stacked tracking concept | 154 |

| Cha | pter 7.                                           | A Monte-Carlo study of Tracking Triggers              | 161 |

| 7.1 | Introd                                            | luction                                               | 161 |

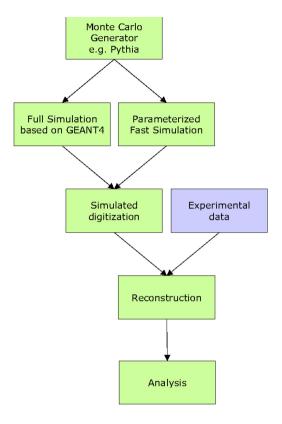

|     | 7.1.1                                             | CMSSW                                                 | 161 |

| 7.2 | Valida                                            | ation of "Fast" Simulation against "Full" Simulation  | 164 |

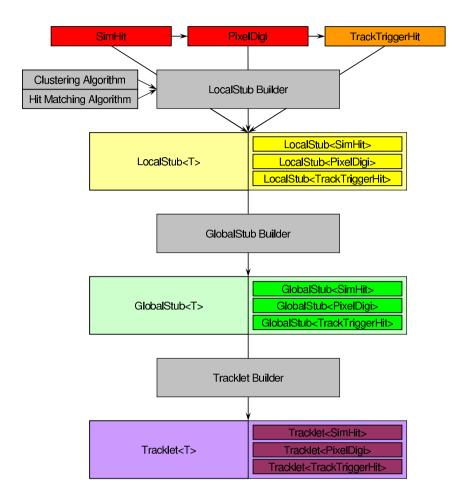

| 7.3 | A framework for the study of Tracking Triggers 16 |                                                       |     |

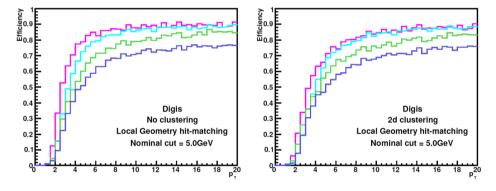

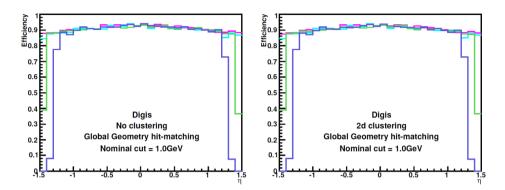

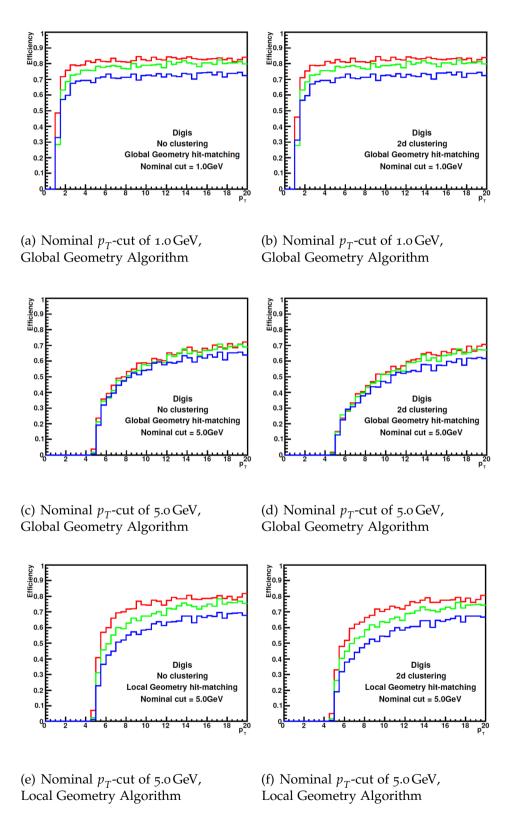

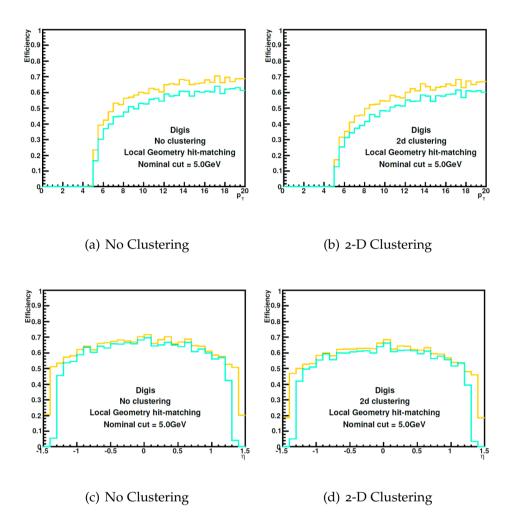

|     | 7.3.1                                             | Clustering algorithms                                 | 173 |

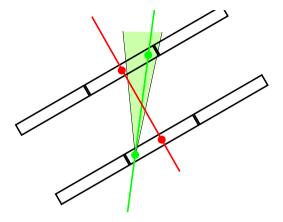

|     | 7.3.2                                             | Hit-matching algorithms                               | 175 |

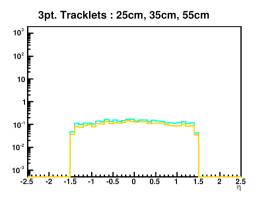

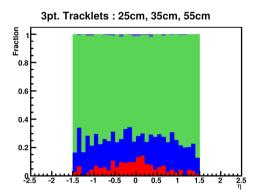

|     | 7.3.3                                             | Tracklets                                             | 179 |

| 7.4 | Initial                                           | Studies with Tracking Triggers                        | 179 |

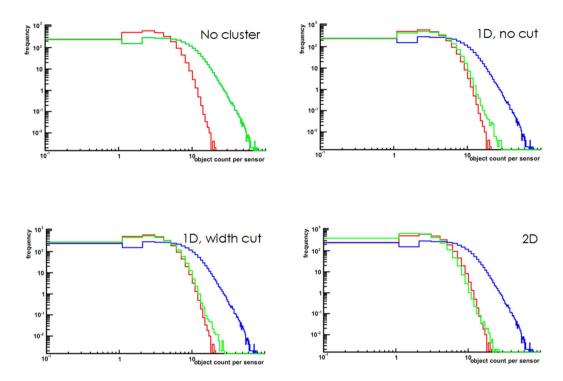

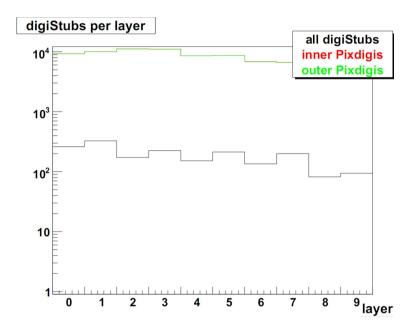

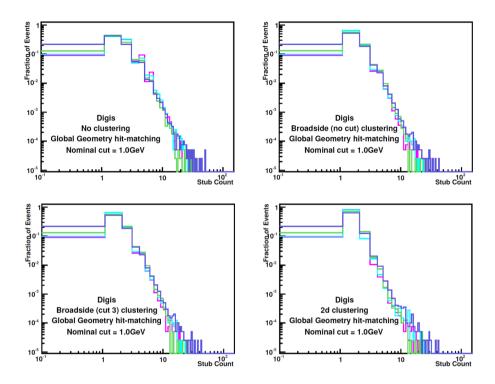

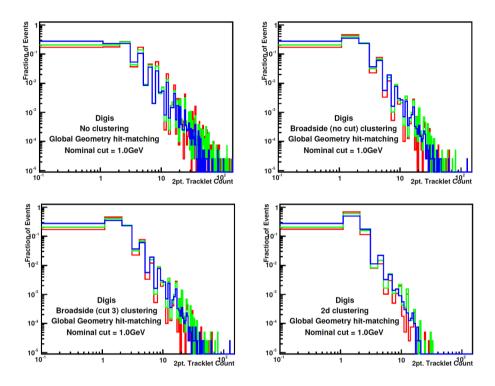

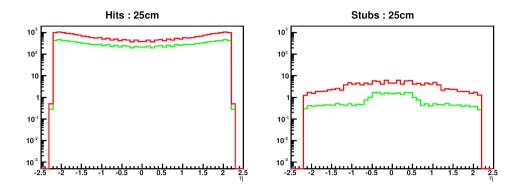

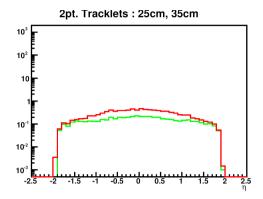

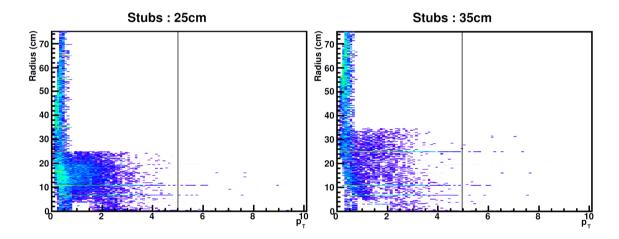

|     | 7.4.1                                             | Multiplicities                                        | 182 |

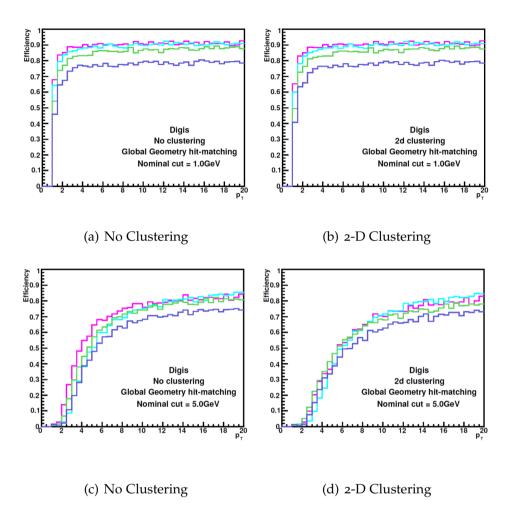

|     | 7.4.2                                             | Efficiencies                                          | 184 |

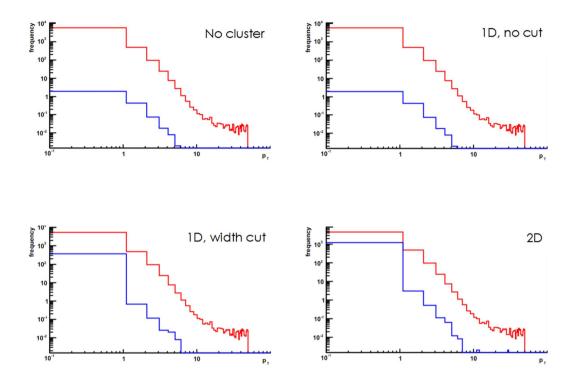

|     | 7.4.3                                             | Rates                                                 | 189 |

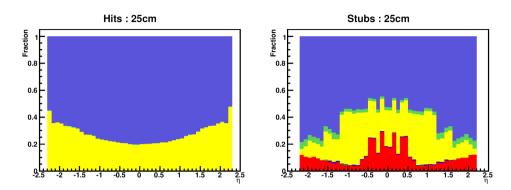

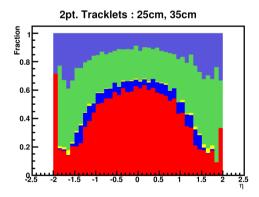

|     | 7.4.4                                             | Purities                                              | 191 |

|     | 7.4.5                                             | Incorrect reconstruction of secondary tracks          | 194 |

|     | 7.4.6                                             | Removing the vertex constraint                        | 195 |

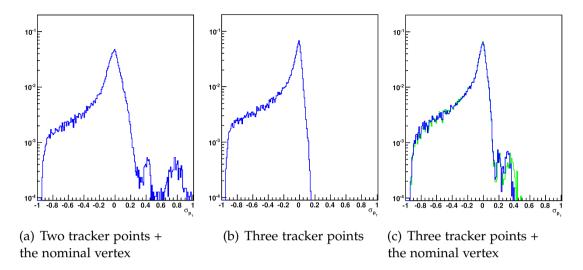

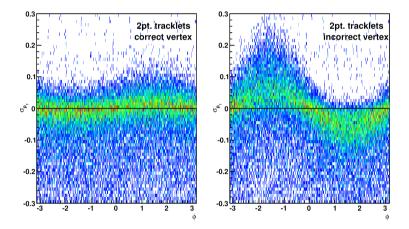

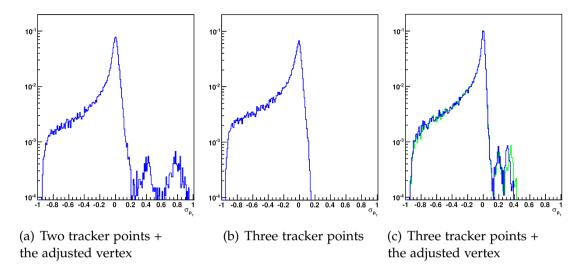

|     | 7.4.7                                             | $p_T$ -resolutions                                    | 197 |

|     | 7.4.8                                             | Vertex reconstruction                                 | 204 |

| 7.5 | Sumn                                              | nary                                                  | 207 |

| 0.0 | Conte   | nts                                     | 7   |

|-----|---------|-----------------------------------------|-----|

| Cha | pter 8. | A Super-LHC Electron Trigger            | 209 |

| 8.1 | Two Le  | evel-1 Electron Trigger Philosophies    | 210 |

| 8.2 | The "I  | nside-Out" Electron Trigger             | 212 |

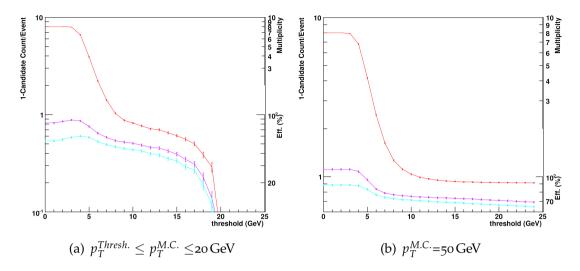

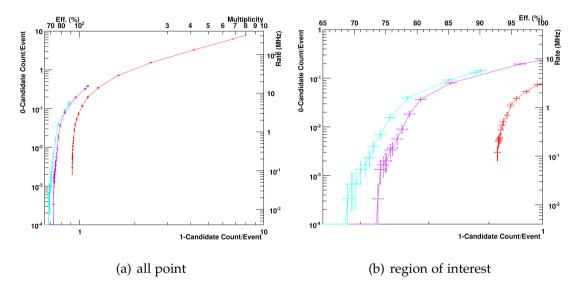

|     | 8.2.1   | Preparatory study                       | 212 |

|     | 8.2.2   | Background Rates                        | 215 |

|     | 8.2.3   | Efficiency                              | 216 |

|     | 8.2.4   | Balancing efficiency and rate reduction | 218 |

| 8.3 | Summ    | ary                                     | 219 |

| Cha | pter 9. | Conclusions                             | 220 |

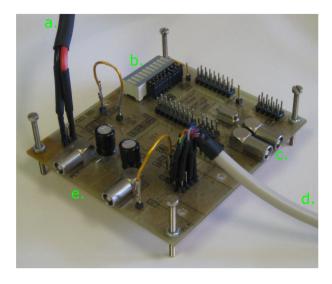

| App | endix A | A. The Front End Test Stand laser-wire  | 223 |

| A.1 | The Fr  | ont End Test Stand (FETS)               | 225 |

| A.2 | A read  | lout system for the FETS laser-wire     | 227 |

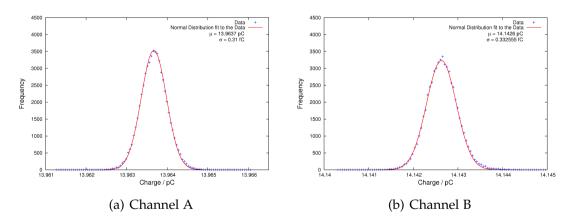

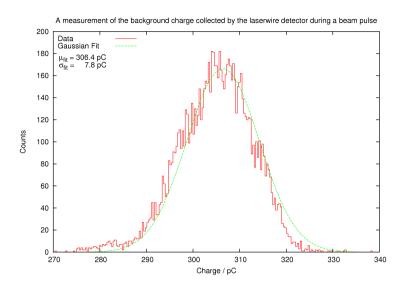

| A.3 | Tests o | of the FETS laser-wire readout system   | 228 |

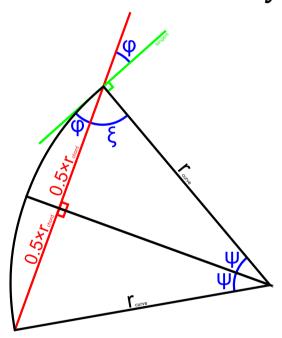

| App | endix I | 3. Circular Geometry                    | 232 |

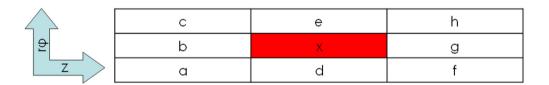

| App | endix ( | C. 2-D Clustering Algorithm             | 233 |

| Glo | ssary   |                                         | 234 |

| Ref | erences |                                         | 239 |

## **List of Figures**

| 1.1  | Feynman diagrams of the trilinear and quadrilinear couplings of the standard model gauge bosons                             | 19 |

|------|-----------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Results of W-pair production by the Aleph experiment at LEP                                                                 | 20 |

| 1.3  | Feynman diagram of the coupling between fermions and gauge-bosons in the standard model                                     | 21 |

| 1.4  | Feynman diagrams of the $F_{\mu}F^{\mu}h$ and $F_{\mu}F^{\mu}hh$ vertices                                                   | 22 |

| 1.5  | Theoretical bounds on the mass of the Higgs boson                                                                           | 26 |

| 1.6  | Latest results of searches for the Higgs boson                                                                              | 27 |

| 1.7  | Feynman diagrams for the three sources of ultraviolet divergences in the standard model                                     | 28 |

| 1.8  | Feynman diagrams for the process $WW \rightarrow X \rightarrow WW$                                                          | 28 |

| 1.9  | Higgs production channels at the LHC                                                                                        | 32 |

| 1.10 | Higgs decay modes in the mass range accessible at the LHC                                                                   | 33 |

| 1.11 | The production cross-sections of a selection of possible production modes at the LHC as a function of interaction energy    | 34 |

| 1.12 | A comparison of H $\to \gamma \gamma$ signal and background for a Higgs mass of 130 GeV and 100 fb $^{-1}$ of data recorded | 35 |

| 1.13 | Diagram of the CMS Detector                                                                                                 | 37 |

| 1.14 | Layout of a quarter of the CMS tracking detector                                                                            | 38 |

| 0.0  | List of Figures                                                                       | 9  |

|------|---------------------------------------------------------------------------------------|----|

| 1.15 | The CMS Trigger and Data Acquisition System                                           | 41 |

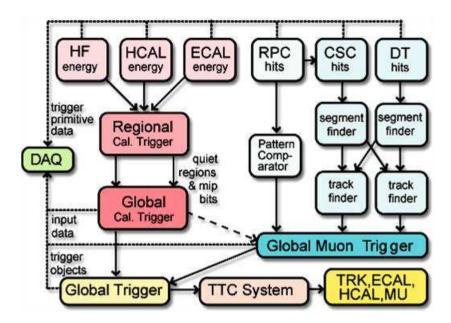

| 1.16 | The CMS level-1 trigger                                                               | 43 |

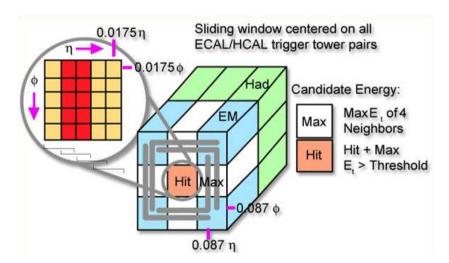

| 2.1  | The calorimeter trigger $e/\gamma$ algorithm                                          | 49 |

| 2.2  | The calorimeter trigger jet algorithm                                                 | 51 |

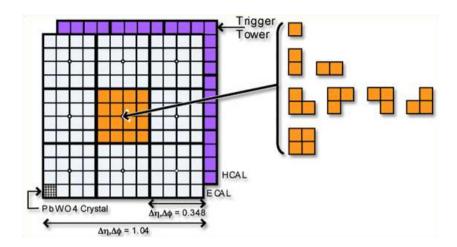

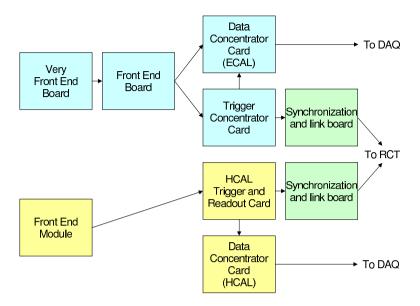

| 2.3  | The calorimeter TPG and DAQ architecture                                              | 55 |

| 2.4  | The RCT architecture                                                                  | 56 |

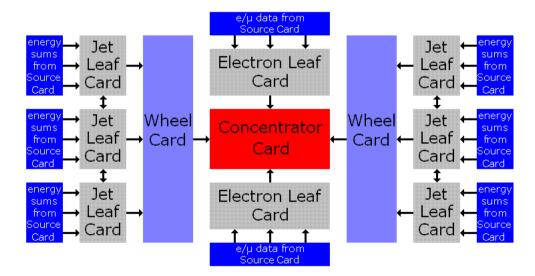

| 2.5  | The GCT architecture                                                                  | 57 |

| 2.6  | The GT architecture                                                                   | 58 |

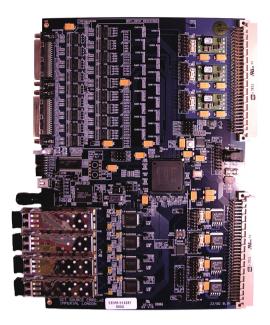

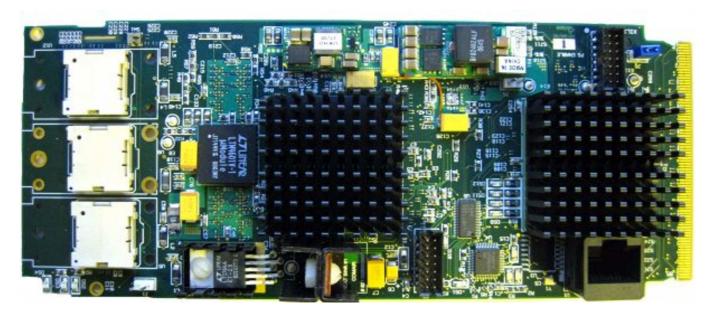

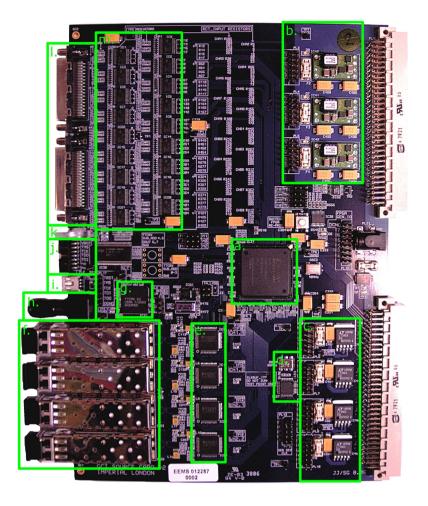

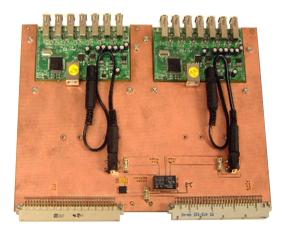

| 2.7  | The GCT source card                                                                   | 61 |

| 2.8  | The GCT architecture                                                                  | 61 |

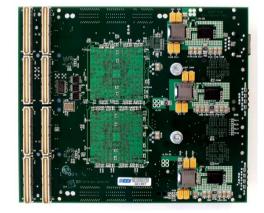

| 2.9  | The GCT leaf card                                                                     | 62 |

| 2.10 | The GCT concentrator card                                                             | 63 |

| 2.11 | The GCT wheel card                                                                    | 64 |

| 2.12 | The GCT matrix processor Card                                                         | 66 |

| 3.1  | Block Diagram of the CMS GCT source card                                              | 70 |

| 3.2  | Key features of the CMS GCT source card                                               | 72 |

| 3.3  | The source card clock system                                                          | 73 |

| 3.4  | The source card JTAG chain                                                            | 78 |

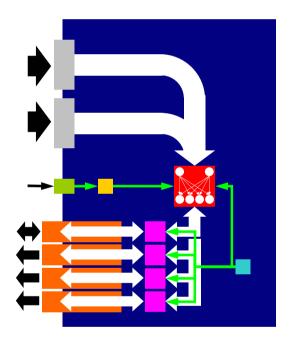

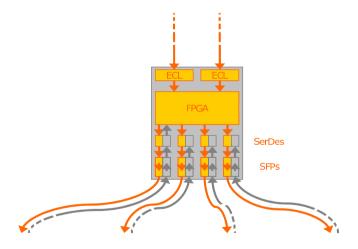

| 3.5  | Schematic of data flow through the CMS GCT source card                                | 83 |

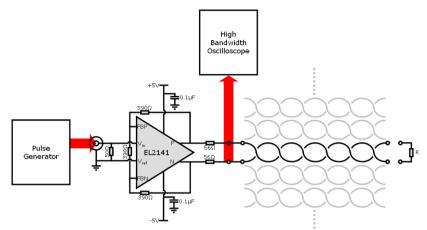

| 3.6  | The RCT-GCT cable testing apparatus                                                   | 86 |

| 3.7  | The RCT Emulator card                                                                 | 88 |

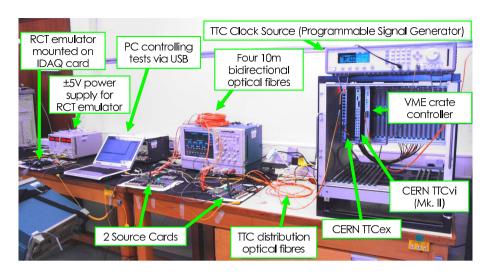

| 3.8  | Photograph of the experimental set-up used in the testing of the CMS GCT source cards | 89 |

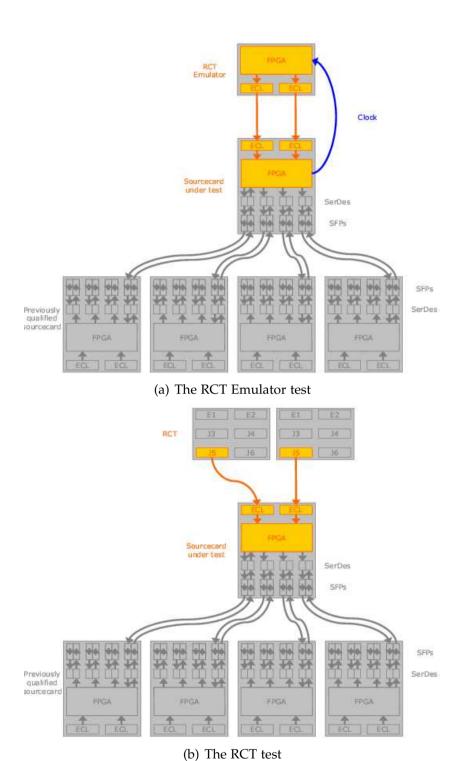

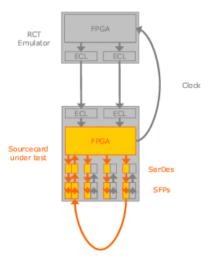

| 3.9  | Schematic layout of the two tests of the source card ECL inputs                       | 90 |

| 0.0  | List of Figures                                                                                                         | 10   |

|------|-------------------------------------------------------------------------------------------------------------------------|------|

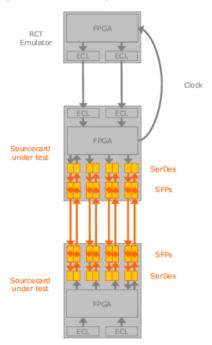

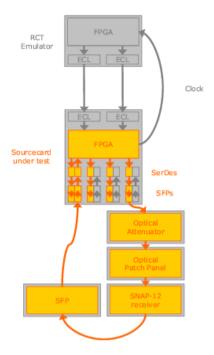

| 3.10 | Schematic layout of the initial tests of the source card optical links                                                  | 92   |

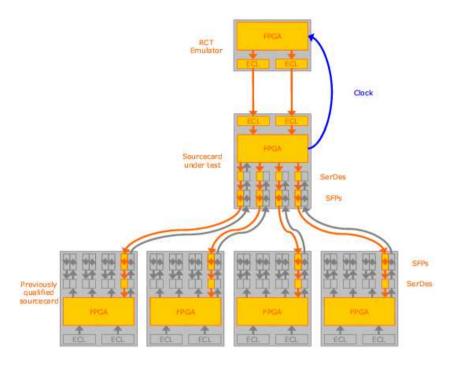

| 3.11 | Schematic layout of the two physical tests of the source card optical links                                             | 94   |

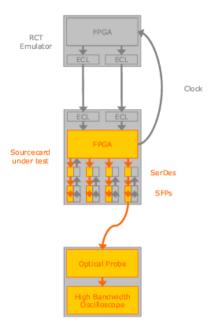

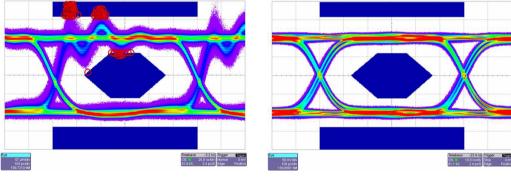

| 3.12 | Eye diagrams resulting from the first two tests of the source card optical links                                        | 95   |

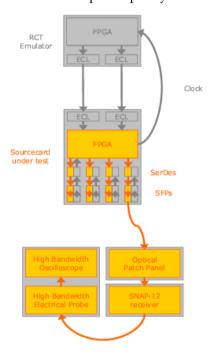

| 3.13 | Schematic layout of the indirect test of the source card optical links                                                  | 96   |

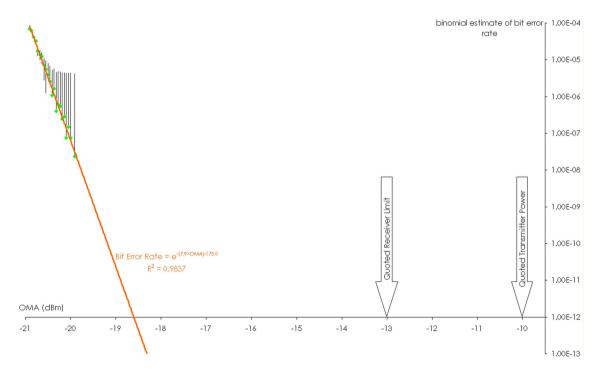

| 3.14 | Extrapolated BER as a function of fibre attenuations on the optical links                                               | s 97 |

| 3.15 | Test configuration used for the production testing of the optical links                                                 | 99   |

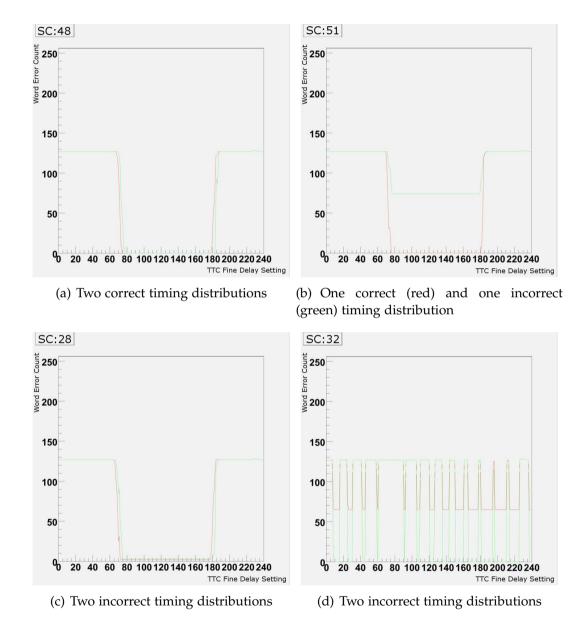

| 3.16 | Four plots of word error rate against the TTCrx fine-delay setting made during the RCT-source card integration tests    | 103  |

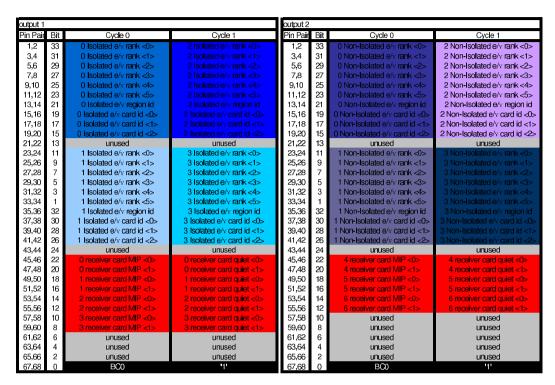

| 4.1  | The bit structure of the six RCT outputs                                                                                | 110  |

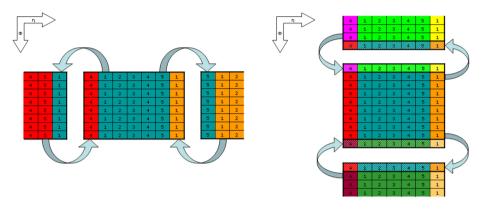

| 4.2  | The chosen routing scheme for electron and muon data                                                                    | 111  |

| 4.3  | The chosen routing scheme for the RCT regional data for regions far from the $\eta=0$ boundary                          | 112  |

| 4.4  | The chosen routing scheme for the RCT regional data for regions near to the $\eta=0$ boundary                           | 113  |

| 4.5  | The prototype (V2) USB-hub carrier card for the GCT source card system                                                  | 116  |

| 4.6  | The monitor panel for the GCT source card system                                                                        | 118  |

| 4.7  | Schematic of the GCT source card USB control system                                                                     | 119  |

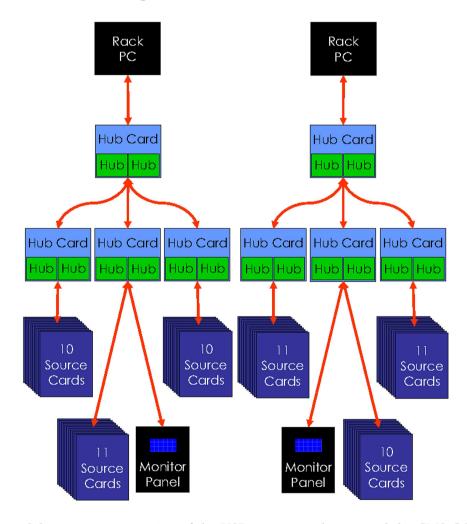

| 5.1  | The source card software structure                                                                                      | 122  |

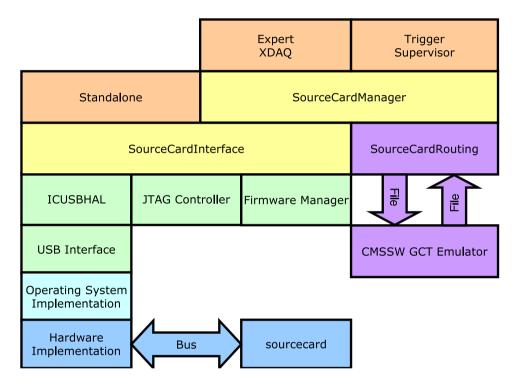

| 5.2  | The trigger supervisor structure                                                                                        | 127  |

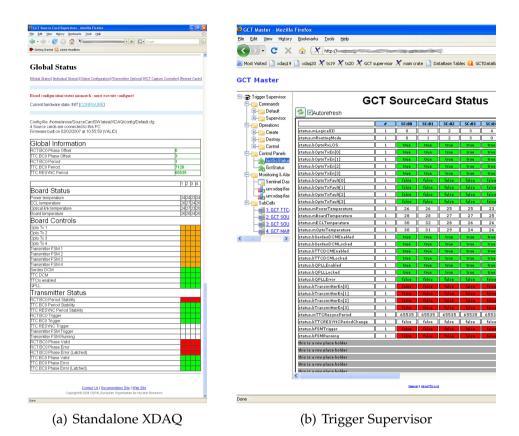

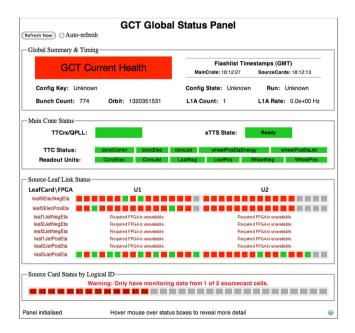

| 5.3  | Screen shots of the XDAQ and Trigger Supervisor "at-a-glance" source card summary tables                                | 131  |

| 5.4  | Screen shots of the trigger supervisor master panel                                                                     | 131  |

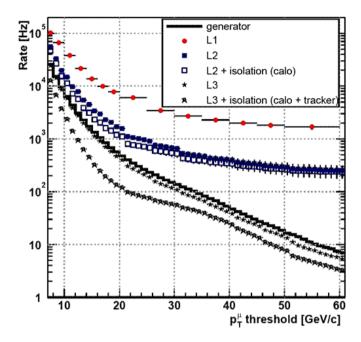

| 6.1  | Single muon trigger rates for CMS at the LHC as a function of $p_T$ threshold for the level-1 and higher level triggers | 136  |

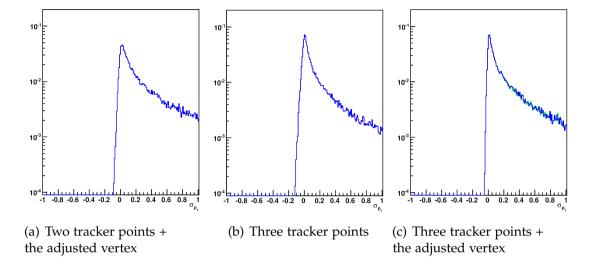

| 7·25 | Simulated $p_T$ -resolution calculated using two tracker points + the nominal vertex, three tracker points and three tracker points + the nominal vertex                                                | 200 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.26 | Simulated $p_T$ -resolution vs. track direction in $\phi$ for 2-point tracklets with the nominal vertex set at x=400 $\mu$ m and x=0 $\mu$ m                                                            | 201 |

| 7.27 | Simulated $p_T$ -resolution calculated using two tracker points + the adjusted vertex, three tracker points and three tracker points + the adjusted vertex and using three different fitting techniques | 202 |

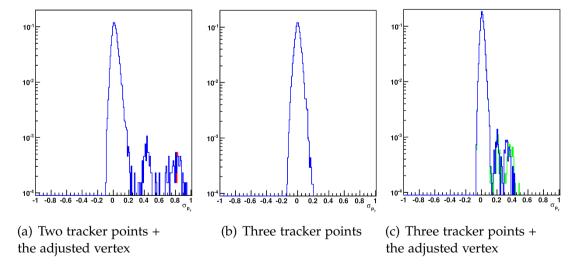

| 7.28 | Simulated $p_T$ -resolution calculated using two tracker points + the adjusted vertex, three tracker points and three tracker points + the adjusted vertex and using three different fitting techniques | 203 |

| 7.29 | Simulated $p_T$ -resolution calculated using two tracker points + the adjusted vertex, three tracker points and three tracker points + the adjusted vertex and using three different fitting techniques | 203 |

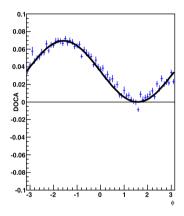

| 7.30 | Simulated estimates of the distance of closest approach calculated using three-point tracklets plotted against the $\phi$ -position of the inner stub                                                   | 205 |

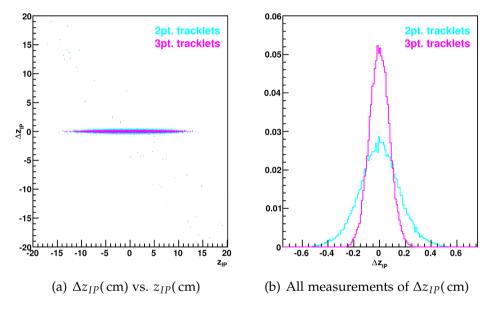

| 7.31 | Simulated resolution of the calculated z-position of the interaction point for both two- and three-point tracklets                                                                                      | 206 |

| 8.1  | The HLT e/ $\gamma$ algorithm                                                                                                                                                                           | 210 |

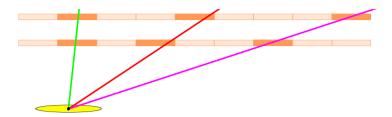

| 8.2  | Two electron trigger philosophies: "outside-in" and "inside-out"                                                                                                                                        | 211 |

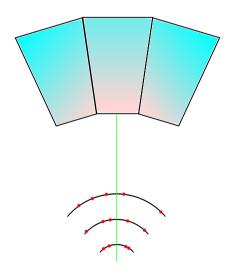

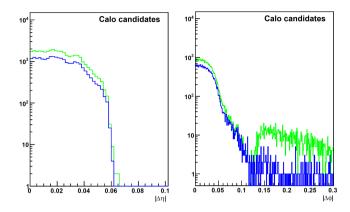

| 8.3  | Simulated resolution with which two- and three-point tracklets can identify the location that tracks hit the calorimeter in the $\phi$ -direction                                                       | 214 |

| 8.4  | Resolution with which two- and three-point tracklets can identify the location that tracks hit the calorimeter in the $\eta$ -direction                                                                 | 215 |

| 8.5  | Resolution with which upgraded level-1 e/ $\gamma$ candidates can identify the location that tracks hit the calorimeter in the $\eta$ - and $\phi$ - directions                                         | 216 |

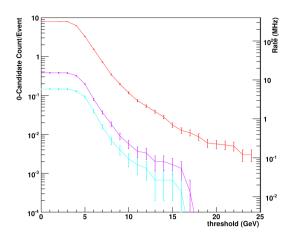

| 8.6  | Mean rate of calorimeter candidates, two-point+calorimeter candidates and three-point+calorimeter candidates as a function of applied $E_T$ and $p_T$ threshold for background events                   | 217 |

## **List of Tables**

| 5.1 | Field Structure of the source card capture file                                                                              | 130 |

|-----|------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.1 | Estimation of the number of logic devices required for an upgraded calorimeter trigger based on bandwidth requirements alone | 141 |

| 5.2 | Distribution of the distance of tracker hits from a calorimeter seed point in the $\phi$ -direction                          | 145 |

| 5.3 | Distribution of the distance of tracker hits from a calorimeter seed point in the <i>z</i> -direction                        | 146 |

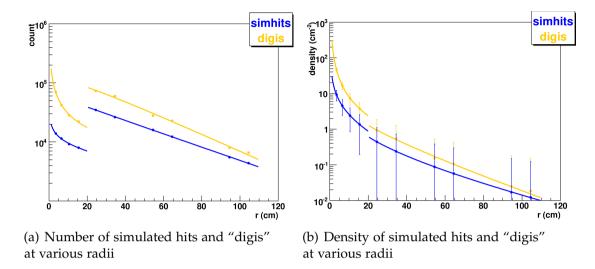

| 7.1 | Comparison of the densities of simulated and digitized tracker hits predicted by the "full" and "fast" simulation            | 165 |

| 7.2 | Simulated estimates of stub multiplicities by layer, clustering algorithm and hit-matching algorithm                         | 183 |

| 7.3 | Simulated estimates of tracklet multiplicities by layer, clustering algorithm and hit-matching algorithm                     | 185 |

| 7·4 | Computational complexity of four methods of measuring $r_{curve}$                                                            | 199 |

| 3.1 | The chosen window sizes in $\eta$ and $\phi$ for the association of tracker candidates with calorimeter candidates           | 216 |

1 Introduction 16

## Chapter 1

### Introduction

"In the attitude of silence the soul finds the path in a clearer light, and what is elusive and deceptive resolves itself into crystal clearness.

Our life is a long and arduous quest after Truth."

- Mahatma Gandhi (1869 - 1948)

The search for a coherent description of the universe in which we live has been a constant feature throughout mankind's history, from the five classical 'elements' [1] of antiquity, through the middle ages with the formation of the scientific method in the Middle East [2] and through the scientific revolution of the 17th and 18th centuries. In modern times, the emphasis in fundamental physics has been on the unification of seemingly disparate aspects of nature into a single framework, starting with Maxwell's unified description of the electric and magnetic fields and culminating in the Standard Model of Particle Physics [3, 4, 5, 6, 7, 8].

Each generation of physicists has brought about advancement and understanding but, with each step taken, the bar is raised for future generations so that new discovery and insight requires more precise measurements, more complicated mathematical descriptions and the need to study nature on ever more extreme scales. The rare and fleeting nature of the particles currently being sought requires the current generation of experiments in particle physics to look for ever

smaller, but significant, features in an ever larger background of less significant events. In addition the accumulation and process of data needs to be at ever higher speed. This requirement for speed necessitates the use of dedicated processing hardware rather than software algorithms. These studies considers the hardware used for this purpose and how the lessons learned can be applied to future experiments in particle physics.

#### 1.1 The Standard Model of Particle Physics

The most detailed and fundamental model of nature is the Standard Model of Particle Physics. The model describes all matter as being composed of spin- $\frac{1}{2}$  particles whose interactions arise as a direct consequence of insisting upon local gauge invariance, a prerequisite [9] to making a quantum field theory renormalizable and thus meaningful. By insisting that the Lagrangian describing the spin-o and spin- $\frac{1}{2}$  fields is invariant under rotation in  $SU(3)_{colour}$ ,  $SU(2)_{isospin}$  and  $U(1)_{hypercharge}$  spaces, it is necessary to respectively introduce 8, 3 and 1 spin-1 gauge fields to account for all possible local variations in phase. These fields are observed as gluons, the  $W^{\pm}$  &  $Z^0$  bosons and the photon  $(\gamma)$ . Whilst the  $SU(3)_{colour}$  symmetry is thought to be exact, the  $SU(2)_{isospin} \times U(1)_{hypercharge}$  'electroweak' symmetry is said to be broken. Without symmetry breaking, the massless gauge bosons required by quantum field theory cannot be reconciled with the massive  $W^{\pm}$  and  $Z^0$  bosons seen in nature without breaking the gauge invariance of the theory. The simplest known mechanism for electroweak symmetry breaking is the Higgs mechanism.

Whilst it is legitimate to add terms on an ad hoc basis for the mass of the scalar particles to the Lagrangian, Nature's asymmetric treatment of left-handed and right-handed spinor states precludes a similar treatment of the spinor fields; instead, the fermion masses must be introduced by the Yukawa coupling of the Higgs field to the fermion field.

#### 1.1.1 The Standard Model Lagrangian

The Standard Model Lagrangian is constructed broadly of four terms, equation 1.1:

$$\mathcal{L}_{Standard\ Model} = \mathcal{L}_{Gauge\ Boson} + \mathcal{L}_{Fermion} + \mathcal{L}_{higgs\ Boson} + \mathcal{L}_{Yukawa\ Coupling} \tag{1.1}$$

with each term defined as follows

#### 1.1.1.1 $\mathcal{L}_{Gauge\ Boson}$

$$\mathcal{L}_{Gauge\ Boson} = -\frac{1}{4} B^{\mu\nu} B_{\mu\nu} - \frac{1}{4} W_a^{\mu\nu} W_{\mu\nu}^a - \frac{1}{4} G_a^{\mu\nu} G_{\mu\nu}^a$$

(1.2)

where

$$B_{\mu\nu} = \partial_{\mu}B_{\nu} - \partial_{\nu}B_{\mu} \tag{1.3}$$

$$W_{\mu\nu} = \partial_{\mu}W_{\nu}^{a} - \partial_{\nu}W_{\mu}^{a} + g_{2}f_{2}^{abc}W_{\nu}^{b}W_{\nu}^{c}$$

(1.4)

$$G_{\mu\nu} = \partial_{\mu}G_{\nu}^{a} - \partial_{\nu}G_{\mu}^{a} + g_{3}f_{3}^{abc}G_{\nu}^{b}G_{\nu}^{c}$$

(1.5)

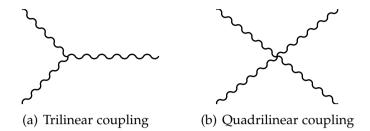

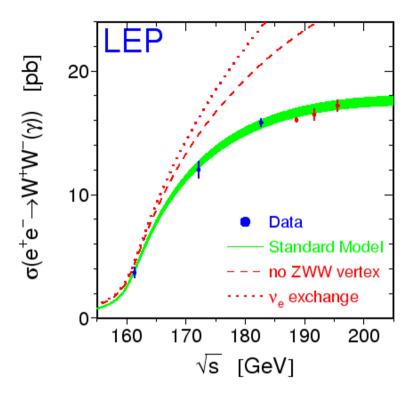

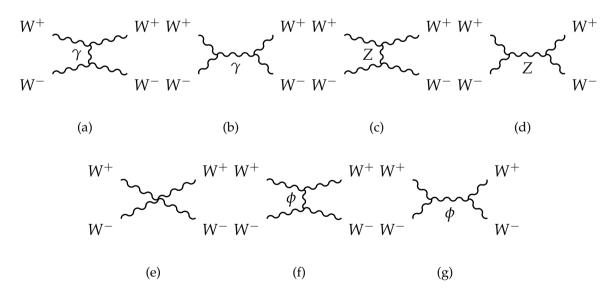

where  $B_{\mu}$ ,  $W_{\mu}$  and  $G_{\mu}$  are the  $U(1)_{hypercharge}$ ,  $SU(2)_{isospin}$  and  $SU(3)_{colour}$  gauge fields and  $f_3^{abc}$  are, respectively, the structure constants of the  $SU(2)_{isospin}$  and  $SU(3)_{colour}$  gauge group. For the field  $W_{\mu}$  the indices a, b, c run from 1 to 3 and for the field  $G_{\mu}$ , from 1 to 8, representing the 3 and 8 generators of the  $SU(2)_{isospin}$  and  $SU(3)_{colour}$  groups, respectively. The terms  $g_2f^{abc}W^b_{\mu}W^c_{\nu}$  and  $g_3f^{abc}G^b_{\mu}G^c_{\nu}$  must be included to maintain gauge invariance when taking into account the non-Abelian nature of the  $SU(2)_{isospin}$  and  $SU(3)_{colour}$  groups. Their inclusion creates Lagrangian terms which are cubic and quartic with respect to the field and which are not seen in the Abelian  $U(1)_{hypercharge}$  group. These terms manifest themselves as trilinear and quadrilinear couplings of the weak and strong gauge bosons, shown in figure 1.1. Such couplings were demonstrated by the Aleph experiment at LEP (Large Electron-Positron Collider) . Figure 1.2 is one of the clear indications that the standard model provides the most accurate description of the data.

**Figure 1.1:** Feynman diagrams of the trilinear and quadrilinear couplings introduced by the necessary inclusion of cubic and quartic terms in the Lagrangian of non-Abelian fields required to maintain gauge invariance. Here the lines may represent the photon & weak gauge bosons  $(\gamma/W^{\pm}/Z^{0})$ , or the strong gauge bosons, the gluons.

#### 1.1.1.2 L Fermion

$$\mathcal{L}_{Fermion} = \overline{Q}_i i \not \!\! D Q_i + \overline{u}_i i \not \!\! D u_i + \overline{d}_i i \not \!\! D d_i + \overline{L}_i i \not \!\! D L_i + \overline{e}_i i \not \!\! D e_i$$

(1.6)

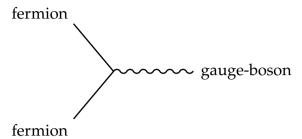

where Q and L respectively represent the left-handed Quark- and Lepton-  $SU(2)_{isospin}$ doublet and u, d and e represent the right-handed u-type quark, d-type quark and charged-lepton singlets and the index, i, runs from 1 to 3 representing the three generations.  $\mathbb{D}$  is the gauge covariant derivative,  $D_u$ , in Feynman slash notation,  $D = \gamma^{\mu}D_{\mu}$ . The gauge covariant derivative, rather than the standard derivative, is required to ensure gauge invariance under  $U(1)_{hypercharge}$ ,  $SU(2)_{isospin}$  and  $SU(3)_{colour}$  local gauge transformations. In field theories, a gauge covariant derivative of the form  $D_{\mu} = \partial_{\mu} - i\alpha F_{\mu}$  is necessary, and sufficient, to account for any arbitrary gauge transformations imposed upon the field on which the derivative is acting. The necessary inclusion of the vector field in making the derivative gauge covariant results in the introduction of terms describing field-field interactions. If we consider, for example, the Lagrangian term  $\overline{L}_i i \gamma^{\mu} D_{\mu} L_i$  and the  $SU(2)_{isospin}$  gauge covariant derivative,  $D_{\mu} = \partial_{\mu} - i \frac{g_2}{2} \sigma^a W_{\mu}^a$ , substituting the latter into the former results in a Lagrangian term of the form  $L_iW_{ii}^aL_i$  which can be seen to describe the interaction of a fermion with a gauge boson as shown in figure 1.3.

As it is now known that neutrinos have mass and thus a right handed state, an additional term of the form  $\overline{n}_i i \not \! D n_i$ , where n indicates the right-handed neutral-lepton singlet, must be included. It is also now known that the interactions of

**Figure 1.2:** Data taken by the Aleph experiment at LEP compared with three hypotheses: the standard model (solid), the standard model with no  $Z^0W^+W^-$  vertices (dashed) and the standard model with no trilinear vertices (dotted).

the three generations are not independent, but interact by the CKM (Cabibbo-Kobayashi-Maskawa) mechanism in the quark sector and PMNS (Pontecorvo-Maki-Nakagawa-Sakata) mechanism in the lepton sector. These interactions may be included by modification of the above expression, such that the terms  $\overline{Q}_i i \mathbb{D} Q_i$  and  $\overline{L}_i i \mathbb{D} L_i$  take the form  $\overline{Q}_i i \mathbb{D} Q_i$  and  $\overline{L}_i i \mathbb{D} Q_i$  where  $\overline{Q}_i i \mathbb{D} Q_i$  indicates the inclusion of the relevant mixing matrices into the  $SU(2)_{isospin}$  component of the gauge covariant derivative. No modifications are required to right-handed singlet terms as there is no  $SU(2)_{isospin}$  coupling to right-handed states.

#### 1.1.1.3 Lhiggs Boson

$$\mathcal{L}_{higgs \, Boson} = |D_{\mu}\{h+v\}_{2}|^{2} - \lambda |\{h+v\}_{2}|^{4} + \lambda v^{2}|\{h+v\}_{2}|^{2}$$

$$= |D_{\mu}\{h+v\}_{2}|^{2} - \frac{\lambda}{4} \cdot h^{4} - \lambda v \cdot h^{3} - \lambda v^{2} \cdot h^{2} + constant \quad (1.7)$$

**Figure 1.3:** An example of a fermion/gauge-boson vertex of the type arising from the use of the gauge covariant derivative, rather than the standard derivative, as is required to ensure gauge invariance under local gauge transformations.

where h is the Higgs field and v is the vacuum expectation value<sup>i</sup> of the field. The notation,  $\{h+v\}_2$ , is used to represent the  $SU(2)_{isospin}$  doublet,  $\begin{pmatrix} 0 \\ \frac{1}{\sqrt{2}} \left(h+v\right) \end{pmatrix}$ .

The  $h^4$  and  $h^3$  terms respectively represent quadrilinear and trilinear couplings of the Higgs field, analogous to those in figure 1.1, while the  $h^2$  term, represents a mass term. Direct comparison of equation 1.7 with the Klein-Gordon Lagrangian<sup>ii</sup> yields the identity:

$$mass_h = \sqrt{2\lambda} v \tag{1.8}$$

As before, the gauge covariant derivative, rather than the standard derivative, is required to ensure gauge invariance under  $U(1)_{hypercharge}$  and  $SU(2)_{isospin}$  local gauge transformations.

If the  $SU(2)_{isospin} \times U(1)_{hypercharge}$  gauge covariant derivative,  $D_{\mu} = \partial_{\mu} - i \frac{g_2}{2} \sigma^a W_{\mu}^a - i \frac{g_1}{2} B_{\mu}$  is considered, substitution into the first term of equation 1.7 may be seen to result in Lagrangian terms of the form:

$$\frac{1}{2}\partial^{\mu}h\partial_{\mu}h + \frac{g_{2}^{2}}{4}|W_{\mu}^{1} + iW_{\mu}^{2}|^{2}(h+v)^{2}

+ \frac{1}{8}|g_{1}B_{\mu} - g_{2}W_{\mu}^{3}|^{2}(h+v)^{2}

+ 0|g_{1}B_{\mu} + g_{2}W_{\mu}^{3}|^{2}(h+v)^{2}$$

(1.9)

which, upon identification of  $\frac{W_{\mu}^1 \mp i W_{\mu}^2}{\sqrt{2}}$ ,  $\frac{g_1 B_{\mu} - g_2 W_{\mu}^3}{\sqrt{g_1^2 + g_2^2}}$  and  $\frac{g_1 B_{\mu} + g_2 W_{\mu}^3}{\sqrt{g_1^2 + g_2^2}}$  as  $W_{\mu}^{\pm}$ ,  $Z_{\mu}^0$  and

<sup>&</sup>lt;sup>i</sup>also known as the condensate

$<sup>^{</sup>ii}\mathcal{L}_{Klein-Gordon}=\frac{1}{2}\partial_{\mu}\phi\,\partial^{\mu}\phi-\frac{1}{2}m_{\phi}^{2}\phi^{2}$  where  $\phi$  is a scalar field and  $m_{\phi}$  is the mass of the boson associated with that field.

$A_{\mu}$  (the photon) respectively, become:

$$\frac{1}{2}\partial^{\mu}h\partial_{\mu}h + \frac{g_{2}^{2}}{4}W_{\mu}^{+}W^{-\mu}\left(h^{2} + 2hv + v^{2}\right)

+ \frac{1}{8}\left(g_{1}^{2} + g_{2}^{2}\right)Z_{\mu}^{0}Z^{0\mu}\left(h^{2} + 2hv + v^{2}\right)

+ 0\left(g_{1}^{2} + g_{2}^{2}\right)A_{\mu}A^{\mu}\left(h^{2} + 2hv + v^{2}\right)$$

(1.10)

Further recognizing that the mass of a charged boson is given by a term of the form,  $mass_{F^{\pm}}^2F^+F^-$  and for an electrically neutral boson,  $\frac{1}{2}mass_{F^0}^2F^0F^0$ , the mass of the bosons may be expressed as:

$$mass_{W^{\pm}} = \frac{g_2 v}{2} \tag{1.11}$$

$$mass_{Z^0} = \frac{v}{2} \sqrt{g_1^2 + g_2^2}$$

(1.12)

$$mass_{A^0} = 0$$

(1.13)

and by comparison with equation 1.8 it is possible to redefine

$$\frac{g_2^2}{4} = 2\lambda \left(\frac{mass_{W^{\pm}}}{mass_h}\right)^2 \tag{1.14}$$

$$\frac{g_1^2 + g_2^2}{8} = \lambda \left(\frac{mass_{Z^0}}{mass_h}\right)^2$$

(1.15)

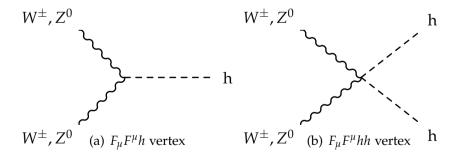

implying that the coupling strength of the gauge bosons to the Higgs boson is dependent on the ratio of the mass of the gauge boson to the mass of the Higgs boson. The vertices predicted by the theory are indicated in figure 1.4.

**Figure 1.4:** Feynman diagrams of the  $F_{\mu}F^{\mu}h$  and  $F_{\mu}F^{\mu}hh$  vertices introduced by the necessary use of the gauge covariant derivative, rather than the standard derivative, acting upon the Higgs field.

Prior to the discovery of the  $W^{\pm}$  and  $Z^0$  bosons, comparison of the electroweak theory to the Fermi theory of weak interactions allowed the vacuum expectation

value, v, to be expressed as  $v^2 = 2^{-\frac{1}{2}}G_F^{-1}$ , where  $G_F$  is the Fermi constant, and thus to be shown to have a value of approximately 246 GeV. This value, along with the value for the Weinberg mixing angle<sup>iii</sup> and the electromagnetic coupling constant, gave the predicted masses of the  $W^{\pm}$  and  $Z^{0}$  bosons to be 80 and 90 GeV respectively [10]; in excellent agreement with the current best-fit values of  $80.398\pm0.025$  GeV and  $91.1876\pm0.0021$  GeV [11]. These predictions were a strongly supportive of the standard model and a similar prediction for the mass of the Higgs boson would be highly desirable. As it is not possible to separate the terms  $\lambda$  and  $mass_h$  it is impossible to predict either value individually.

#### 1.1.1.4 Lyukawa Coupling

$$\mathcal{L}_{Yukawa\ Coupling} = -G_i^d \{h+v\}_2 \left(\overline{Q}_i d_i + Q_i \overline{d}_i\right) -G_i^u \{h+v\}_2^{\dagger} \left(\overline{Q}_i u_i + Q_i \overline{u}_i\right) -G_i^e \{h+v\}_2 \left(\overline{L}_i e_i + L_i \overline{e}_i\right)$$

(1.16)

where  $\{h+v\}_2$  again represents the  $SU(2)_{isospin}$  doublet form of the Higgs field and the vacuum expectation value. Q and L respectively represent the lefthanded Quark- and Lepton- doublet, u, d and e represent the right-handed u-type quark, d-type quark and charged-lepton singlets and the index, i, runs from 1 to 3 representing three generations of particles. The term,  $\{h+v\}_2^{\dagger}$ , is used to indicate the conjugate Higgs field, defined to be  $-i\sigma_2\{h+v\}_2^*$ , so as to include interactions with the upper half of the doublet. The terms,  $G_i$ , are the coupling constants.

Direct comparison with the Dirac Lagrangian iv yields the identity:

$$mass_x = \frac{G^x v}{\sqrt{2}} \tag{1.17}$$

The Weinberg mixing angle,  $\theta_W$ , is defined by  $cos(\theta_W) = \frac{g_2}{\sqrt{g_1^2 + g_2^2}} = \frac{mass_{W^{\pm}}}{mass_{Z^0}}$  or  $tan(\theta_W) = \frac{g_2}{g_1}$  iv  $\mathcal{L}_{Dirac} = \frac{i}{2} \{ \overline{\psi} \gamma^{\mu} \partial_{\mu} \psi - (\partial_{\mu} \overline{\psi}) \gamma^{\mu} \psi \} - m_{\psi} \overline{\psi} \psi$  where  $\psi$  is a spinor field and  $m_{\psi}$  is the mass of the fermion associated with that field.

or by comparison with equation 1.8:

$$G^{x} = 2\sqrt{\lambda} \frac{mass_{x}}{mass_{h}} \tag{1.18}$$

Noting also that the strength of the interaction between the Higgs boson and the spinor fields (that is, terms of the form  $hX_ix_i$ ) is dependent only on the coupling constant,  $G_i^x$ , implies that the strength of the interaction is linearly dependent on the ratio of the fermion mass to the Higgs mass, and as such the Higgs Boson interacts preferentially with heavier particles.

The addition of a neutrino mass term depends on the nature of neutrinos themselves. If neutrinos are Dirac particles, then their mass may be taken into account by the addition of a term of the form  $-G_i^n\{h+v\}_2^{\dagger}(\overline{L}_in_i+L_i\overline{n}_i)$ , where n indicates the right-handed neutral-lepton singlet. If, on the other hand, neutrinos are Majorana particles, their mass may be included by the addition of a term of the form  $-\frac{m_i}{2} \hat{n}_i n_i$ , where the term  $\hat{n}_i$  is used to indicate the conjugate neutrino field,  $-i\sigma_2 n_i^*$  and m must be generated by either a Higgs triplet or an effective operator involving two Higgs doublets arranged to transform as a triplet. As Majorana type mass terms couple left-handed states to left-handed states and similarly right-handed states to right-handed states, the masses of left-handed and right-handed Majorana neutrinos are decoupled and may possess different values. Furthermore, a Majorana neutrino may also interact with the Higgs Boson through the Yukawa mechanism, thereby also introducing a Dirac mass term for the neutrinos. If this is the case then a value of zero for the left-handed Majorana mass, a value at the electro-weak scale for the Dirac mass and a value at the Planck scale for the right-handed Majorana mass results "naturally" in an effective neutrino mass which is very much smaller than the electro-weak scale, as observed. Such a mechanism is known as a type-I see-saw mechanism. As yet, the true nature of neutrinos is unknown; namely, whether they are Dirac or Majorana particles, whether left- and right-handed neutrinos have different masses and whether the see-saw mechanism is an accurate description of neutrino mass generation.

As previously stated, the three generations of particles are now known not to be independent, but to interact via the CKM and PMNS mechanisms. This requires modifying terms of the form,  $G_i^x\{h+v\}_2(\overline{X}_ix_i+X_i\overline{x}_i)$  to  $G_{ij}^x\{h+v\}_2(\overline{X}_ix_j+X_i\overline{x}_j)$ , where  $G_{ij}$  indicates the inclusion of the relevant mixing matrix element into the coupling constant.

#### 1.1.2 Searches for the Higgs Boson

Given that the Higgs mechanism is currently the simplest known method of electroweak symmetry breaking, and, that the mechanism requires the existence of at least one (as yet unobserved) massive scalar boson, most particle physicists are focused on the search for the Higgs boson or one of its supersymmetric equivalents [12, 13, 14, 15, 16, 17].

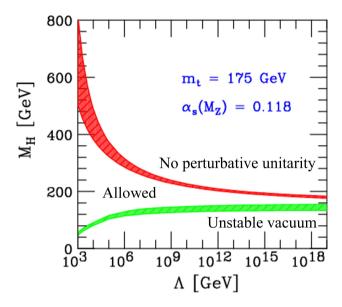

Although the existence of the Higgs boson has still to be demonstrated, should it conform to the standard model description, its properties and couplings are well understood; namely, it is massive, spin-o, uncharged and uncoloured. Although the mass of the Higgs boson is not directly predicted by the standard model, it is theoretically constrained to be less than the order of 1 TeV (figure 1.5) by the requirement that the scalar field theory is noninteracting, the so-called unitarity bound. Exclusion of the Higgs boson with a mass of less than 1 TeV will directly imply that the standard model is fundamentally flawed. The mass is also constrained by the fact that the Yukawa couplings act to oppose the vacuum potential: if the Yukawa couplings are too strong or, equivalently, the Higgs mass is too low, the potential is modified such that the vacuum expectation value, v, vanishes. This is forbidden as the main purpose for the inclusion of a Higgs field in the standard model is the generation of a non-zero vacuum expectation value. As such, the mass of the Higgs boson is constrained from below; the so-called vacuum-stability bound.

Conversely, the relationships indicated in figure 1.5 may be inverted such that, should the Higgs boson be found, its mass may be used to provide insight as to

vequivalently described as "trivial"

the energy scale,  $\Lambda$ , at which "new physics" is required by the standard model. For a Higgs mass of between 130 GeV and 180 GeV, this energy scale is the Planck energy ( $10^{19}$  GeV). For masses outside this range, "new physics" is required at energies lower than the Planck scale.

**Figure 1.5:** Bounds on the mass of the Higgs boson following from the requirement that the electroweak theory is consistent up to the energy scale  $\Lambda$ , where  $\Lambda$  is the energy scale at which "new physics" appears.

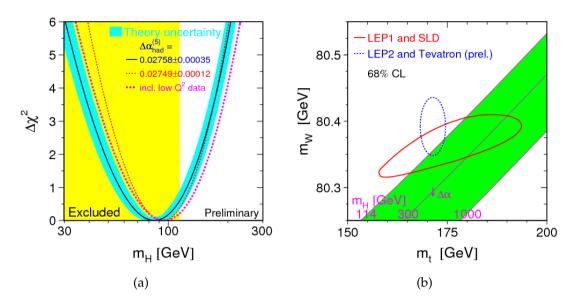

Although, as stated previously, the mass of the Higgs boson is not directly predicted by the standard model, the probability of any particular mass can be inferred using measurements of the radiative corrections to the  $W^{\pm}$  and  $Z^0$  bosons in the channels  $W^+ \to \bar{b}t \to W^+$ ,  $W^- \to \bar{t}b \to W^-$ ,  $Z \to \bar{t}t \to Z$ ,  $Z \to HZ \to Z$  and  $W^{\pm} \to HW^{\pm} \to W^{\pm}$ . Hence, accurate measurement of the  $W^{\pm}$ ,  $Z^0$ , t and b masses made at the LEP[18] and Tevatron[19] facilities can be used to infer the most likely Higgs mass [20]. Direct measurements at LEP[21] exclude the possibility of a Standard Model Higgs with a mass less than 114.1 GeV. Measurements at Tevatron[22] exclude at 95% confidence level, the possibility of a Standard Model Higgs with a mass of 170 GeV.

Figures 1.6(a) and 1.6(b) indicate the current status of Higgs searches. The yellow region in 1.6(a) indicates the 95% confidence level exclusion as demonstated by LEP. These results exclude at 95% confidence the probability of a Higgs mass greater than 185 GeV.

Figure 1.6: Latest results of searches for the Higgs boson. Taken from [20].

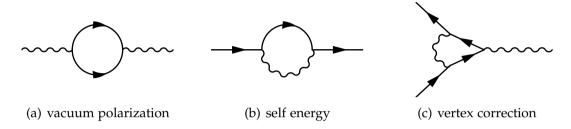

#### 1.1.3 Objections to the standard model

The significance of the result by 't Hooft [9] is that, for gauge invariant theories, higher order divergent diagrams such as those in figures 1.7(a), 1.7(b) and 1.7(c) can be 'tamed' by the processes of regularization and renormalization. The processes shown in figures 1.8(a)-1.8(e), however, diverge as  $\frac{s}{M_W^2}$  as  $s \to \infty$  without the systematic cancellations introduced by adding scalar diagrams of the type in figures 1.8(f) and 1.8(g). The standard model Higgs boson is a suitable candidate for such a scalar particle and, as such, provides an elegant solution to the so-called "unitarity problem" [23]. If the standard model Higgs is demonstrated not to exist, detailed studies of WW scattering in the energy range around  $M_W^2$  will provide alternative insight into the true behaviour of nature.

The cancelling of W scattering divergences by the standard model Higgs boson raises extra problems; the first is that the cancellation is 'conspiratorial', requiring that the various couplings are finely tuned. The second is that direct calculations of the standard model Higgs mass suffer their own divergences. One possible solution to this problem is the introduction of a SuSy (SuperSymmetric) partner for every standard model particle; a fermionic partner for each standard model boson and a bosonic partner for each standard model fermion. The high

**Figure 1.7:** Feynman diagrams for the three sources of ultraviolet divergences in the standard model.

**Figure 1.8:** Feynman diagrams for the process  $WW \rightarrow X \rightarrow WW$ .

degree of symmetry allows for the systematic cancellation of all divergences at the expense of adding a plethora of, as yet, unseen particles: 1 photino, 2 winos, 1 zino, 8 gluinos, 6 sleptons, 6 squarks and at least 5 Higgs bosons and their fermionic partners. Extensions to the minimal model also include the graviton and gravitino. To date, no evidence of supersymmetry has been found [11].

A further objection to the standard model is the large number of parameters which cannot be determined from theory, but must be constrained by observation, namely the 3 fundamental constants (c, G and  $\hbar$ ) and 19 parameters (6 quark masses, 3 CKM angles, 1 CKM phase, 3 charged lepton masses, 3 gauge coupling strengths, the QCD (Quantum ChromoDynamics) vacuum angle, the Higgs vacuum expectation value and the Higgs coupling strength<sup>vi</sup>). More recent observations have demonstrated the need for at least 7 further parameters: 3 neutral lepton masses, 3 PMNS angles and 1 PMNS phase. The introduction of supersymmetry worsens this situation by adding at least 105 further parameters. Furthermore, the weak-hypercharge, weak-isospin and colour-charge of each field is assumed to be a fundamental property of the field and are neither explained nor their values predicted.

By excluding a large section of the available SuSy parameter space, direct searches up to the TeV range will provide the strongest possible evidence as to whether supersymmetry does, in fact, apply to the universe that we observe. Even without direct production (or lack thereof) of supersymmetric particles, the exclusion of a Higgs boson with mass less than 1 TeV automatically excludes both the standard model and all supersymmetric models, as all rely on the Higgs mechanism for the generation of mass.

Although the CP-violating QCD Lagrangian term of the form  $\frac{\theta_{QCD}}{64\pi^2}e^{\mu\nu\rho\sigma}G_{\mu\nu}G_{\rho\sigma}$  is gauge invariant and hence not excluded from the standard model Lagrangian, current limits on the QCD vacuum angle,  $\theta_{QCD}$ , place an upper bound of  $10^{-10}$  on its value. As  $\theta_{QCD}$  is treated as a parameter, the standard model offers no explanation as to why this type of interaction is so much weaker than all other

vior alternatively, as stated previously, the Higgs mass

interactions or is possibly excluded altogether. At the same time, the standard model offers no explanation for the source of the CP-asymmetry required for baryogenesis.

Although not an insuperable objection, much of the search for a good theory of particle interactions has also been a search for an aesthetically pleasing theory: a theory that "feels" right<sup>vii</sup>. Generally, in physics, beauty is synonymous with simplicity of form and with the fact that key features should not happen by chance, but should have some underlying cause. In this sense, the standard model is blemished; in particular —

- The  $SU(3)_{colour} \times SU(2)_{isospin} \times U(1)_{hypercharge}$  gauge group structure is included by hand to explain observations; there is no deeper principle behind this choice or explanation as to why higher groups are excluded.

- The formation of left-handed  $SU(2)_{isospin}$  doublets and right-handed singlets is, again, unexplained. Left-right symmetric models are generally regarded as more satisfactory.

- The number of generations,  $N_g = 3$ , is unexplained.

- The quantization of electric charge,  $Q_d = -\frac{1}{2}Q_u = \frac{1}{3}Q_e$ , is unexplained.

The standard model both lacks a mechanism for the inclusion of gravity, and worse, produces results directly at odds with general relativity: the vacuum energy density of the Higgs field ( $10^8 \,\text{GeV}^4$ ) is vastly different from the cosmological constant ( $10^{-46} \,\text{GeV}^4$ ) predicted by the latter theory [24]. Furthermore, cosmological results indicate the presence of dark matter [25] and dark energy [26], for which the standard model provides no candidates.

Finally, the standard model fails to explain the discrepancy between the observed mass scale ( $1 \, \text{eVc}^{-2}$  to  $170 \, \text{GeVc}^{-2}$ ) and the natural (Planck) mass scale: ( $10^{19} \, \text{GeVc}^{-2}$ ); the so-called "Heirarchy problem".

viiSuch an attitude is sometimes referred to as Paul Dirac's religion of mathematical beauty

#### 1.2 The Large Hadron Collider (LHC)

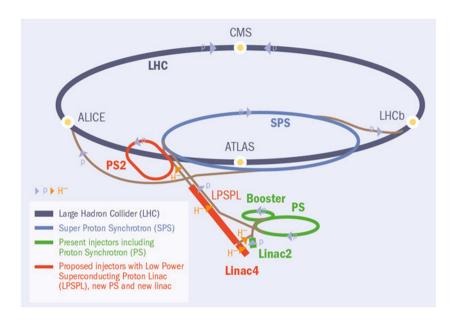

The LHC (Large Hadron Collider) [27] is a proton-proton collider based at CERN, operating at a maximum centre-of-mass energy of 14 TeV, a collision rate of 40 MHz and a nominal luminosity of 10<sup>34</sup> cm<sup>-2</sup>s<sup>-1</sup>. The principle aims of the LHC are (1) to elucidate the nature of electroweak symmetry breaking (for which the Higgs mechanism is assumed to be responsible) and (2) to search for physics beyond the standard model [28]. As a hadron collider, the LHC cannot be used to make precision measurements allied to those made at LEP, but rather provides both a window to access phenomena at the energy frontier and those with ultra-low cross sections. In order to do so, the LHC is designed to operate at unprecedented energies and to produce large numbers of DIS (Deep Inelastic Scattering) collisions during every BX (Bunch Crossing) . A second mode of operation allows the LHC to collide lead ions at a centre of mass energy of 5.5 TeV per nucleon, with the express purpose of studying quark-gluon plasmas.

Due to the composite nature of the proton, the available energy in each collision is only a fraction of the 14 TeV centre of mass energy; the LHC is expected to permit discovery ( $5\sigma$  signal) of new phenomena up to an energy of 1 TeV, with access to physics above this energy being limited by statistics. A lack of statistics does not exclude discovery above 1 TeV with some signals being "unmissable" [29] [30].

The LHC hosts 6 experiments: the two general purpose detectors, CMS (Compact Muon Solenoid) and ATLAS (A Toroidal LHC ApparatuS), are designed to verify the standard model and to search for a wide range of new physics phenomena; the ALICE (An LHC Ion Collider Experiment/A Large Ion Collider Experiment) [31] experiment is designed for heavy ion studies; and LHCb for studying CP-violation in the b-quark sector. Two further small experiments, Totem (Total Cross Section, Elastic Scattering and Diffraction Dissociation Measurement) and LHCf study diffractive physics in the extreme-forward regions on either side of the CMS and Atlas experiments.

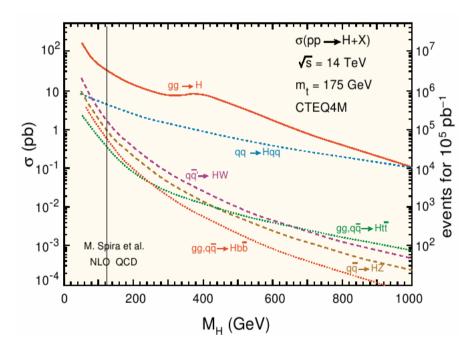

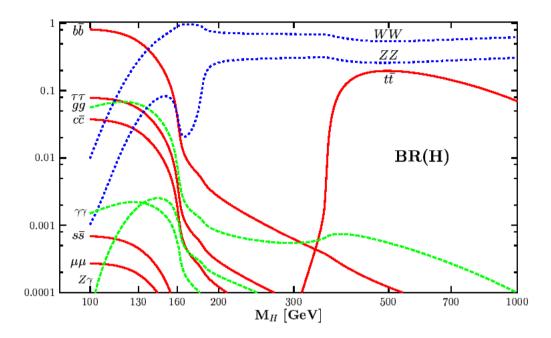

Although the general purpose detectors were designed to look for any signs of 'new' physics, the most keenly anticipated is the discovery of the standard model Higgs boson. The five dominant production channels for the standard model Higgs at LHC are gluon-gluon fusion (via a heavy quark loop), vector-boson fusion, vector-boson bremsstrahlung<sup>viii</sup>,  $t\bar{t}$  fusion and  $b\bar{b}$  fusion. The dominance of these modes is due to the fact that the Yukawa and Higgs couplings in the Standard Model are proportional to a particle's mass; this fact similarly controls the ratio of the various decay modes. Figures 1.9 and 1.10 demonstrate the cross-sections and branching ratios of each mode.

**Figure 1.9:** Higgs production channels at the LHC. The channel labelled  $gg \to H$  represents gluon-gluon fusion via heavy quark loop,  $qq \to Hqq$  represents vector-boson fusion,  $q\bar{q}' \to HW^\pm$  and  $q\bar{q} \to HZ^0$  represents vector-boson bremsstrahlung (higgsstrahlung).  $gg, q\bar{q}' \to Ht\bar{t}$  and  $gg, q\bar{q}' \to Hb\bar{b}$  respectively represents  $t\bar{t}$  and  $b\bar{b}$  fusion. The region to the left of the vertical line at  $M_H = 120\,\text{GeV}$  is excluded by LEP.

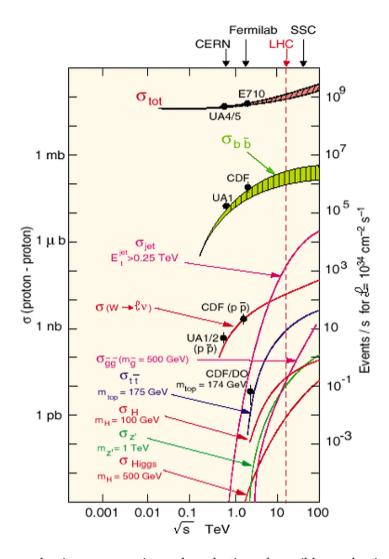

The production cross section of the Higgs boson cannot be taken in isolation, but must be taken in relation to that of all possible processes. As can be seen in figure 1.11, the cross section (and hence production probability) of Higgs processes are between 9 and 11 orders of magnitude (dependant on the mass of the Higgs boson) lower than the total inelastic cross section and some 3 to

viii also known as Higgsstrahlung

**Figure 1.10:** Higgs decay modes in the mass range accessible at the LHC. The decay of the Higgs boson to massless particles is necessarily mediated by heavy fermion loops.

5 orders of magnitude lower than  $W^{\pm}$  and  $Z^{0}$  production cross section, with the general effect that the signal is "swamped", not only by the dominant QCD processes but also by the electroweak signals which LEP was built to study.

In order to accommodate such low production probabilities, it is necessary to have a very high interaction rate, this requiring a very high beam luminosity. At LHC energy scales the total proton-proton cross-section is estimated to be 100 mb, of which 30 mb is expected to be elastic and therefore not relevant to the experiments. At the design luminosity of  $10^{34} \, \mathrm{cm}^{-2} \mathrm{s}^{-1}$ , the 70 mb inelastic scattering cross-section equates to an event rate of  $7 \times 10^8 \, \mathrm{s}^{-1}$ . The beam is not continuous, but bunched with a crossing rate of 40 MHz, and only around 80% of bunches are filled, this resulting in an average event rate of 22 events per crossing.

The number of charged tracks per crossing at the LHC is in the order of one-thousand [33] and the event data size around 1 MByte per event [34]. As such the experiments face many challenges not faced at previous experiments.

**Figure 1.11:** The production cross-sections of a selection of possible production modes at the LHC as a function of interaction energy. Adapted from [32].

The high crossing rate (40 MHz) places strict demands on the speed at which the sensors must collect data and the speed at which the data must be read out from the detectors, this limiting the choices of available technologies. The large number of interactions per crossing requires precision tracking in order to separate vertices and to locate secondary vertices. Both the high crossing rate and high interaction rate result in "pile-up" effects in two forms: "in-time" pile-up, which is the result of uninteresting (at least for the LHC) QCD events (termed minimum-bias), and "out-of-time" pile-up, where particles from previous crossings remain in the detector, looping in the magnetic field. The large number of particles also result in a massive radiation dose exceeding 30 MRad

(300 kGy) and 10<sup>15</sup> cm<sup>-2</sup> neutron equivalent dose in the forward regions of the detectors over the expected lifetime of the tracker [35]. This not only requires radiation tolerance of the active components, both in terms of resilience to long-term damage and tolerance to SEUs (Single Event Upsets) <sup>ix</sup>, but also careful choice of materials to minimize material radioactivation over the lifetime of the experiments [38].

Not only must the detectors withstand the environment, but they require excellent resolution in order to separate signal from background: for instance, the cleanest decay signal for a low mass Higgs boson is the decay  $H \rightarrow \gamma \gamma$ , but even this requires excellent calorimetry in order to identify the signal over the background (see figure 1.12).

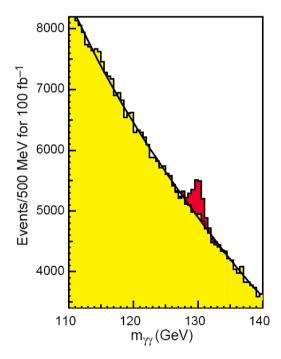

**Figure 1.12:** A comparison of  $H \rightarrow \gamma \gamma$  signal(red) and background(yellow) for a Higgs mass of 130 GeV and 100 fb<sup>-1</sup> of data recorded. Adapted from [39].

The other 'golden' decays,  $H \rightarrow \tau\tau$ ,  $H \rightarrow ZZ \rightarrow l^+l^-l^+l^-$  and  $H \rightarrow ZZ \rightarrow jjl^+l^-$  (where

<sup>&</sup>lt;sup>ix</sup>An SEU occurs when a charged particle passes through the an electronic component, changing the state of a bit in a digital logic circuit or in a memory element. This is typically mitigated by using triple-redundant logic where each circuit element is triplicated and the state determined by a majority rule. [36] [37]

*j* represents a jet), similarly require both excellent calorimetry and particle tracking to separate them from the background.

## 1.3 The Compact Muon Solenoid (CMS)

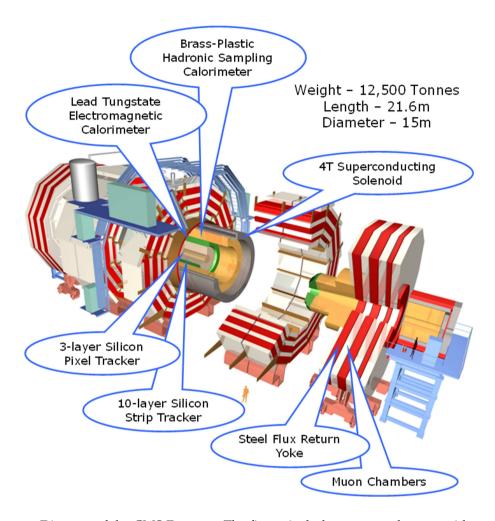

CMS [40] is the smaller of the two general-purpose detectors at the LHC. It is a hermetic detector covering the rapidity range from  $-3 < \eta < +3$  at full detector resolution and having an extended rapidity range of  $-5 < \eta < +5$ . Moving radially from the beampipe, the detector consists of a pixel tracker, a silicon microstrip tracker, a homogeneous lead tungstate electromagnetic calorimeter, a brass-plastic sampling hadronic calorimeter, a four Tesla superconducting magnet, a second hadronic calorimeter and an iron flux return yoke interspersed with muon detectors. The detector is shown in figure 1.13.

#### 1.3.1 The Silicon Tracker

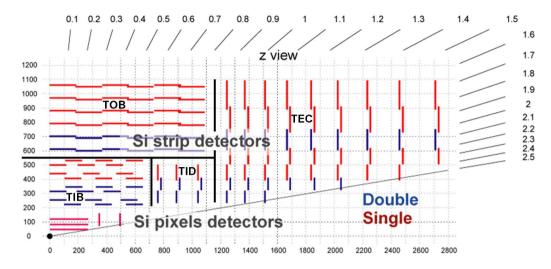

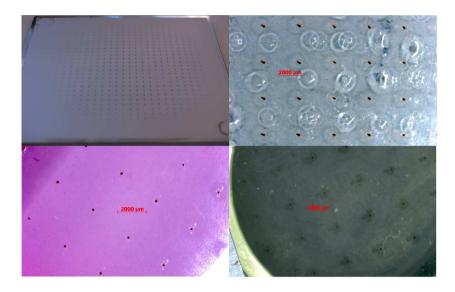

The CMS tracker [41, 42] (figure 1.14) consists of three layers of silicon pixel sensors and ten layers of silicon microstrip sensors in the barrel, and twelve layers in either endcap. The inner layer of the pixel detector is at a 4 cm radius from the nominal interaction point and, as such, has to cope with high particle fluences; a  $3.2 \times 10^{15}$  cm<sup>-2</sup> neutron equivalent dose is expected over the lifetime of the experiment. It must be situated close to the interaction region in order to identify the (approximately 20) separate vertices, tag 'long-lived' particles such as b and c quarks and  $\tau$  leptons, and to identify light quark and gluon jets. The microstrip tracker provides many widely spaced points for precision momentum and vertex measurements [43]. The entire silicon tracker is 5.4 m long, has a diameter of 2.4 m and is operated at -10 °C to minimize the effects of radiation damage. The pixel tracker has 45 million channels and the strip tracker a further 10 million.

The CMS pixel detector is a hybrid design consisting of a silicon sensor with rectangular pixels of pitch  $100 \, \mu \text{m}$  (r $\phi$ ) by  $150 \, \mu \text{m}$  (z) and a separate readout

**Figure 1.13:** Diagram of the CMS Detector. The figure includes two people to provide an indication of scale.

chip. The sensors require a large external bias voltage (up to 600 volts), a large depletion region and fast charge collection to ensure a useable signal after heavy irradiation and in order to be read out within a single bunch-crossing. Each pixel contains a set of n-on-n diodes and a contact pad for bump bonding it to the corresponding channel on the readout chip. The readout chip [44] provides an analogue readout of the pixels, performs a comparison to threshold on a pixel-by-pixel basis, stores the data in a pipelined buffer while waiting for a level-1 trigger decision and provides a sparsified analogue readout via a high-speed token-ring. Because the readout is analogue, interpolation may be used to improve the spatial resolution to approximately 10  $\mu$ m in r $\phi$  and 15-20  $\mu$ m in z [45].

**Figure 1.14:** Layout of a quarter of the CMS tracking detector. This image is mirrored along both axes to make the full detector layout. The interaction point is marked at z=0.

The CMS microstrip tracker is similarly a hybrid design with the strips being read out by the APV25 (Analogue Pipeline Voltage, 0.25  $\mu$ m) [46] readout chip. The sensors consist of either 512 or 768 strips with pitch ranging from 80  $\mu$ m to 205  $\mu$ m and length ranging from 9 cm to 20 cm [47, 48].

In the readout chip, each channel is preamplified, shaped and sampled before being stored in a pipelined buffer whilst waiting for a level-1 trigger decision. The APV25 has two sampling modes; peak mode where the signal is sampled once, at the peak, and deconvolution mode where the signal is sampled before, at and after the peak, and the signal reconstructed using an Analogue Pulse Shape Processor. The mode is selected according to the beam luminosity with the former mode at low luminosity (less susceptible to noise) and the latter at high luminosity (less susceptible to pile-up). Each APV25 chip reads out 128 channels. For the microstrip tracker, zero-suppression is not performed on-detector.

Upon receipt of a level-1 trigger signal, the buffered analogue signals are timedivision multiplexed (in order to reduce the cabling requirements) and transmitted optically. This results in approximately 45,000 analogue optical readout fibres leaving the detector. The use of analogue signals was driven primarily by power considerations, namely that the power consumed by digitization increases with the speed of digitization and that within the tracker access for both power and cooling (to compensate for the increased heat dissipation) are severely restricted. There are however additional benefits;

- The ability to interpolate between channels thereby increasing the effective resolution

- A reduced susceptibility to noise by minimizing the number of manipulations made on detector, mitigating the possibility of 'bit-flipping' upsets.

- The possibility of monitoring degradation of the sensors and readout chips by studying the signal quality.

Track reconstruction by combinatorial Kalman filtering gives a track reconstruction efficiency of approximately 100% for muons in the acceptance range, whilst electron/hadron reconstruction efficiencies range from 95% in the central region to 80% in the forward region. For  $p_T$ =100 GeV muons in the central region, the  $p_T$  resolution is between 1% and 2% and improves at lower track momentum. The tracker can determine the impact parameter with a resolution of 20  $\mu$ m for  $p_T$ =100 GeV tracks, although this performance degrades at lower momentum due to multiple scattering [49].

## 1.3.2 The Electromagnetic Calorimeter (ECAL)

The ECAL (Electromagnetic Calorimeter) [39] is a homogeneous scintillating crystal calorimeter. The requirement that the ECAL and HCAL be located within the solenoid severely limits the size of the calorimeter. In order to achieve high containment in the limited space available, lead tungstate was chosen due to its small Molière radius (2.2 cm) and short radiation length (0.89 cm) [45]. Additionally, lead tungstate has a high radiation tolerance and a rapid light collection time (> 80% in one bunch-crossing). It does, however, have a relatively low light yield and, as such, the light signal must be amplified. This is achieved using APD (Avalanche PhotoDiodes) in the barrel and radiation hard VPTs (Vacuum

PhotoTriodes) in the endcaps, where the radiation dose is greater and the magnetic field is close to axial. The barrel ECAL uses two APDs per crystal for the purpose of noise mitigation. Each crystal has a front face of 2.2 cm×2.2 cm in the barrel section (approximately 0.0175×0.0175 in  $\eta \times \phi$ ) and a depth of 230 mm. The energy resolution is  $\frac{\sigma_E}{E} = \frac{0.125}{E} \oplus \frac{2.9\%}{\sqrt{E}} \oplus 0.3\%$ , better than the design value of 0.5% for electrons and photons at 100 GeV.

The ECAL signals are digitized on detector and trigger primitives generated for each trigger tower ( $5\times5$  crystals in the barrel and approximations to  $\eta$ - $\phi$  segments in the endcaps). The trigger primitives are sent off-detector to the calorimeter trigger (see chapter 2), while the raw data is stored in a pipelined buffer pending a level-1 trigger decision.

#### 1.3.3 The Hadronic Calorimeter (HCAL)

Heavier particles and their decay products are not contained in the ECAL and penetrate through to the HCAL (Hadronic Calorimeter) [50]. In the barrel this is a sampling calorimeter with a brass absorber and plastic scintillator which is read out by HPD (Hybrid PhotoDiode) sensors coupled via wavelength-shifting fibres. In the forward endcap region, quartz Cerenkov fibres, rather than plastic scintillator, are embedded into steel absorber due to their greater radiation tolerance. The energy resolution is measured to be  $\frac{\sigma_E}{E} = \frac{75\%}{\sqrt{E}} \oplus 8\%$ , compared to the design value of  $\frac{\sigma_E}{E} = \frac{100\%}{\sqrt{E}} \oplus 4.5\%$ ; the poor energy resolution<sup>x</sup> is currently the limiting factor in CMS' calorimetry and is closely related to the lack of longitudinal shower information from the HCAL towers and noise in the readout electronics. Upgrades to both are currently under investigation.

#### 1.3.4 The Muon Detectors

The CMS detector intersperses the iron magnetic-flux return circuit with three types of muon stations. In the barrel, DTs (Drift Tubes) provide precision track-

<sup>\*</sup>For comparison, the ATLAS Copper-Liquid Argon HCAL has a resolution of  $\frac{\sigma_E}{E} = \frac{45\%}{\sqrt{E}} \oplus 1.3\%$ .

ing while RPCs (Resistive Plate Chambers) provide charge collection sufficiently quickly to create tracks for the purpose of triggering at level-1. In the endcaps CSCs (Cathode Strip Chambers) provide the precision tracking while, again, RPCs provide triggering information. The spatial resolution of the muon detectors ranges from 50 to  $200 \,\mu\text{m}$ , translating to a momentum resolution of 15% for a muon with  $10 \,\text{GeV}$  p<sub>T</sub> and 40% at  $1 \,\text{TeV}$  when taken independently of the silicon tracker [51, 52].

#### 1.3.5 The CMS Trigger System

As stated in section 1.2, the LHC event rate is 40 MHz and the CMS event size is 1 MByte per crossing, resulting in a raw data rate of 40 PByte per second. As such, there is neither the readout bandwidth nor the storage capability to store all of the data produced. The peak storage rate for CMS is approximately 1 TByte per day (100 Hz) and, therefore, the data volume must be reduced by a factor of  $4 \times 10^5$  before anything can be written to disk. This data reduction is achieved by triggering; the selective storage of events based on a coarse-grained analysis of the data.

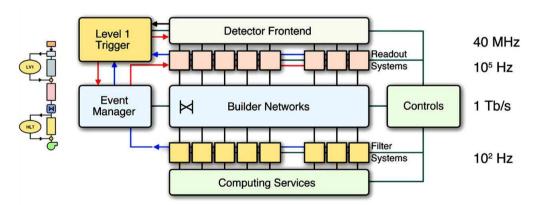

**Figure 1.15:** The CMS Trigger/DAQ System. Data from a subset of the detector is first sent to the level-1 trigger for processing. Upon a level-1 accept signal, the remaining detector data is read out to the Higher Level Trigger for further processing.

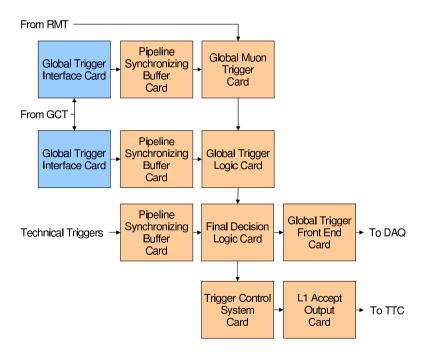

The CMS trigger [53, 54, 55] is achieved in two stages; the level-1 trigger and the HLT (Higher Level Trigger). The level-1 trigger [56] is a high bandwidth, fixed latency system based on FPGAs (Field Programmable Gate Arrays) and

ASICs (Application Specific Integrated Circuits). The enormous volume of data from the detector and the requirement of a trigger decision in a very short (and guaranteed) time period of 128 BX excludes the use of iterative algorithms, requiring instead pipelined algorithms and massive parallelization. The level-1 trigger uses only calorimetric and muon data, as the bandwidth requirement of the tracker is too large to allow read out of every bunch-crossing; instead, it is read out only once the level-1 accept signal is issued. The aim of the level-1 trigger is to reduce the data rate by an average factor of 400, from a rate of 40 MHz to 100 kHz. The Higher Level Trigger is a multi-stage iterative algorithm conducted on a farm of 3000 PCs: it uses full detector information to reproduce the level-1 trigger decision and then to iteratively improve on this decision by the staged introduction of fine-grained calorimetry information and tracking information. If, at any stage, the event is rejected, the process is halted and the processing resources freed for handling the next event. A time cut-off (the value of which depends on the process) is applied to prevent resources becoming locked. The aim of the HLT is to reduce the data rate by a further factor of 1,000 so that the data can then be recorded to disk and tape storage at approximately 100 Hz.

The purpose of the trigger system, particularly of the level-1 trigger, is not (as is often described) to identify interesting events from the background of uninteresting events. Such a definition would imply that it is already known which interesting events exist to be found. Instead, the trigger is designed to discard events that lie within our current understanding, while simultaneously having a threshold for acceptance that is sufficiently low to allow all possible signatures of new physics to be recorded. In CMS this is achieved by placing identifying the type of decay products and the transverse energy (particles from heavy states are emitted isotropically, while less interesting events are focussed in the forward regions) of those products; by this means, as few constraints as possible are placed on the discovery potential. This type of triggering is described as 'inclusive triggering'.

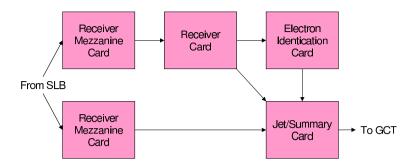

Figure 1.16: The CMS level-1 trigger.

#### 1.3.6 The CMS Level-1 Trigger

As stated previously, the level-1 trigger only uses data from the electromagnetic and hadronic calorimeters and tracks from the muon systems. Most of the trigger infrastructure is located in the USC (Underground Sorting Cavern) to minimize the cable latency: two exceptions to this are the ECAL trigger tower primitives, which are generated on the ECAL front-end electronics, and the muon local track finder which is performed on the racks on the outside of the detector.

The muon trigger creates tracks from hits, sorts all the tracks in an event by their transverse momentum and forwards the top four candidates to the global trigger.

The calorimeter trigger creates two different types of trigger object, reflecting the two fundamental types of energy deposition in the calorimeter; electron/photon candidates and jets. The former are spatially-compact objects mainly confined to the ECAL, while the latter are larger and primarily in the HCAL. The objects are classified by various criteria and sorted, with the four highest ranked candidates of each type being forwarded to the global trigger. The calorimeter trigger is discussed in detail in chapter 2.

The global trigger combines candidates from the muon and calorimeter triggers and, based on these combinations, decides whether to discard an event or whether to read out the full granularity information and forward it to the Higher Level Trigger. The trigger can be based either on simple objects, such as a single particle with a transverse momentum greater than a certain threshold, composite objects, such as "two electrons  $\lor$  two muons  $\lor$  (electron + muon)", or any other conceivable combination, although the object should be kept simple in order to avoid introducing bias.

Tracker information is not used in the level-1 trigger, because it was not believed to be necessary for triggering under LHC conditions. As such, the tracker was not designed to be capable of being read out for every event; the bandwidth requirement, the choice of analogue optical link technology [57, 58] and off-detector zero-suppression [59, 60] prohibiting this. Under conditions of higher luminosity this requirement changes and is discussed in chapter 6.

#### 1.3.7 The CMS Level-1 Trigger Software

Given the many different types of hardware and the vast number of control and processing subsystems, both on- and off-detector, the system used to control the experiment requires a great deal of flexibility and the ability to be scaled as required, while retaining complete reliability. The size and international nature of the collaboration also requires that the user interface is both standardized and clear, as those operating the experiment cannot be expected to be experts in all subsystems. This is achieved using a framework called XDAQ (Distributed Data AcQuisition) [61] which provides a platform-independent environment into which each subsystem dynamically loads its own software modules. The framework thus provides a standardized infrastructure for core tasks, such as message passing and data transfer via SOAP (Simple Object Access Protocol) or I<sup>2</sup>O (Intelligent Input/Output) over TCP/IP, which minimizes the amount of code duplication and thereby reduces the probability of errors. The framework

also provides a web-based interface through which the user interacts by means of a standard internet browser.

The modules used to control each subsystem are written as C++ classes based on standard XDAQ templates and are compiled as libraries that can be dynamically loaded at runtime. This allows individual subsystems to be started, stopped and recompiled without affecting the rest of the modules on that node.

Although the control system of the level-1 trigger is clearly very different from the control system of, for example, the silicon pixel tracker, within the level-1 trigger there are many tasks which are common to all subsystems. The Trigger Supervisor is a framework built upon XDAQ, specializing it for the task of controlling the subsystems of the CMS level-1 trigger and implementing the common functionality.

## Chapter 2

# The CMS Calorimeter Trigger System

"A man is too apt to forget that in this world he cannot have everything.

A choice is all that is left him."

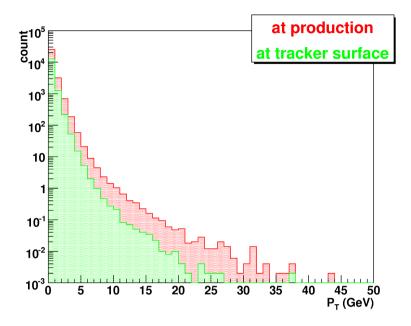

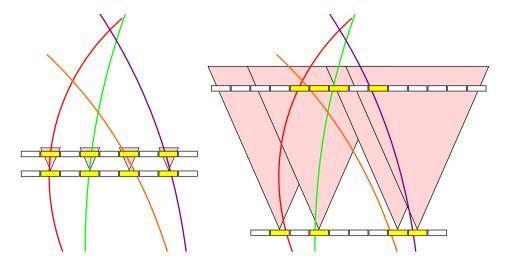

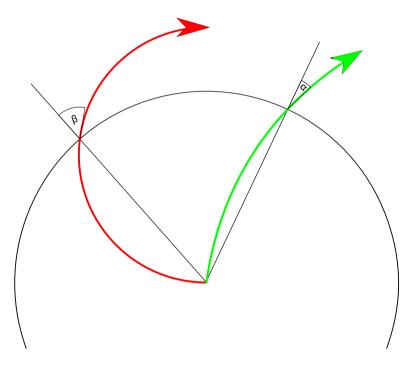

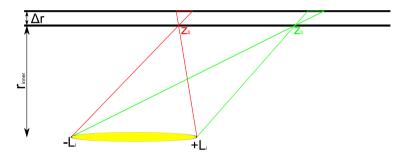

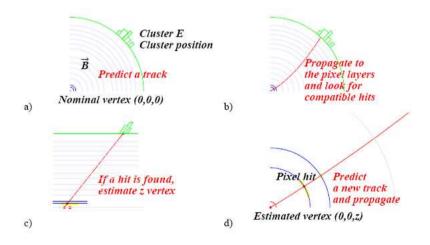

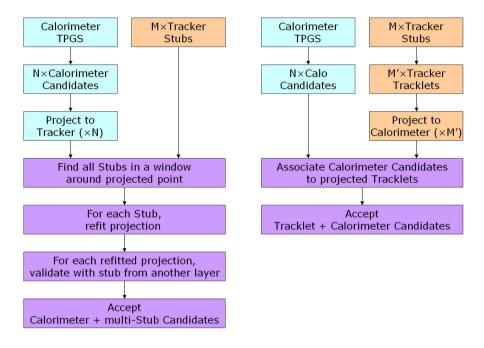

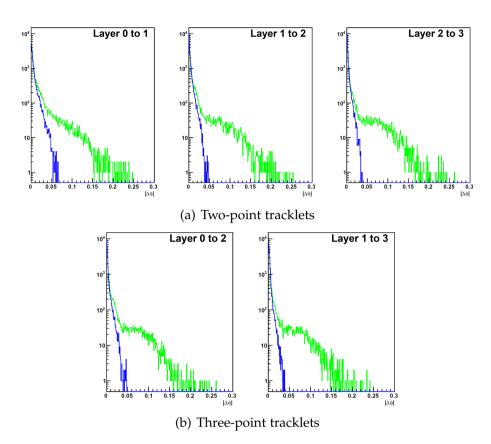

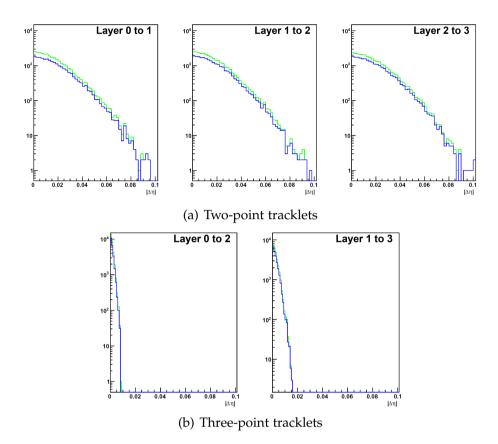

- Harry Mathews (1930 - )