# **Digital electronics**

•Explosive growth over 10-20 years - now dominates applications, still growing... computing

communications: mobile/fixed phones, radio, data links,...

other: digital audio, consumer goods,...

#### •Why?

binary logic

almost complete noise immunity

high speed, still increasing

Ethernet: ~Gb/s, phones, links: >Gb/s, computing ~GHz

ease of use

many analogue functions now easier to implement by digital summation, etc availability

basic logic to complete IC assemblies of big range of complex functions

#### •Bits, Bytes & Words

byte = 8 bits word: usually multiple of bytes 8, 16, 32, 64 bits

1

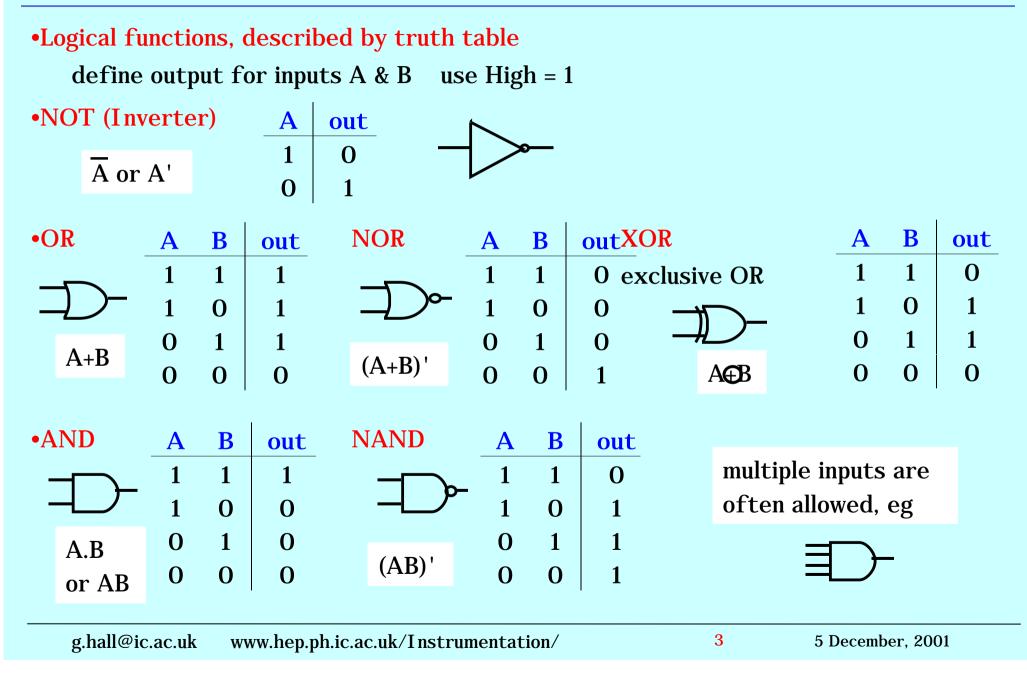

# **Basic logic**

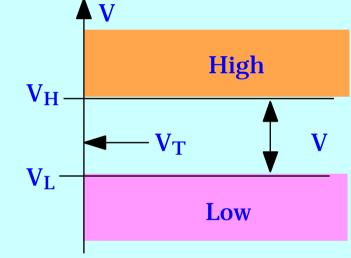

•bits can be represented in several ways, almost invariably voltage

0/1: Low/High (voltage level) ... or High/Low

values and range depend on families, most common are...

•TTL (bipolar) Transistor-Transistor Logic

usually  $V_s = 0$  to +5V

$V_{\rm T} \sim 1.5 V ~~ V \sim 1 V$

outputs & inputs sink/source currents not identical levels

•CMOS - now most common

$V_S = 0$  to +5V but +12V, +3.5V and lower

$V_{\rm T} \sim V_{\rm S} / 2$   $V \sim 0.4 V_{\rm S}$

outputs swing between supplies

•ECL Emitter Coupled Logic high speed, but power hungry

designs must tolerate variations component manufacture operating temperature supply voltage loading noise

## Logic gates

## **Negative-true logic**

it may be easier to think in terms of High & Low, eg...

|                 | Negative-true                        |   |    |    |       |     | OR |   |   |                  |  |

|-----------------|--------------------------------------|---|----|----|-------|-----|----|---|---|------------------|--|

|                 | Α                                    | B | Α' | B' | A'.B' | Q   |    | Α | В | $\mathbf{Q}$     |  |

|                 | L                                    | L | Η  | Η  | Η     | L   |    | L | L | L                |  |

|                 | L                                    | Η | Η  | L  | L     | Н   |    | L | Н | Н                |  |

|                 | Η                                    | L | L  | Η  | L     | Н   |    | Н | L | Н                |  |

|                 | Η                                    | Η | L  | L  | L     | Н   |    | Н | Н | Н                |  |

|                 |                                      |   |    |    |       |     |    |   |   |                  |  |

| g.hall@ic.ac.uk | www.hep.ph.ic.ac.uk/Instrumentation/ |   |    |    |       | on/ | 4  |   |   | 5 December, 2001 |  |

|                 |                                      |   |    |    |       |     |    |   |   |                  |  |

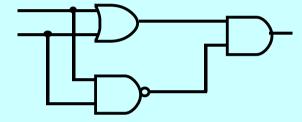

# Which gates are needed?

•Logic functions can be constructed from other combinations

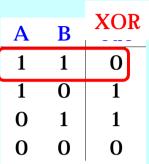

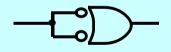

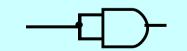

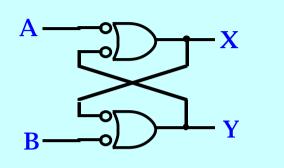

eg XOR

start from OR, change...

•A couple of examples...

what purpose could they serve?

•Several simple theorems of logic help to do translations if needed (see H&H)

DeMorgan's: Not(A+B) = NotA.NotB Not(A.B) = NotA + NotB

$NotA = A' = \overline{A}$

# A few applications

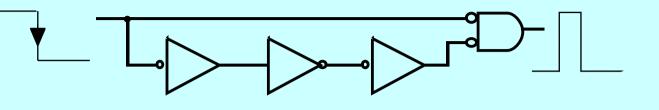

•Pulse on falling edge

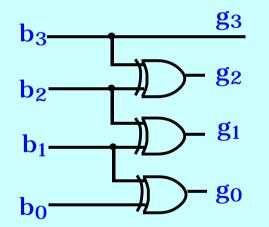

### •Gray coding

| binary | Gray |

|--------|------|

| 0000   | 0000 |

| 0001   | 0001 |

| 0010   | 0011 |

| 0011   | 0010 |

| 0100   | 0110 |

| 0101   | 0111 |

| 0110   | 0101 |

| 0111   | 0100 |

|        |      |

...

in Gray code, only 1 bit changes between states eg, valuable for controlling stepping motors simplifying logic sequences

## Memory - the Flip-flop

#### •Work out the truth table

| Α | B | Χ | Y |

|---|---|---|---|

| L | L | Н | Η |

| L | Η | Н | L |

| Η | L | L | Η |

| Η | Η | L | Η |

| Η | Н | Н | L |

Note the symmetry

so the state depends on the previous history of the flip-flop

#### •Clocked flip-flop S if CLK = L, state is maintained Q S $\mathbf{R} = \mathbf{Q}_{n+1}$ L L $Q_n$ R L. Η I. Η L Η Note the Η Η \_ complementary CLK

why is HH output undefined?

•We now have a memory device with Set & Reset, which runs sequentially

g.hall@ic.ac.uk www.hep.ph.ic.ac.uk/Instrumentation/

7

outputs

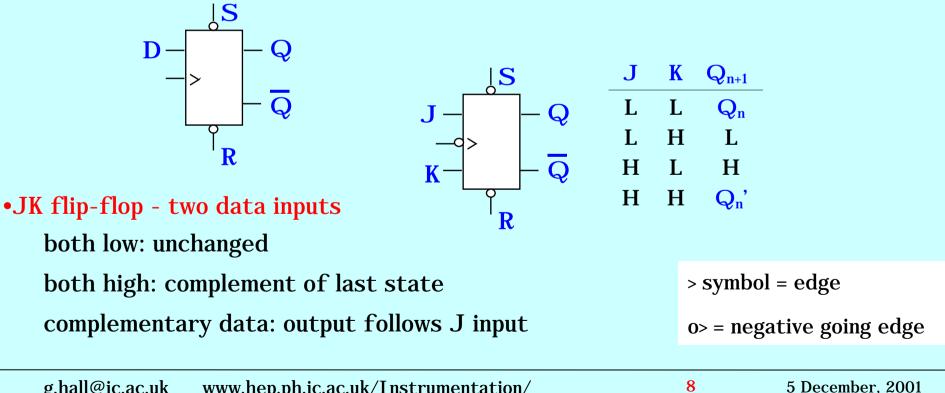

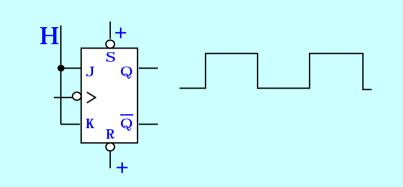

# **D** and **JK** flip flops

•even the clocked flip-flop is not quite sufficient

can't guarantee inputs will not change during clock high

the solutions are Master-Slave and edge triggered D flip-flops

•D-type flip-flop

transmits value at Data input to Q, on clock edge both positive and negative edge types available

# **Examples**

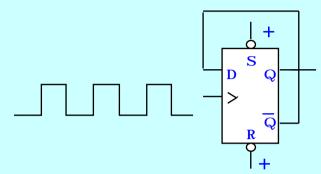

## •Divide clock frequency by 2

#### LSB •n-bit Counter $\mathbf{Q_0}$ set all $Q_i = L$ $Q_1$ $Q_2$ output changes on negative edge H H H H + S S S S follow outputs Q Q Ω J ₽ ₽ ₽ R Q . RQ K K K $\mathbf{Q}_{\mathbf{0}}$ L $\mathbf{Q}_{\mathbf{1}}$ L output = $HLL = 100_2 = 4$ $Q_2$ Η

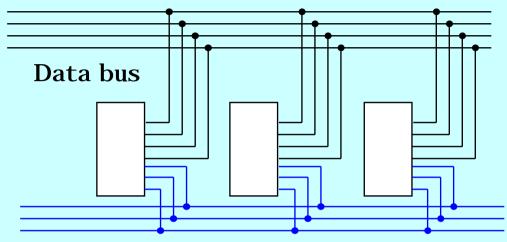

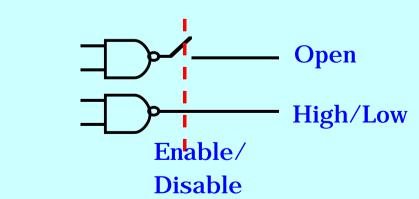

# **Tri-state logic**

•In some applications there is a need to connect to a "bus"

### •Bus

series of parallel lines shared between multiple devices typically 8-bit, 16-bit, 32-bit,..

Address bus

•but if all devices are connected to the bus... who has priority? potential recipe for confusion

•Solution, third logic state: "open circuit" ie HIGH, LOW and "OPEN" controlled by additional input: Enable

# **Programmable logic**

•For very complex logic, it's time consuming and risky to develop circuits programmable logic solves both problems

•PLA programmable logic array

transistor array with connections set by fuses to burn

## •FPGA field programmable gate array

MOS array of uncommitted gates - few k to several M connections made by downloading code which sets biasing of circuits fully re-programmable

## •DSP digital signal processor

$cut\mbox{-}down\ microprocessor\ with\ limited\ instruction\ set$

## •Various levels of complexity and skills to learn

$eg\ 2M\ gate\ FPGA\ needs\ sophisticated\ design\ and\ simulation\ software$