## 8CBC3.1 hybrid + CIC mezzanine : first results

Paolo Baesso, Jarne De Clerq, Davide Di Croce, Mykyta Haranko, Mark Kovacs, Stefano Mersi, Inna Makarenko, Alan Prosser, Sarah Seif El Nasr-Storey

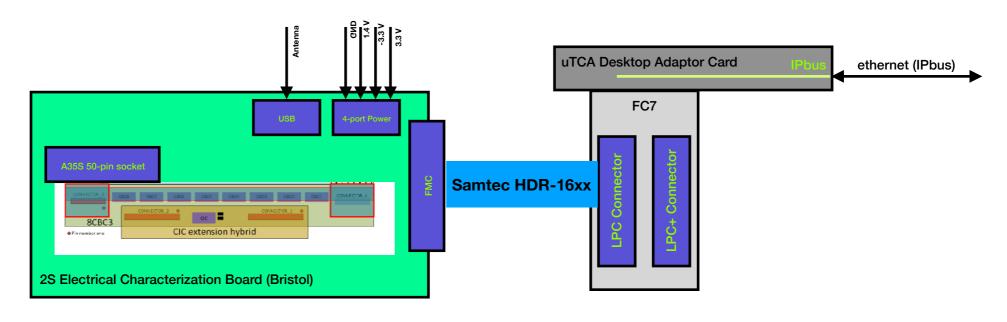

## **2S FEH prototype (CBC3.1 + CIC) : First Results** Read-out system for electrical readout of 2S FEH prototype

- FC7 based read-out system using :

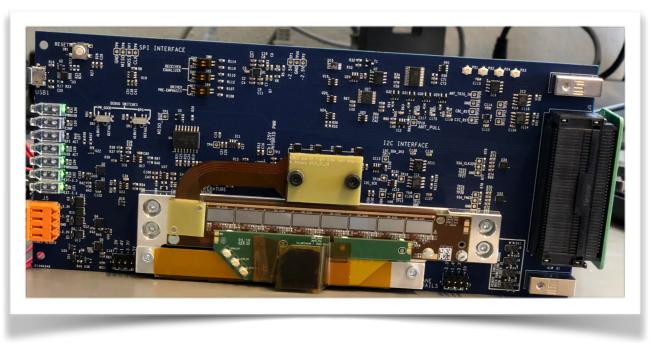

- 2S electrical characterization board for translation and buffering of output lines from CIC

- 8 CBC3.1 hybrid with a CIC extension hybrid

- Firmware for readout and control of a 2S FEH prototype

- Software for readout and control of a 2S FEH prototype based on simple python scripts (stand-in for Ph2\_ACF)

CMS

- Week of the 15th April spent testing read-out system and performing first checks on the 2S FEH prototype :

- M. Kovacs organized presence of experts for the entire week

- power-up checks on 2S electrical characterization board performed at Bristol the previous week

- experience in operating/working with the CIC courtesy of the stand-alone CIC set-up used for DAQ development

- Once basic connectivity between different components in the set-up was established set-up was used to :

- confirm connectivity between CIC mezzanine and 8CBC3.1 hybrid

- demonstrate that stand-alone CIC initialization sequence can be performed with the 2S FEH

- demonstrate that output of CIC (for hits) is consistent with what we expect from the CBCs under different conditions

- confirm validity of the automated BX0 identification in the CIC

## **2S FEH prototype (CBC3.1 + CIC)** Confirming connectivity between CBCs and CIC

4

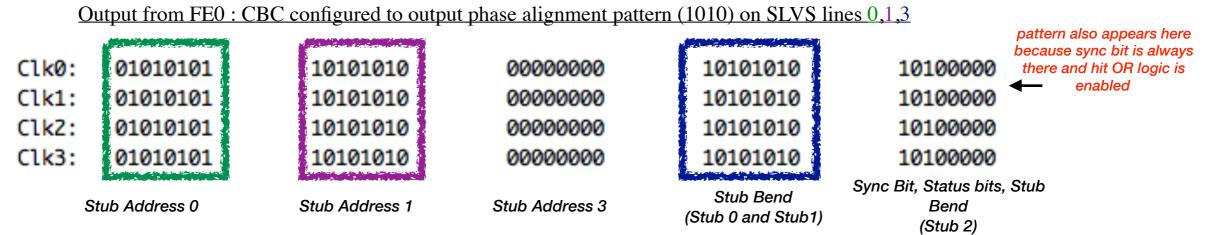

- CIC debug mode in which CIC core is bypassed and the output of any given phase aligner port is routed directly to the output lines of the CIC used to verify that all 8 CBCs, once configured, output the expected phase and word alignment patterns :

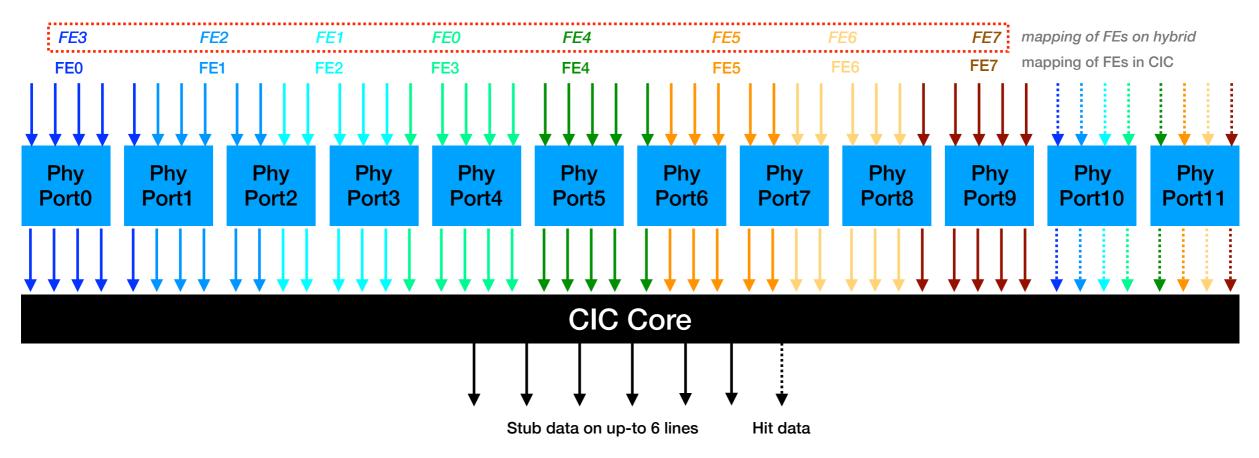

- phase aligner ports 0 9 are used to phase align the (40) stub data lines from the 8 CBCs (5 per CBC) connected to the CIC

- phase aligner ports 10 11 are used to phase align the (8) hit data lines from the 8 CBCs (1 per CBC) connected to the CIC

• Phase alignment patterns on CBCs are generated by setting a low threshold on all 8 CBCs (so all channels always contain a hit) and using the channel masks to generate stubs with addresses and bends that produce this pattern on the stub output lines

- Week of the 15th April spent testing read-out system and performing first checks on the 2S FEH prototype :

- M. Kovacs organized presence of experts for the entire week

- power-up checks on 2S electrical characterization board performed at Bristol the previous week

- experience in operating/working with the CIC courtesy of the stand-alone CIC set-up used for DAQ development

- Goals of the week were to :

- confirm connectivity between 2S electrical characterization board, FC7, and 2S FEH

- ✓ is the CIC receiving the clock and hard reset signals?

- ✓ is the CIC receiving the fast commands?

- ✓ do all chips respond to I2C read and write commands?

- confirm connectivity between CIC mezzanine and 8CBC3.1 hybrid

- $\checkmark$  do the configured CBCs output phase and word alignment patterns ?

- demonstrate that stand-alone CIC initialization sequence can be performed with the 2S FEH

- $\checkmark$  can the complete initialization sequence be performed on the 2S FEH?

- record response to a resync and effect on Bx0

## **CIC** Initialization Sequence

Initialization sequence based on CIC1 power on and initialization guide provided by Lyon : same sequence used for the CIC standalone DAQ tests

CIC Power on Sequence

| Step            | Action                                                           |

|-----------------|------------------------------------------------------------------|

|                 | Enable CIC Alim                                                  |

|                 | Launch the CIC Clock generation @320MHz                          |

|                 | Set the active low CIC Hard Reset to '1'                         |

|                 | increase the dll current                                         |

| Phase Alignment | set the phyport in auto startup mode                             |

|                 | apply a SoftReset                                                |

|                 | release the SoftReset                                            |

|                 | check all dll are correctly locked                               |

| Phase Alignment | Apply signals to the CIC inputs                                  |

| Phase Alignment | Check that all the channels are correctly locked                 |

| FC Locking      | Launch the emission of the FC frame to the CIC                   |

| FC Locking      | Check fc decoder locking state                                   |

| FC Locking      | Send a Resync                                                    |

| FC Locking      | Check fc decoder correctly receive a Resync                      |

| Word Alignment  | Set the pattern you want to use to align each trigger line       |

| Word Alignment  | Disable the using of the external alignment value                |

| Word Alignment  | Ask for the auto alignment                                       |

| Word Alignment  | Resync                                                           |

| Word Alignment  | Send continuously the patterns on every line for each enabled FE |

| Word Alignment  | check if the alignment is correctly done                         |

| Word Alignment  | Deassert the wa request                                          |

| Phase Phase        | e and word alig   | gnment patteri    | ns used in initi  | alization sequ     | ence               |

|--------------------|-------------------|-------------------|-------------------|--------------------|--------------------|

| Pattern            | SLVS1             | SLVS2             | SLVS3             | SLVS4              | SLVS5              |

| phase<br>alignment | <u>0b01010101</u> | <u>0b10101010</u> | 0600000000        | <u>0b1010 1010</u> | 0b1010 0000        |

| phase<br>alignment | 0b10000000        | 0b10000001        | <u>0b10101010</u> | <u>0b1010 1010</u> | <u>0b1010 1010</u> |

| word<br>alignment  | <u>0b01111010</u> | <u>0b10111100</u> | <u>0b11010100</u> | <u>060001 0011</u> | <u>0b1010 0001</u> |

|                    |                   |                   |                   |                    |                    |

#### 1 • • • . • 1• . . DI

- Phase and word alignment steps require configuring the CBCs to generate specific patterns on each of the 6 output lines (5 stubs, 1 hit) ٠

- Patterns produced by lowering threshold and masking all channels but those required to generate stubs/bends/hits corresponding to patterns needed for specific alignment procedure :

- tuning of the data on the hit lines also requires sending L1 triggers to the CBCs; triggers generated internally in the FC7 at 1MHz and back-pressure is disable

- Phase alignment done in three steps; impossible to generate a 10101010 pattern on all 5 stub data lines\* simultaneously

- first on three of the six stub lines (SLVS0, SLVS1, SLVS3 for all CBCs)

- then on another three of six stub lines (SLVS2, SLVS3, SLVS4 for all CBCs)

- then on the last SLVS line containing hit data( SLVS5 for all CBCs )

- Word alignment done in one step on the 5 stub data lines (SLVS0, SLVS1, SLVS2, SLVS3, SLVS4)

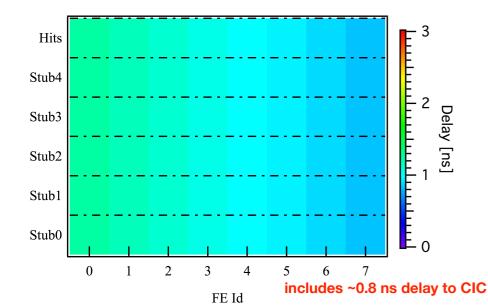

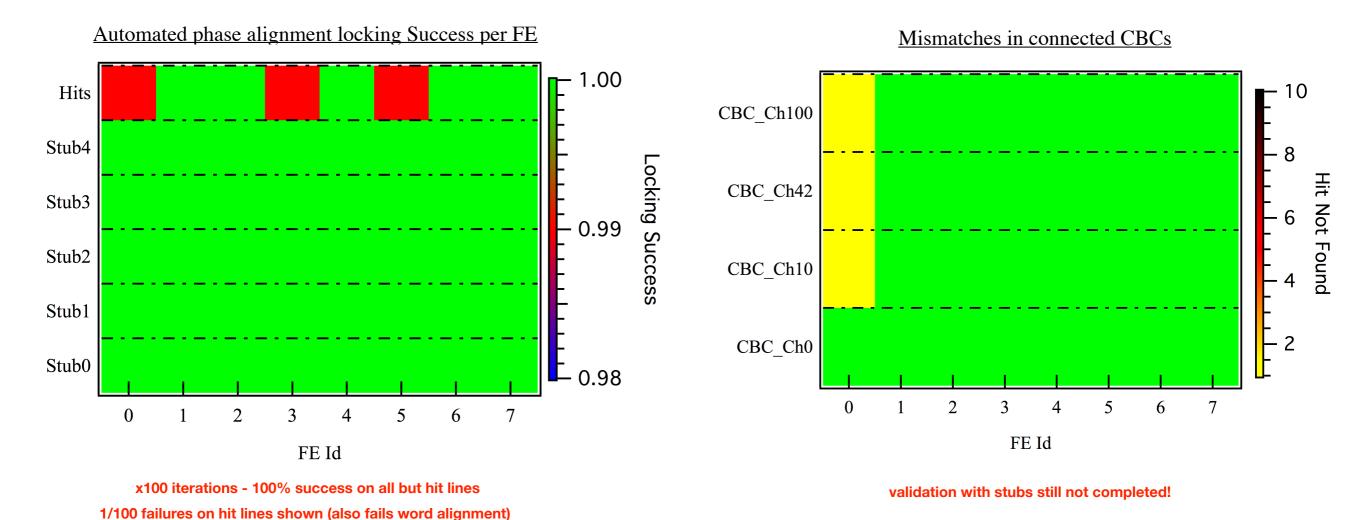

#### CIC Initialization Sequence : Phase alignment on hit and stub data lines

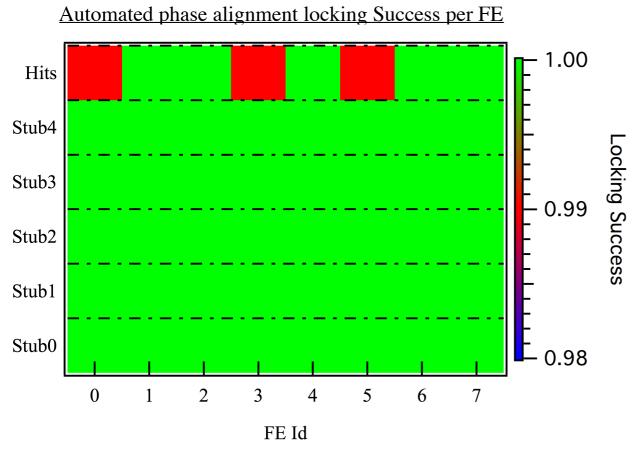

- Execute CIC initialization sequence and request CIC to identify phase on 8x6 SLVS lines from CBCs with the phase aligner running in autostartup mode

- Perform phase alignment sequence and check that all channels locked correctly (read-back I2C registers from CIC) :

- the stub data lines from the CBCs preceded by configuring CBCs so that phase alignment pattern appears on 3 lines at a time

- the hit data lines from the CBCs preceded by configuring CBCs so that phase alignment pattern appears in hit data

- allow 1 s for automated phase aligner block to run

x100 iterations - 100% success on all but hit lines 1/100 failures on hit lines shown (also fails word alignment)

7

#### 8

#### Checking data post CIC initialization sequence using a given hit pattern [ all channels except for 0, 10, 42 and , 100 masked ]

- configure CBCs to continuously output a specific hit pattern (CIC outputting unsparsified CBC data)

- read-back and decode CIC hit (L1) data and check for any mismatches

## CIC Initialization Sequence : Data quality check after phase alignment (hits only)

- Execute CIC initialization sequence and request CIC to identify phase on 8x6 SLVS lines from CBCs with the phase aligner running in autostartup mode

- Perform phase alignment sequence and check that all channels locked correctly (read-back I2C registers from CIC) :

- the stub data lines from the CBCs preceded by configuring CBCs so that phase alignment pattern appears on 3 lines at a time

- the hit data lines from the CBCs preceded by configuring CBCs so that phase alignment pattern appears in hit data

- allow 1 s for automated phase aligner block to run

- Week of the 15th April spent testing read-out system and performing first checks on the 2S FEH prototype :

- M. Kovacs organized presence of experts for the entire week

- power-up checks on 2S electrical characterization board performed at Bristol the previous week

- experience in operating/working with the CIC courtesy of the stand-alone CIC set-up used for DAQ development

- Goals of the week were to :

9

- → confirm connectivity between 2S electrical characterization board, FC7, and 2S FEH

- ✓ is the CIC receiving the clock and hard reset signals?

- ✓ is the CIC receiving the fast commands?

- ✓ do all chips respond to I2C read and write commands?

- confirm connectivity between CIC mezzanine and 8CBC3.1 hybrid

- ✓ do the configured CBCs output phase and word alignment patterns ?

- demonstrate that stand-alone CIC initialization sequence can be performed with the 2S FEH

- $\checkmark$  can the complete initialization sequence be performed on the 2S FEH?

- · demonstrate that FE ASICs (CBCs) on hybrid can be configured correctly for data taking

- ✓ can we measure the pedestal and noise on all 8 ASICs on the hybrid?

- confirm validity of the automated BX0 identification in the CIC

- ✓ use automated BX0 identification in CIC to measure the delay (in 40 MHz clock cycles) between the reception of a resync (fast reset) and the reception of the first data packet with a predefined pattern

- ✓ record response of all 8 CBCs on hybrid to a fast reset (Resync)

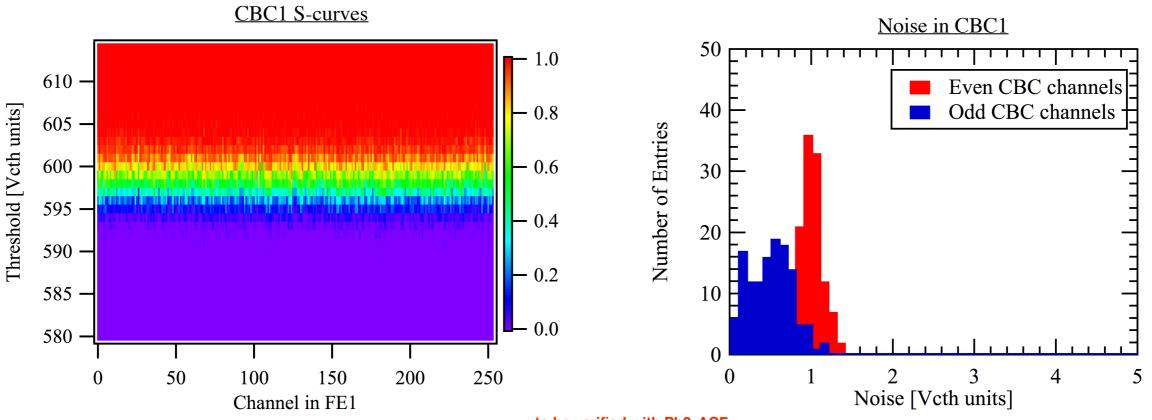

## Equalize response of CBCs : offset tuning and pedestal/noise measurement

- Ensure that CBCs are tuned correctly (uniform response across all channels )

- configure CIC to output CBC hit data in unsparsified mode

- triggering and event generation using standard  $\mu$ DTC firmware (internal trigger generation + DDR3 readout )

to be verified with Ph2\_ACF

#### Generic L1A chip event format (µDTC)

|   | 31 | 30 | 29 | 28 | 27 | 26    | 25   | 24 | 23 | 22 | 21 | 20   | 19    | 18 | 17     | 16     | 15   | 14   | 13   | 12 | 11 | 10 | 9 | 8       | 7      | 6       | 5      | 4       | 3     | 2 | 1 | 0 |

|---|----|----|----|----|----|-------|------|----|----|----|----|------|-------|----|--------|--------|------|------|------|----|----|----|---|---------|--------|---------|--------|---------|-------|---|---|---|

| 0 | 1  | 0  | 1  | 0  |    | Error | Code |    |    |    |    | Hybr | id ID |    |        |        |      | Chi  | DID  |    |    |    | Т | otal L1 | IA Dat | ta Size | e (128 | Bbit wo | ords) |   |   |   |

| 1 |    |    |    |    |    |       |      |    |    |    |    |      |       |    |        |        |      | Chip | Туре |    |    |    |   | Frame   | e Dela | ıy (Tin | neout  | Count   | ter)  |   |   |   |

| 2 |    |    |    |    |    |       |      |    |    |    |    |      |       | С  | hip He | ader S | oace |      |      |    |    |    |   |         |        |         |        |         |       |   |   |   |

| 3 | D  | D  | D  | D  | D  | D     | D    | D  | D  | D  | D  | D    | D     | D  | D      | D      | D    | D    | D    | D  | D  | D  | D | D       | D      | D       | D      | D       | D     | D | D | D |

| 4 | D  | D  | D  | D  | D  | D     | D    | D  | D  | D  | D  | D    | D     | D  | D      | D      | D    | D    | D    | D  | D  | D  | D | D       | D      | D       | D      | D       | D     | D | D | D |

|   |    |    |    |    |    |       |      |    |    |    |    |      |       |    |        |        |      |      |      |    |    |    |   |         |        |         |        |         |       |   |   |   |

|   | D  | D  | D  | D  | D  | D     | D    | D  | D  | D  | D  | D    | D     | D  | D      | D      | D    | D    | D    | D  | D  | D  | D | D       | D      | D       | D      | D       | D     | D | D | D |

|   | D  | D  | D  | D  | D  | D     | D    | D  | D  | D  | D  | D    | D     | D  | D      | D      | D    | D    | D    | D  | D  | D  | D | D       | D      | D       | D      | D       | D     | D | D | D |

- Week of the 15th April spent testing read-out system and performing first checks on the 2S FEH prototype :

- M. Kovacs organized presence of experts for the entire week

- power-up checks on 2S electrical characterization board performed at Bristol the previous week

- experience in operating/working with the CIC courtesy of the stand-alone CIC set-up used for DAQ development

- Goals of the week were to :

- ▶ confirm connectivity between 2S electrical characterization board, FC7, and 2S FEH

- ✓ is the CIC receiving the clock and hard reset signals?

- ✓ is the CIC receiving the fast commands?

- ✓ do all chips respond to I2C read and write commands?

- confirm connectivity between CIC mezzanine and 8CBC3.1 hybrid

- ✓ do the configured CBCs output phase and word alignment patterns ?

- demonstrate that stand-alone CIC initialization sequence can be performed with the 2S FEH

- $\checkmark$  can the complete initialization sequence be performed on the 2S FEH?

- confirm validity of the automated BX0 identification in the CIC

- ✓ use automated BX0 identification in CIC to measure the delay (in 40 MHz clock cycles) between the reception of a resync (fast reset) and the reception of the first data packet with a predefined pattern

- ✓ record response of all 8 CBCs on hybrid to a fast reset (Resync)

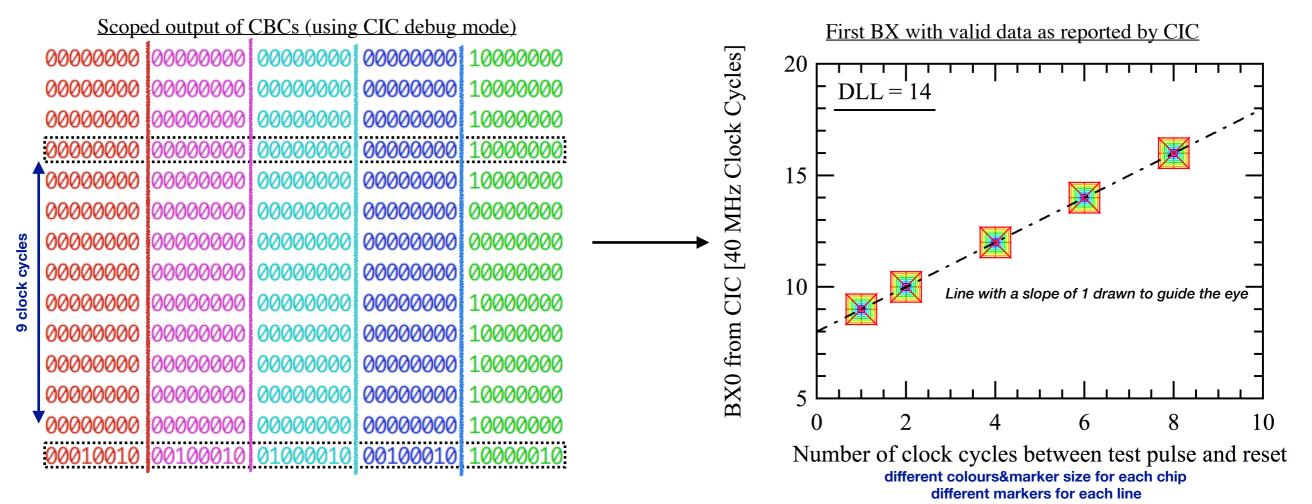

# **2S FEH prototype (CBC3.1 + CIC)** CIC BX0 alignment Sequence

BX0 alignment sequence based on CIC1 power on and initialization guide provided by Lyon : same sequence used for the CIC standalone DAQ tests

#### CIC BX0 Alignment Sequence

|              |                                                       | - |               |            |            |            |            |            |

|--------------|-------------------------------------------------------|---|---------------|------------|------------|------------|------------|------------|

| x0 Alignment | Chose the trigger line used to perform this alignment | I |               |            |            |            |            |            |

| x0 Alignment | Disable the using of the external alignment value     | I | Pattern       | SLVS1      | SLVS2      | SLVS3      | SLVS4      | SLVS5      |

| x0 Alignment | Ask for the auto alignment                            | I | I attern      |            |            |            |            |            |

| x0 Alignment | Resync                                                | I |               |            |            |            |            |            |

| x0 Alignment | FE chip send the recognizable pattern                 | I |               |            |            |            |            |            |

| x0 Alignment | check if the alignment is correctly done              | I | bx0 alignment | 0b00010010 | 0b00100010 | 0b01000010 | 0b00100010 | 0b1000001( |

| x0 Alignment | Deassert the auto Bx0 request                         | 1 | i i           |            |            |            |            |            |

|              |                                                       |   |               |            |            |            |            |            |

- BX0 alignment require configuring the CBCs to generate specific patterns on **any** of the 5 stub lines :

- line to perform alignment on configurable in CIC

- Require pattern to appear in exactly one bunch crossing (to avoid any ambiguity in the measurement); therefore patterns are produced in a slightly different way than the other alignment procedures :

- on-chip test pulse used to generate hits in channels belonging to a specific group of channels in each of the 8 CBCs

- channel masks used to generate stubs with seed positions and bends that match the alignment pattern on each of the 5 stub data lines

- a dedicated triggering finite-state-machine in the uDTC is used to generate triggers that consists of :

- a fast reset (fast command recognized by the CBC and the CIC) a wait for N clock cycles

- a test pulse trigger (fast command recognized by the CBCs); this initializes a test pulse from the on-chip test pulse generator circuit

- a wait for M clock cycles

- an L1A/trigger (fast command recognized by the CBC and the CIC)

Bx0 Bx0 Bx0 Bx0 Bx0 Bx0

# CMS

Patterns used in BX0 alignment sequence

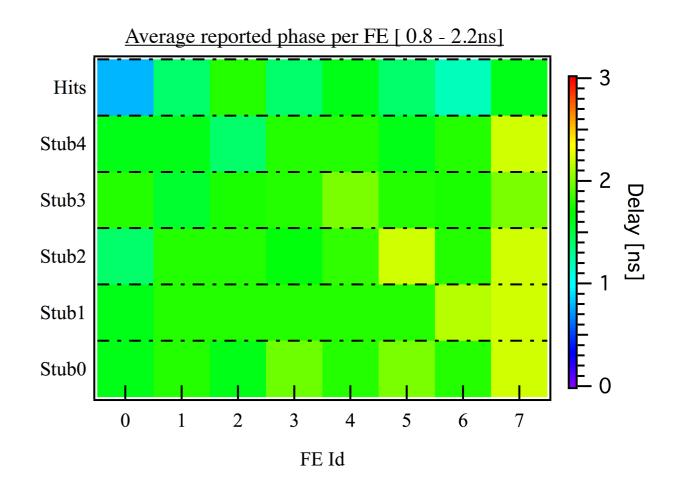

#### CIC BX0 alignment Sequence : confirm uniform response across hybrid

BX0 alignment sequence based on CIC1 power on and initialization guide provided by Lyon : same sequence used for the CIC standalone DAQ tests

#### CIC BX0 Alignment Sequence

| Patterns | used i | n BX0 | alignment | sequence |

|----------|--------|-------|-----------|----------|

|          |        |       | 0         | 1        |

| <b>Bx0</b> Alignment | Chose the trigger line used to perform this alignment | 1 |               |            |            |            |            |            |

|----------------------|-------------------------------------------------------|---|---------------|------------|------------|------------|------------|------------|

| <b>Bx0</b> Alignment | Disable the using of the external alignment value     | 1 | Pattern       | SLVS1      | SLVS2      | SLVS3      | SLVS4      | SLVS5      |

| Bx0 Alignment        | Ask for the auto alignment                            | 1 |               |            |            |            |            |            |

| <b>Bx0</b> Alignment | Resync                                                | 1 |               |            |            |            |            |            |

| <b>Bx0</b> Alignment | FE chip send the recognizable pattern                 | I |               |            |            |            |            |            |

| Bx0 Alignment        | check if the alignment is correctly done              | 1 | bx0 alignment | 0b00010010 | 0b00100010 | 0b01000010 | 0b00100010 | 0b10000010 |

| <b>Bx0</b> Alignment | Deassert the auto Bx0 request                         | 1 | ii            |            |            |            | i i        |            |

• CBCs configured to generate BX0 alignment pattern on each of the SLVS lines in turn

#### Scoped output of CBCs (using CIC debug mode)

|              | -        | · • •    |          | e e      | -        |

|--------------|----------|----------|----------|----------|----------|

|              | 00000000 | 00000000 | 00000000 | 00000000 | 10000000 |

|              | 00000000 | 00000000 | 00000000 | 00000000 | 10000000 |

|              | 00000000 | 00000000 | 00000000 | 00000000 | 10000000 |

|              | 00000000 | 00000000 | 00000000 | 00000000 | 10000000 |

|              | 00000000 | 00000000 | 00000000 | 00000000 | 10000000 |

|              | 00000000 | 00000000 | 00000000 | 00000000 | 00000000 |

| sel          | 00000000 | 00000000 | 00000000 | 00000000 | 00000000 |

| ¢ cyo        | 00000000 | 00000000 | 00000000 | 00000000 | 00000000 |

| clock cycles | 00000000 | 00000000 | 00000000 | 00000000 | 10000000 |

| 0            | 00000000 | 00000000 | 00000000 | 00000000 | 10000000 |

|              | 00000000 | 00000000 | 00000000 | 00000000 | 10000000 |

|              | 00000000 | 00000000 | 00000000 | 00000000 | 10000000 |

|              | 00000000 | 00000000 | 00000000 | 00000000 | 10000000 |

|              | 00010010 | 00100010 | 01000010 | 00100010 | 10000010 |

|              |          | - '      |          |          | 1        |

CIC BX0 alignment Sequence : confirm uniform response across hybrid

BX0 alignment sequence based on CIC1 power on and initialization guide provided by Lyon : same sequence used for the CIC standalone DAQ tests

#### CIC BX0 Alignment Sequence

| <b>Bx0</b> Alignment | Chose the trigger line used to perform this alignment |            |

|----------------------|-------------------------------------------------------|------------|

| Bx0 Alignment        | Disable the using of the external alignment value     | Patteri    |

| Bx0 Alignment        | Ask for the auto alignment                            |            |

| <b>Bx0</b> Alignment | Resync                                                |            |

| <b>Bx0</b> Alignment | FE chip send the recognizable pattern                 |            |

| <b>Bx0</b> Alignment | check if the alignment is correctly done              | bx0 alignn |

| Bx0 Alignment        | Deassert the auto Bx0 request                         |            |

|                      |                                                       |            |

#### Patterns used in BX0 alignment sequence

|         | 0500010010 | 0600100010 | 0601000010 | 0500100010 | 0b10000010 |

|---------|------------|------------|------------|------------|------------|

| Pattern | SLVS1      | SLVS2      | SLVS3      | SLVS4      | SLVS5      |

- CBCs configured to generate BX0 alignment pattern on each of the SLVS lines in turn

- Delay (in 40 MHz clock cycles) measured by the CIC recorded for all CBCs and SLVS lines:

- delay is the same for all lines on a hybrid (for a given DLL setting)

- delay varies as the time between the fast resync and the injected pattern is varied (time between resync and test pulse trigger)

- Perform data quality checks on stub data ( similar to what was done for hit data)

- Use set-up to further investigate response of FE ASCICs to fast commands (resyncs , orbit resets, etc.)

- Repeat tests on all available hybrids

- And a lot more ...

Back-up

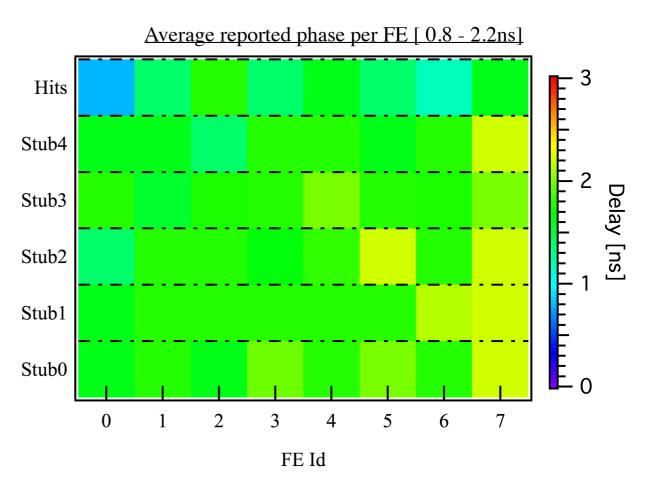

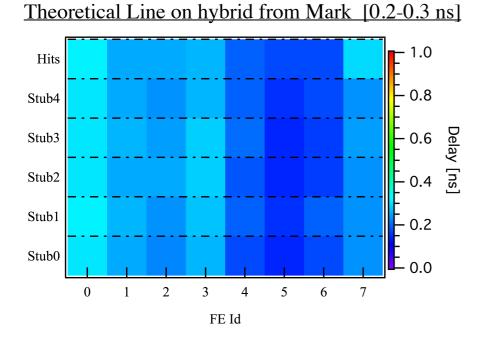

#### CIC Initialization Sequence [comparison with theoretical calculations]

- Execute CIC initialization sequence and request CIC to identify phase on 8x6 SLVS lines from CBCs with the phase aligner running in auto-startup mode

- Perform phase alignment sequence and check that all channels locked correctly (read-back I2C registers from CIC) :

- the stub data lines from the CBCs preceded by configuring CBCs so that phase alignment pattern appears on 3 lines at a time

- the hit data lines from the CBCs preceded by configuring CBCs so that phase alignment pattern appears in hit data

- allow 1 s for automated phase aligner block to run

•

17

Theoretical clock delays on hybrid from Mark [0.84-1.25ns]