## CBC3 Hit Detect Logic for CMSSW

E.Migliore Università di Torino/INFN

## Introduction

- A parametrization of CBC3 signal shape

- it was determined in the lab by S.S. El Nasr-Storey, S. Mersi, G. Zevi Della Porta et al. (talk)

- it was implemented in CMSSW by S. Dutta and S.Sarkar (talk) Input to signal shape are:

- deposited charge

- particle time of flight corrected for the time required to reach the module (reference: center of the module)

- A realistic simulation of CBC3 must implement Hit Detect Logic. This talk is an attempt to document "our" interpretation of the Hit Detect Logic described in the CBC3 manual in view of the implementation in CMSSW code (class SSDigitizerAlgorithm)

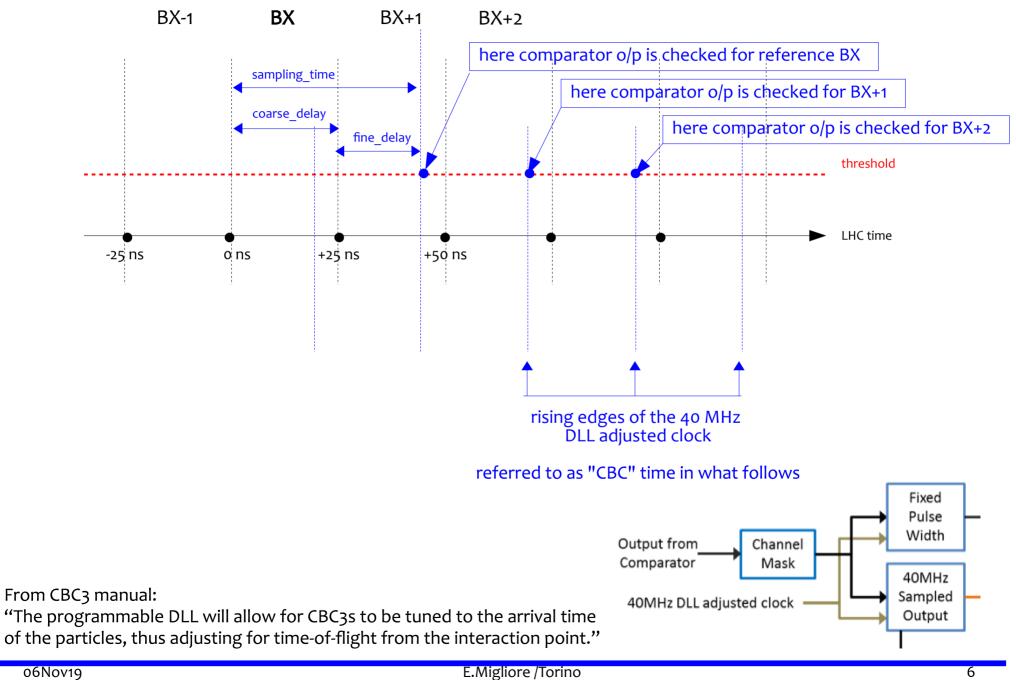

## **CBC3 Hit Detect Logic**

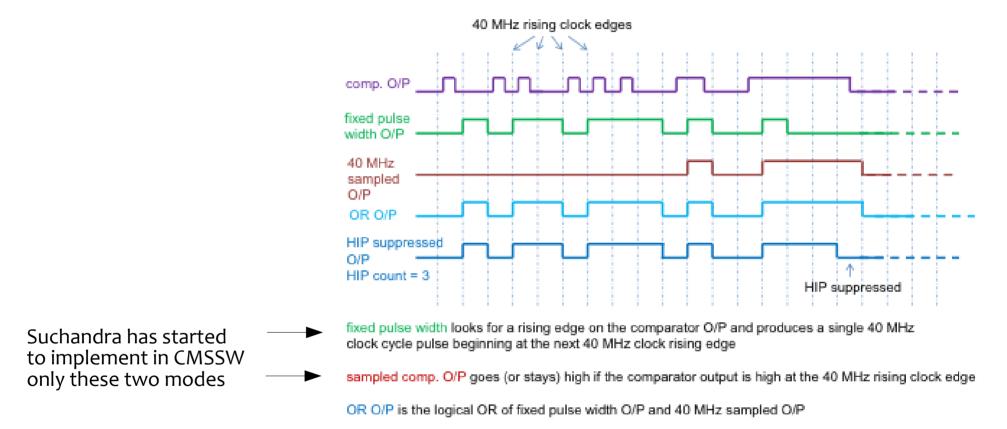

• From CBC3 technical specs manual

- In the following I will adopt the following (short) name conventions:

- fixed pulse width => latched mode

- 40 MHz sampled comp. O/P => sampled mode

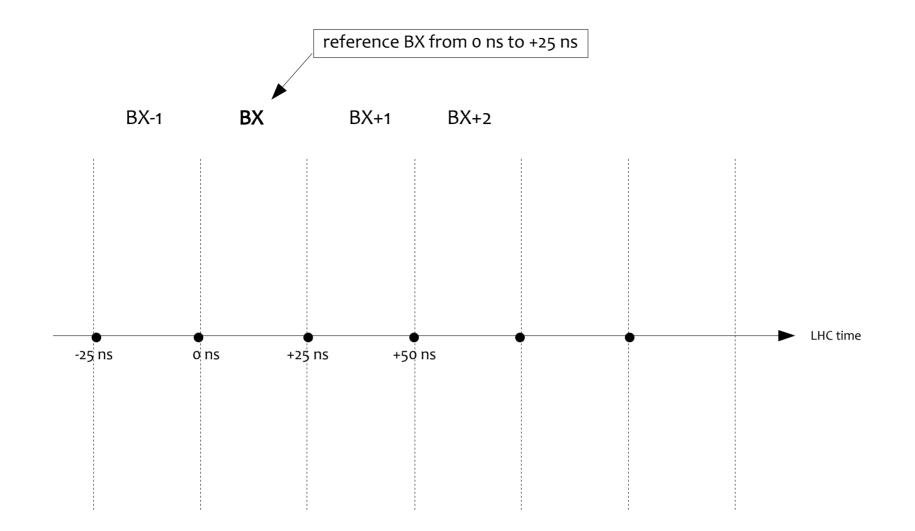

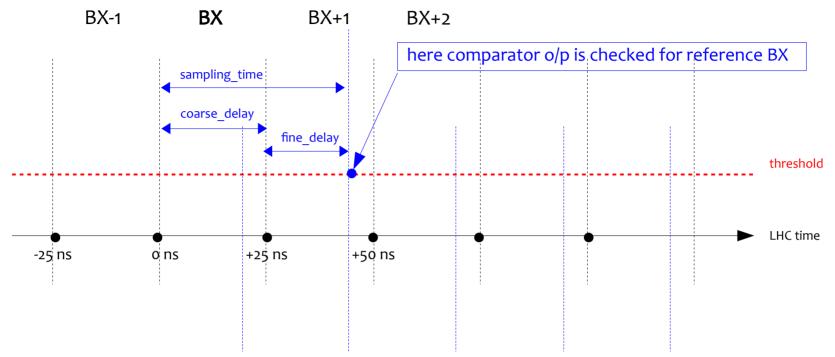

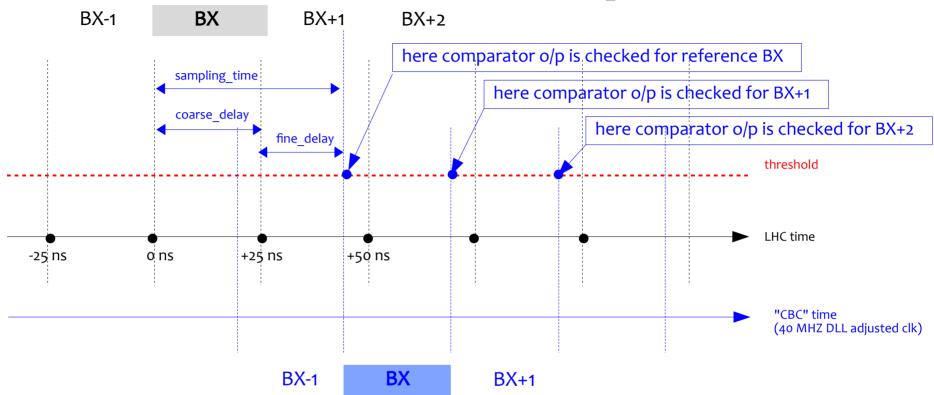

sampling\_time = coarse\_delay + fine\_delay

with coarse\_delay is in 25 ns steps and fine\_delay is in 1 ns steps

sampling\_time = coarse\_delay + fine\_delay

with coarse\_delay is in 25 ns steps and fine\_delay is in 1 ns steps

sampling\_time = coarse\_delay + fine\_delay

with coarse\_delay is in 25 ns steps and fine\_delay is in 1 ns steps

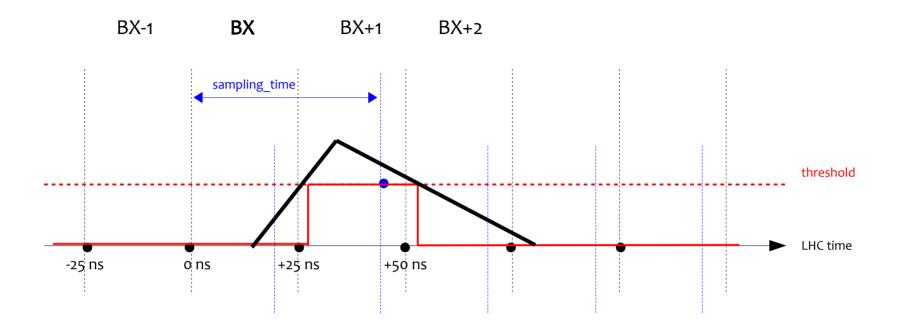

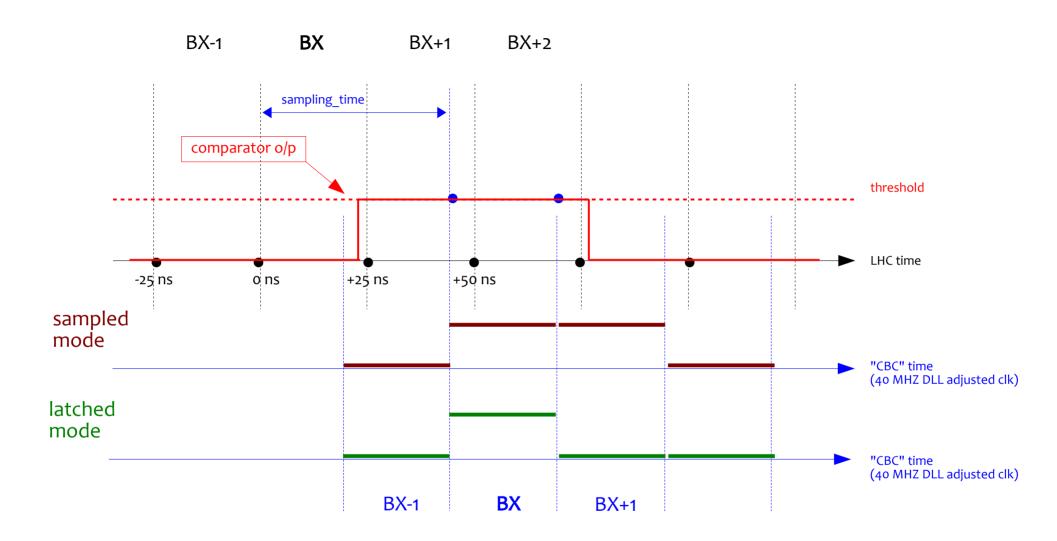

particle crossing sensor during reference BX: case A

- Disclaimer

- "triangular" signal shape

- choice of the sampling time

in the sketch are just for illustration purpose

particle crossing sensor during reference BX: case A

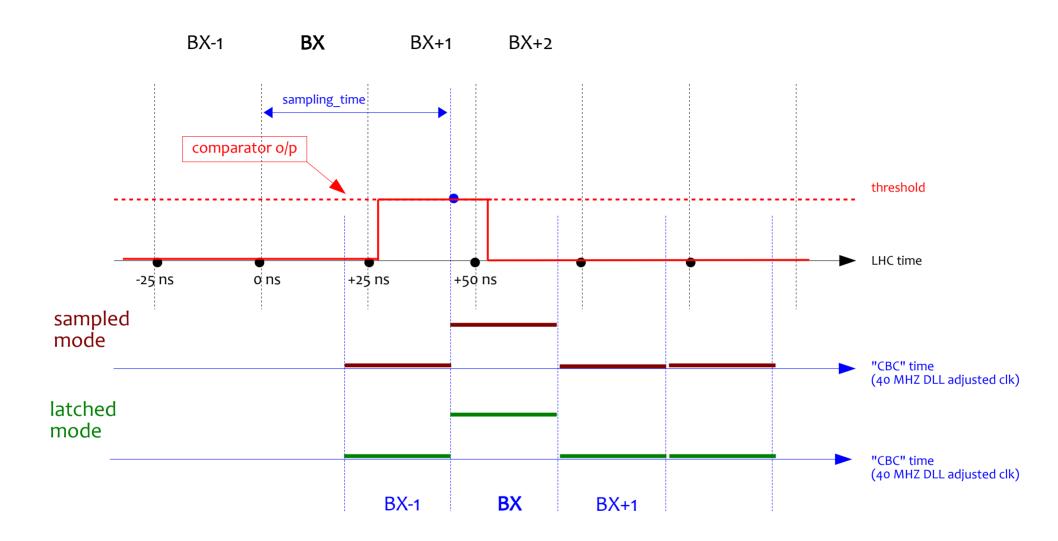

sampled mode: high if comp. o/p is high at the rising edge of the 40 MHz clock

latched mode: looks for a rising edge on comp. o/p and produces a 25 ns pulse beginning at the next 40 MHz clock rising edge

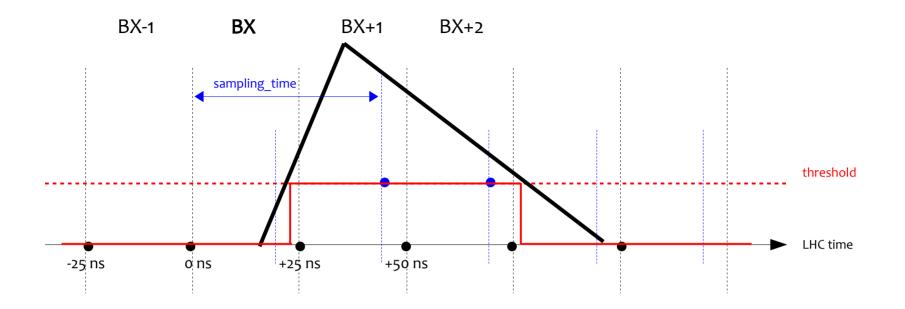

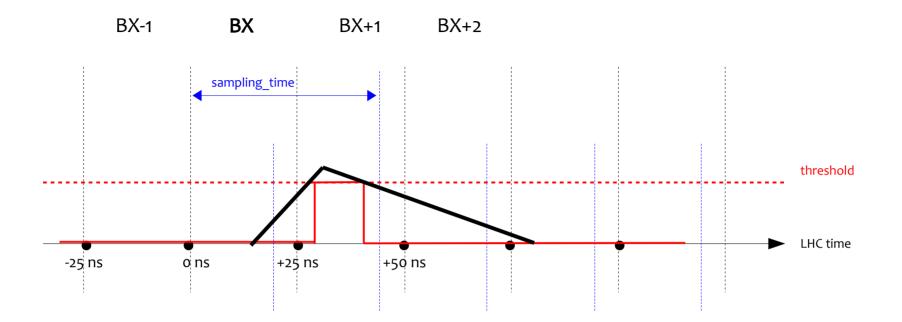

particle crossing sensor during reference BX: case B

particle crossing sensor during reference BX: case B

sampled mode: high if comp. o/p is high at the rising edge of the 40 MHz clock

latched mode: looks for a rising edge on comp. o/p and produces a 25 ns pulse beginning at the next 40 MHz clock rising edge

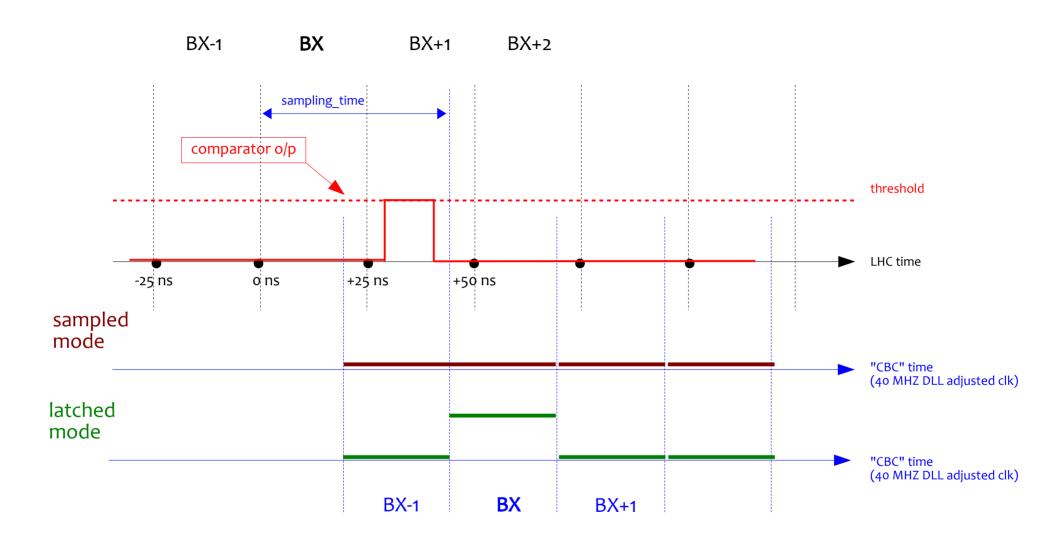

particle crossing sensor during reference BX: case C

particle crossing sensor during reference BX: case C

sampled mode: high if comp. o/p is high at the rising edge of the 40 MHz clock

latched mode: looks for a rising edge on comp. o/p and produces a 25 ns pulse beginning at the next 40 MHz clock rising edge

• Is this interpretation correct?