# **CMS Binary Chip status**

#### Outline

intro & current status brief reminder of architecture, specs and simulated performance layout pictures testing plans future developments summary

# introduction

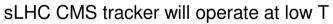

- CBC targeted at phase II outer tracker region  $r > \sim 50 \text{ cm}$

- assumed instrumented by short strips  $\sim 2.5\,/\,5~\text{cm}$

assumed not contributing to L1 trigger separate development for PT layers

#### environment

- ~ -30 -> -40 degrees

- => important to meet specs at low temperatures

- (but will still want to test and run chips and modules at room temperatures)

chip design begun March 2009 in 130nm IBM CMOS Lawrence Jones (RAL engineer)

### current status

MPW data to IBM this week

=> chips back ~ October

CBC design transmission to CERN was delayed by ~ 1 month, to 5<sup>th</sup> July

extra time needed to finish layout, top-level simulation, final design review, ...

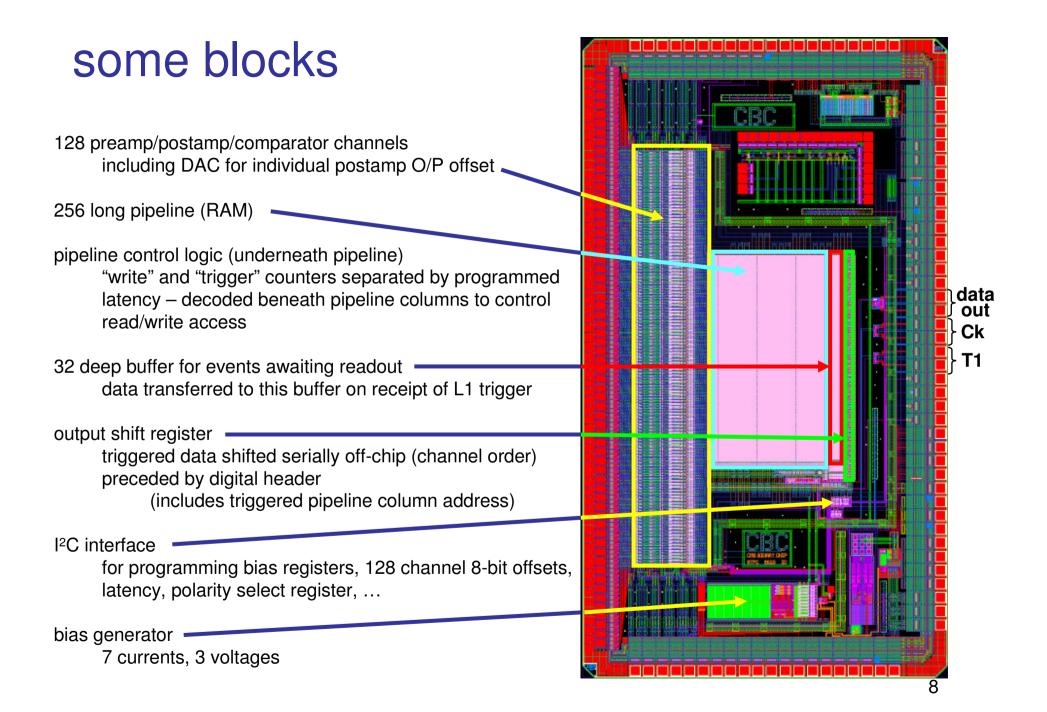

# **CBC** architecture

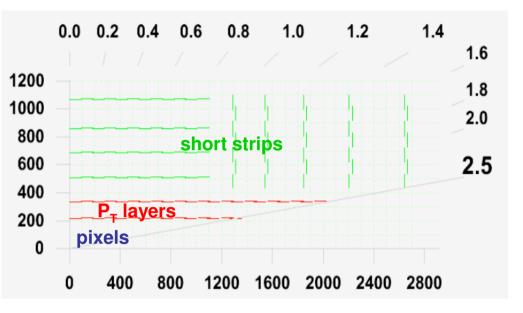

binary un-sparsified architecture simplicity/robustness, lowest power

#### main functional blocks

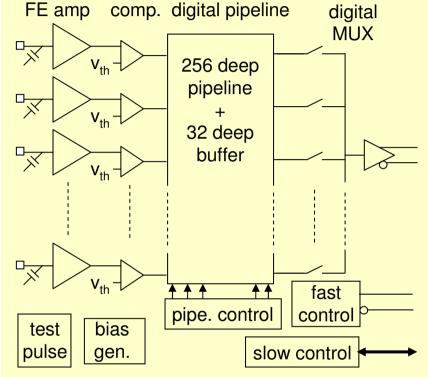

- fast front end amplifier 20 nsec peaking

- comp. with individually programmable threshold

- 256 deep pipeline (6.4 us)

- 32 deep buffer for triggered events

- output mux and driver (SLVS)

- fast (SLVS) and slow (I2C) control interfaces

#### some target specs (see \* for full list)

- both signal polarities

- DC coupled to sensor up to 1 uA leakage

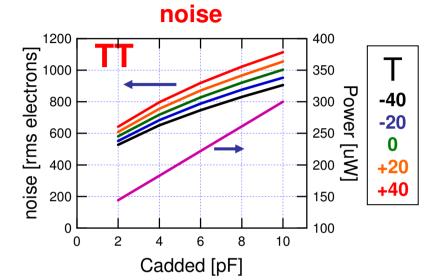

- noise: < 1000e for  $C_{SENSOR}$  ~5 pF

- power consumption

- < 0.5 mW/channel for  $C_{\rm SENSOR} \sim 5 \ \text{pF}$

\* http://icva.hep.ph.ic.ac.uk/~dmray/CBC\_documentation/CBC\_specifications.pdf

will show just simulated pulse shape and noise performance for much more detail see design review talk:

http://icva.hep.ph.ic.ac.uk/~dmray/CBC\_documentation/frontend\_design\_review\_Oct\_09.pdf

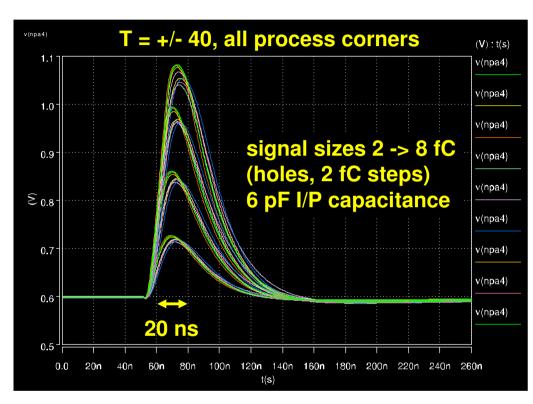

### postamp output pulse shape & noise

$\sim$  20 nsec peaking,  $\sim$  50 mV / fC robust to temperature (-40 -> +40) and process variations electron signal gives opposite polarity

preamp input device power varied with Cadded (added input capacitance) to maintain constant pulse shape

(otherwise preamp risetime increases with Cadded and overall pulse shape affected)

for 1 uA leakage current add 440e in quadrature

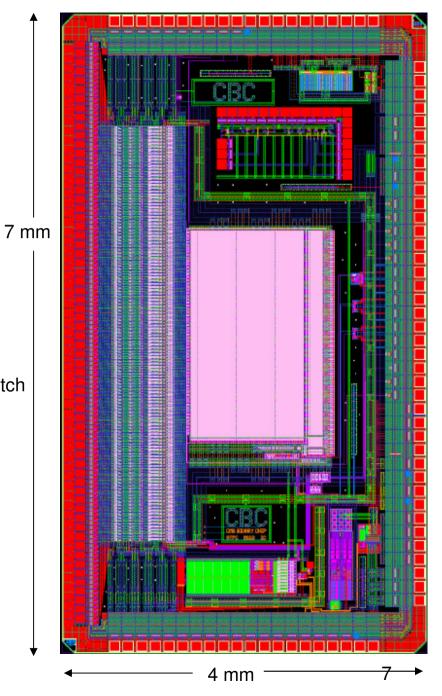

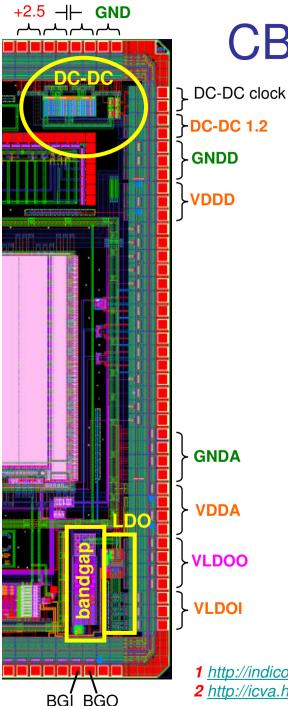

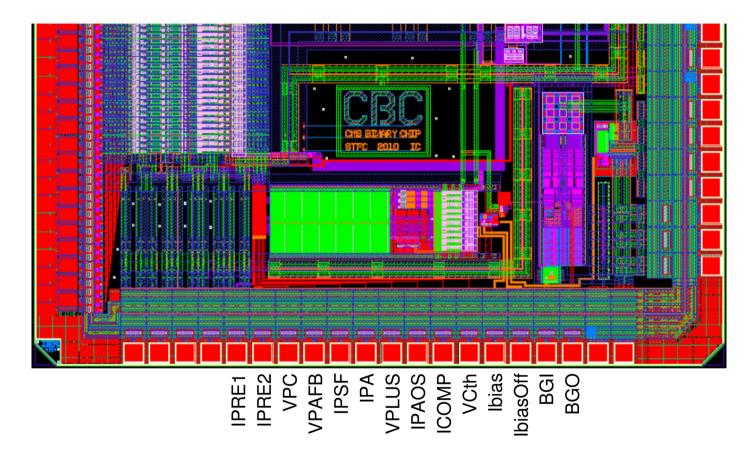

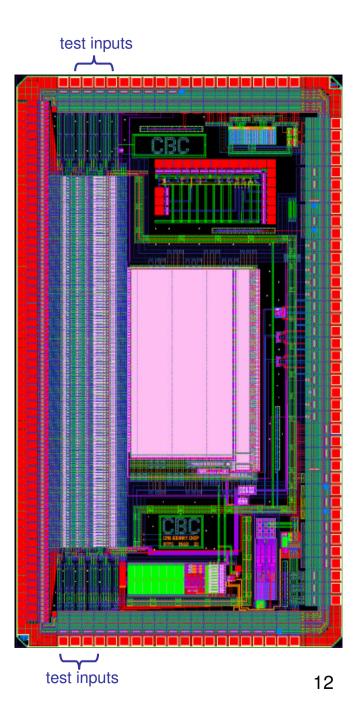

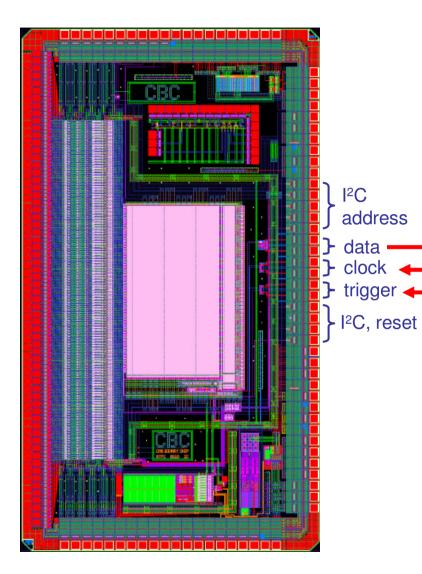

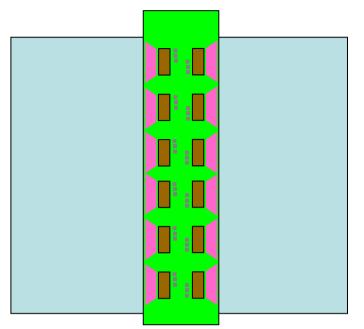

## layout

actual submission size 7 x 4 mm<sup>2</sup>

for MPW dicing reasons – 7 x 3.5 possible

input pads on 50 um pitch

2 staggered rows on 100 um pitch

note: no power pads on front edge

all other pads (top, bottom, right hand side) on 150 um pitch

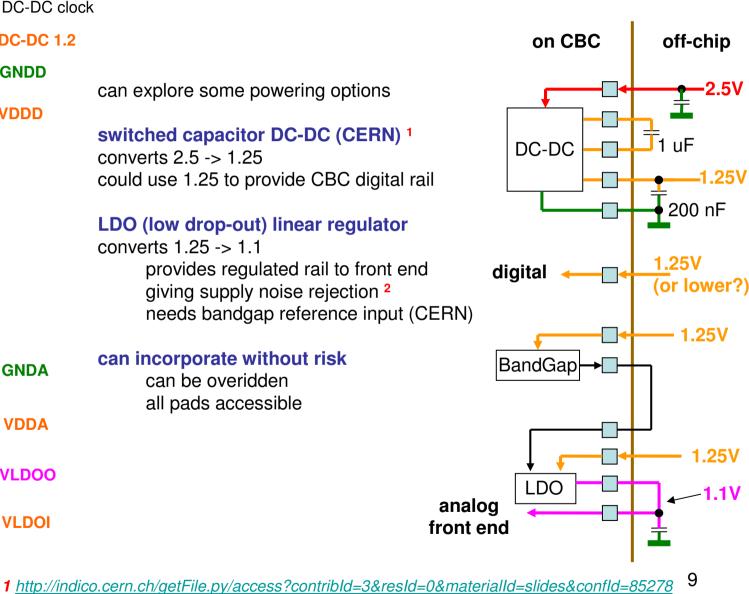

# **CBC** powering options

2 http://icva.hep.ph.ic.ac.uk/~dmray/CBC documentation/LDO PWG Sep09.pdf

# test features (1)

## test features (2)

access to all bias generator outputs to allow study/fault diagnosis/overide

## test pulse

no time to implement complex circuit

e.g. DLL based charge injection to allow to sweep time of charge injection

(but expect to include in future version)

just 8 pads, each one connected to 16 channels though small capacitor

allows to quickly verify functionality of all channels

# running the chip

procedure very similar to APV

I<sup>2</sup>C for programming operational state bias values, channel offsets, polarity, latency,...

SLVS fast control signals 40 MHz clock trigger line single 1 => L1 trigger 101 => fast reset (reset101 like APV)

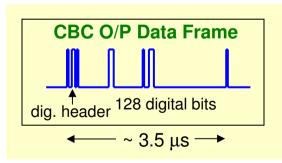

output frame at 40 Mbps (no other bit-rate available on this version)

#### testing plans ... only just begun thinking about this test channel interface at IC will want to verify detailed chip functionality and performance CBC will probably make something like this signals direct fineline chip carrier board (chip + capacitors only) & charge + interface boards for signals and power power injection interface may need different versions to test different functionalities e.g. with/without different powering options bias gen. test for DAQ can use old APV system - VME based/Labview interface

CERN VI2C card for I2C digital pattern generator to provide clock/trigger ADC to acquire output data (even though just binary)

### **Bristol plans**

will focus on module and system tests using daughter board on FPGA development platform

see talk by David Cussans (16<sup>th</sup> June 2010 Power Working Group) http://indico.cern.ch/getFile.py/access?contribId=3&resId=0&materialId=slides&confId=97972

# future chip developments (1)

CBC prototype designed to be complete working readout chip but some system functionalities not yet present

system aspects have been discussed in TUPO meetings

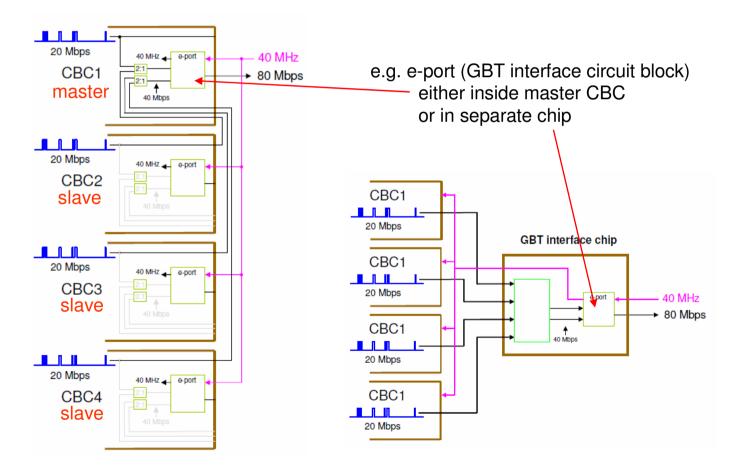

e.g. how to combine data and interface to GBT discussions will continue, but more than one viable option exists

## future chip developments (2)

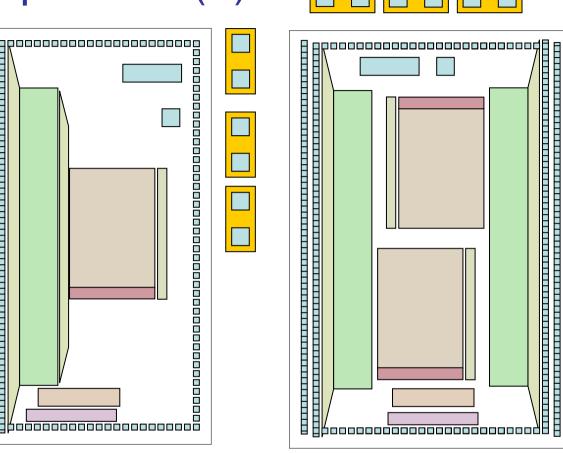

#### 128 -> 256 back-to-back

can share some functionality e.g. power, control but not much else

reduced area, cheaper

less pads available on 256 version

less flexible

overall power consumption probably not much different

#### conclusions

256 back-to-back probably not impossible

but more detailed study may yet reveal difficulties

e.g. hard to see where DC-DC conversion can fit without causing problems (interference & room for external capacitors)

ö

0201 capacitors

# future chip developments (3)

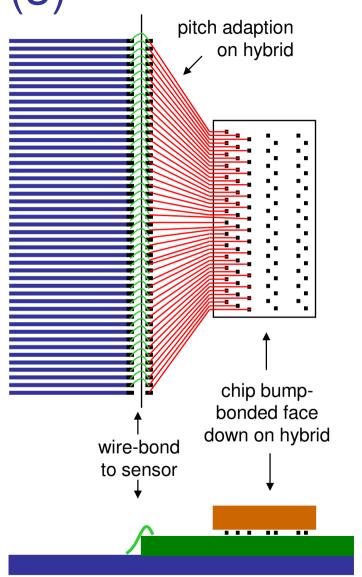

#### bump-bonding?

removes 1/2 of the wire-bonds pitch adaption on hybrid

significant changes to layout hybrid & wire-bond to sensor still required else where to put passives, route power, ...

### summary

CBC prototype designed to be complete working readout chip functionality and performance issues to study noise, power, powering, radiation (SEE),.... useful information for future chip and system developments

some system functionalities not yet present but current design compatible with future anticipated options

chips expected back in October

detailed documentation under development will appear eventually on: <u>http://icva.hep.ph.ic.ac.uk/~dmray/CBC\_documentation/</u>

plans for testing underway

will concentrate initially on detailed functionality and performance at IC Bristol looking at module and system test stand

future developments

some system options need to converge (GBT interface) need to study and make decisions on alternative layouts 256 back-to-back, bump-bonding

### **EXTRA**

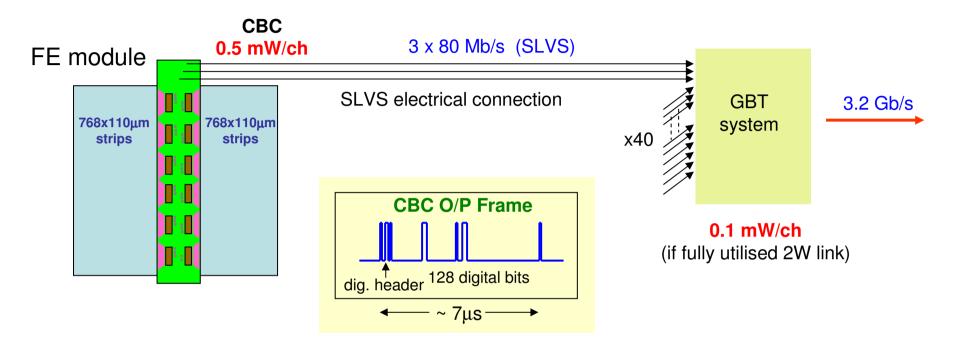

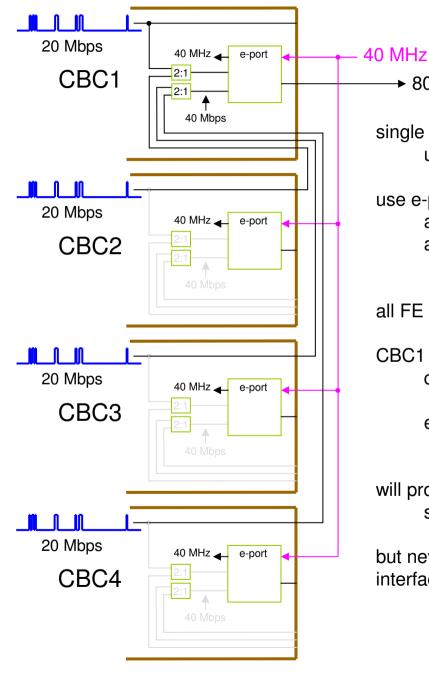

## sLHC strips readout system

binary unsparsified output frame format similar to APV (just hits, not analog values)

keep data frame ~7  $\mu$ s (must be less than average L1 separation)

- => 128 channel CBC provides output data at 20 Mbps

- => 4 CBCs data combined onto one 80 Mbps link to GBT input

plan to use GBT e-link (e-port IP block in chip) takes care of data transfer synchronization

but not on this CBC version

## module concepts

#### hybrid, bonding, PA issues

CBC prototype uses "conventional" layout

128 channels, effective pitch 50 um, wire-bondable no special test setup preparations & generally easier to test

but 50  $\mu m$  not well matched to sensor pitch ~ 100  $\mu m$

=> pitch adaption somewhere - where?

(would like to avoid separate PA's in future system)

hybrid? - possible but uses space for fanout

would help if CBC input pad pitch better matched to sensor  $\sim$  100 um pitch

#### other issues

would module design benefit from 256 (2 x 128 channels back-to-back)? (not impossible - but detailed study may yet reveal difficulties) should we be looking at bump-bonding for chip/hybrid/sensor connection?

=> a number of issues to re-examine for a subsequent iteration

### combining chips output data using CERN e-port IP core

► 80 Mbps

single lines shown outside chips but assume all differential SLVS using CERN SLVS interface driver/receiver

use e-port (e-link) to communicate with GBT (CERN IP core) automatically takes care of synchronization also has receive data path but we will probably not use (plan to use I<sup>2</sup>C bus for slow control)

all FE chips produce 20 Mbps output data frame

CBC1 programmed to be master combines pairs of CBC data streams into 2 x 40 Mbps (compatible with e-port requirements) e-port combines 40 Mbps streams to produce 80 Mbps

will probably not implement e-port in CBC May '10 submission some aspects still under development

but nevertheless a clear route to provide the CBC->GBT system interface in the future

### alternative scheme

put e-port in separate GBT interface chip

CBC1 another chip on hybrid but could offer some future flexibility . . . an option to consider in the future 20 Mbps **GBT** interface chip CBC1 20 Mbps 40 MHz e-port ✤ 80 Mbps CBC1 ♠ 40 Mbps **n** n **n** 20 Mbps CBC1 20 Mbps

incorporates circuitry to combine CBC data streams

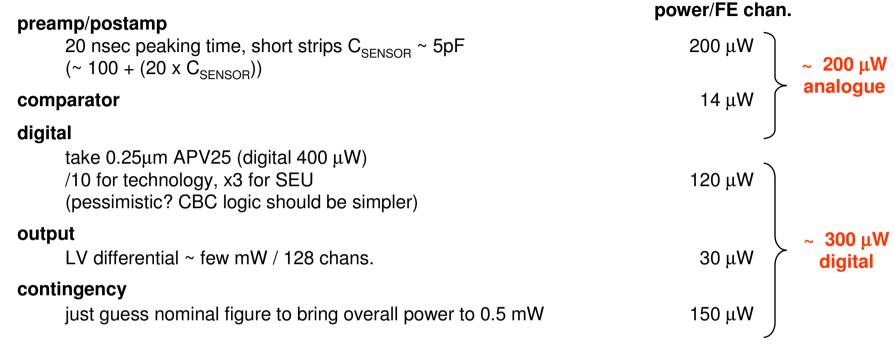

# **CBC** power

#### 0.5 mW / channel seems like an achievable target (c.f. 2.7 mW for APV25)

digital is biggest uncertainty, and maybe largest contributor hope to improve estimate as design progresses can consider running at lower voltage (dig. power ~ V<sup>2</sup>) => extra contingency e.g. 1.2 -> 0.85 power consumption halved will keep power rails separate on chip to keep option open

#### using numbers above: 128 chan. chip needs ~ 20 mA analogue, ~30 mA digital

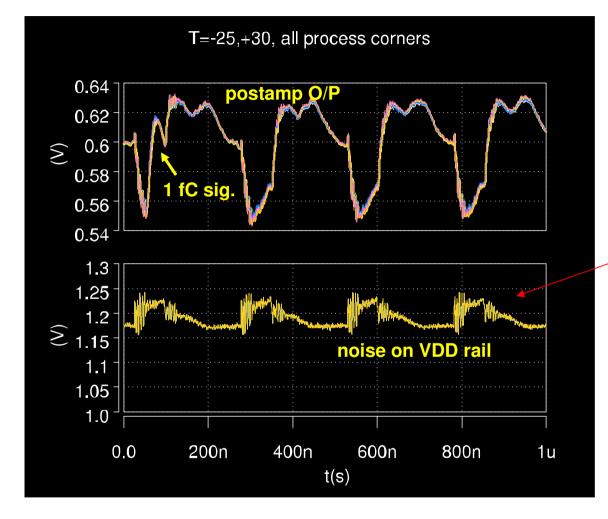

# front end PSR without LDO supply

#### time domain picture

measured noise waveform added to VDD rail supplying FE circuit

sampled scope data for Enpirion "quiet" converter provided by Aachen

but x10 to (artificially) make it noisier

~ 80 mV pk-pk

1 fC normal signal completely swamped by noise

**Ref:** http://indico.cern.ch/getFile.py/access?contribId=24&sessionId=0&resId=0&materialId=slides&confId=47293

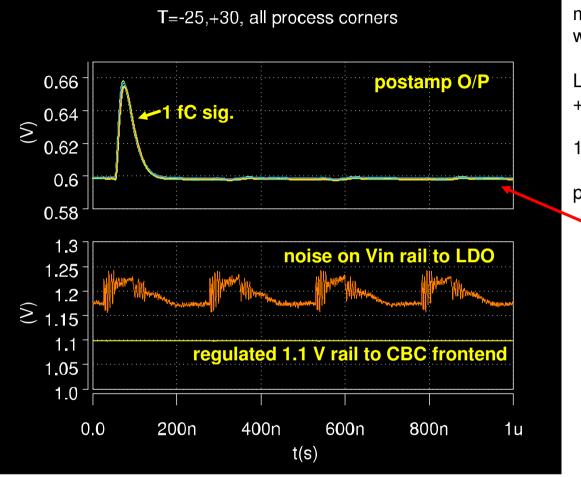

# front end PSR with LDO supply

measured **x10** (80 mV pk-pk) noise waveform now added to LDO Vin

LDO loaded by single CBC frontend + 25 mA extra dummy load

1 fC signal at postamp O/P now appears

postamp O/P noise just visible

~ 125e pk-pk