# **MGPA** first results

testing begun 29th May on bare die (packaging still underway)

two chips looked at so far - both working (all results here from one only)

### OUTLINE

test setup description analogue performance gain linearity matching noise I2C offset adjust calibration feature power consumption

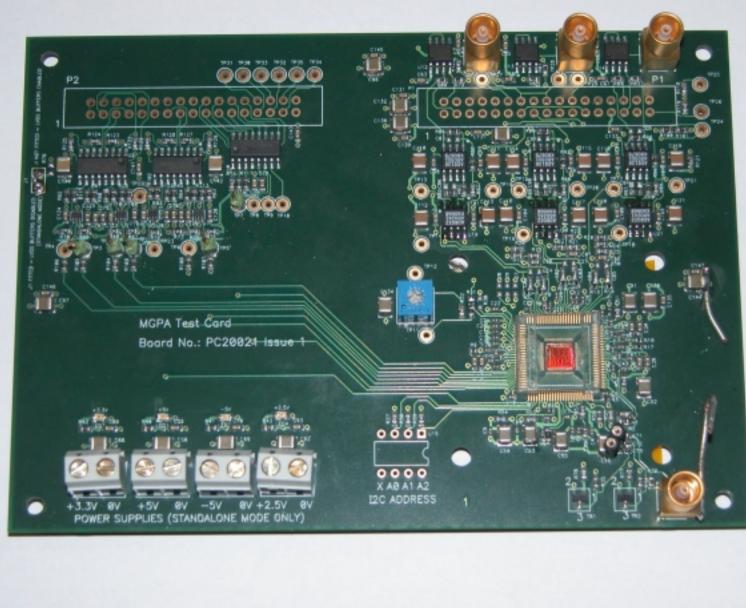

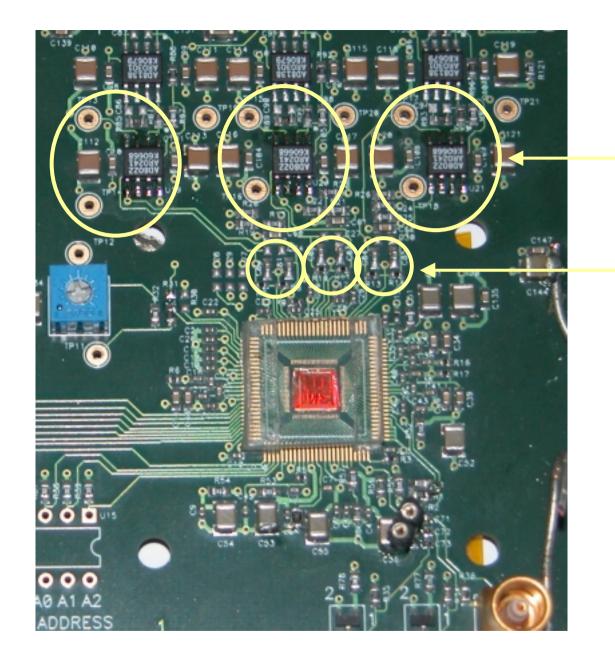

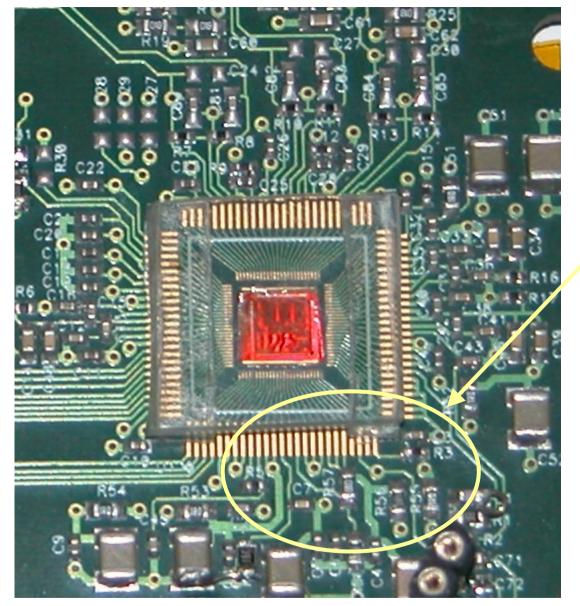

### RAL test board

packaged chips not yet available but RAL board can take bare die

dual purpose design 1) standalone–used here 2) interface to standard DAQ system

bias components fixed – no adjustment possible (without changing 0402 components)

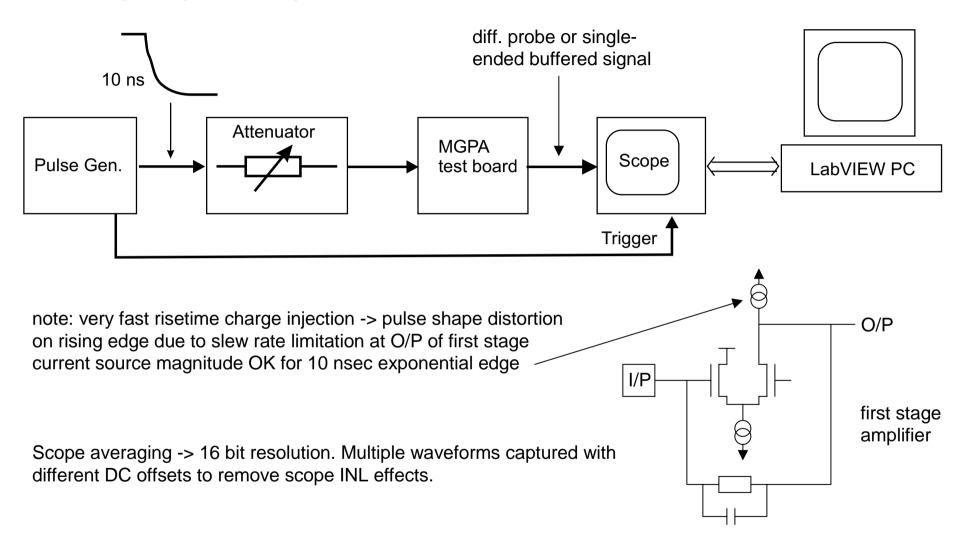

# Test setup for pulse shape measurements

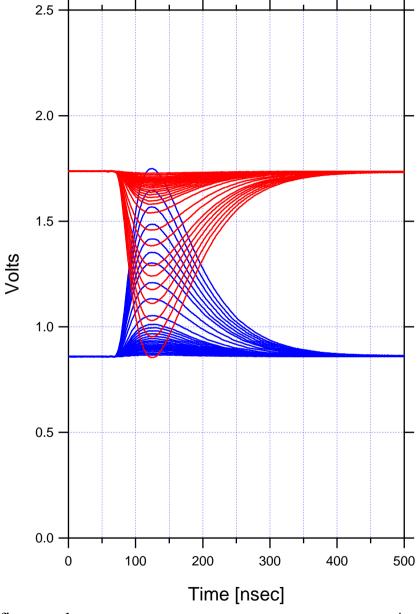

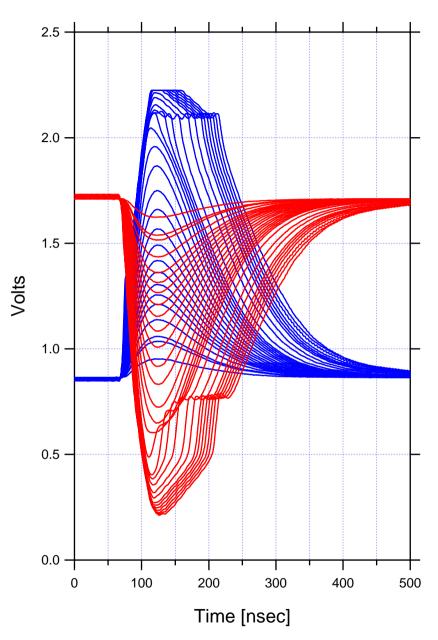

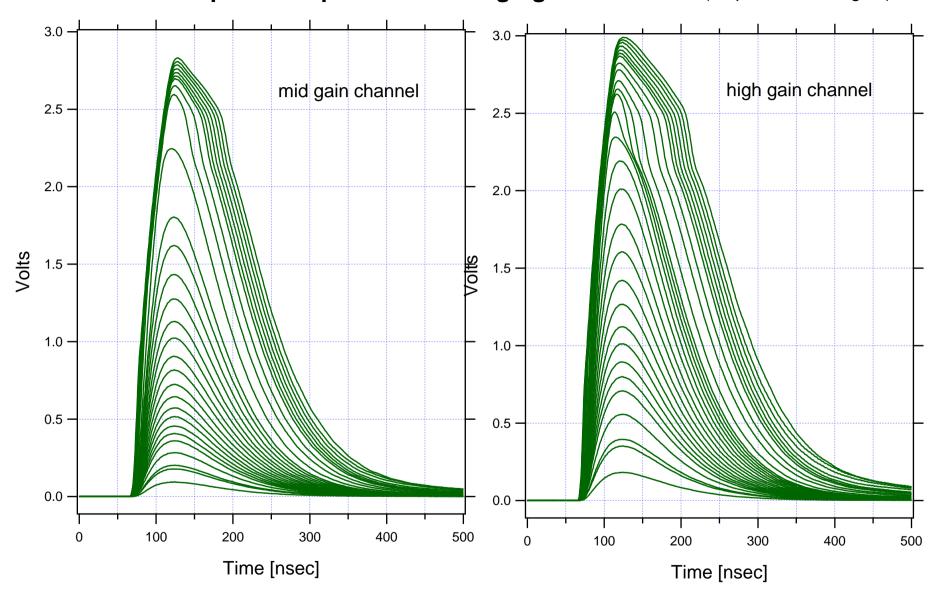

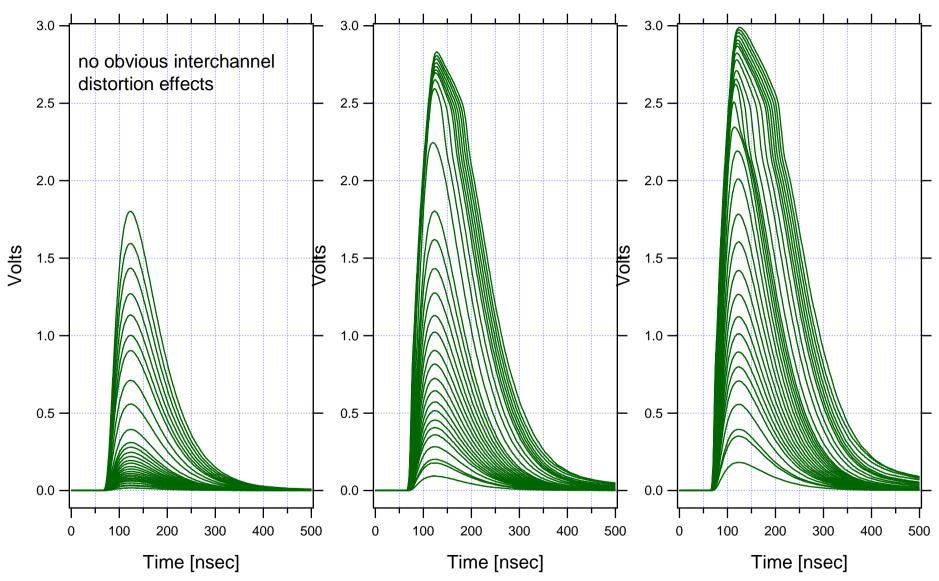

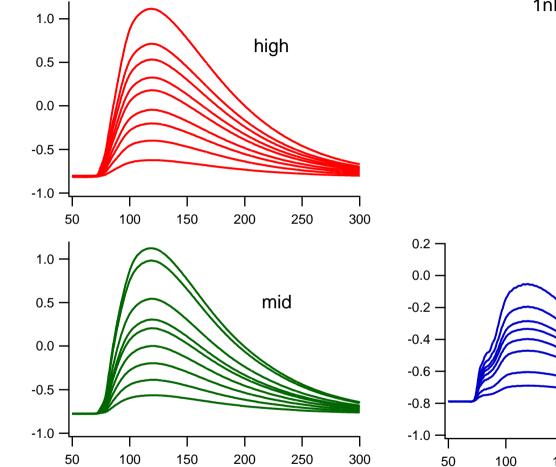

# Pulse shapes – low gain channel

signals up to 60 pC (feedback components for barrel application: 1.2k//33pF)

steps not equally spaced (log attenuator)

2 active probes on +ve and -ve outputs (before any buffering)

```

linear range +/- 0.45 V around Vcm (1.25 V nom.)

```

note: Vcm defined by external pot'l divider (5% resistors) so not exactly 1.25 V

CMS Ecal MGPA first results

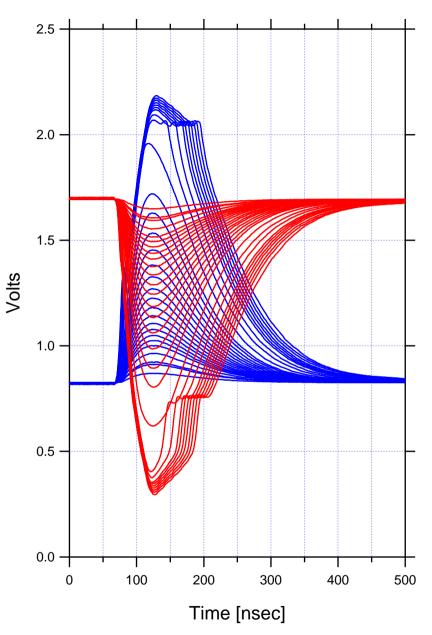

# Pulse shapes – mid gain channel

same signal steps as before (up to 60 pC)

this range only linear up to  $\sim 10 \text{ pC}$

shows saturation effects for out of range signals

# Pulse shapes – high gain channel

this range only linear up to  $\sim 5 \text{ pC}$

25th June, 2003

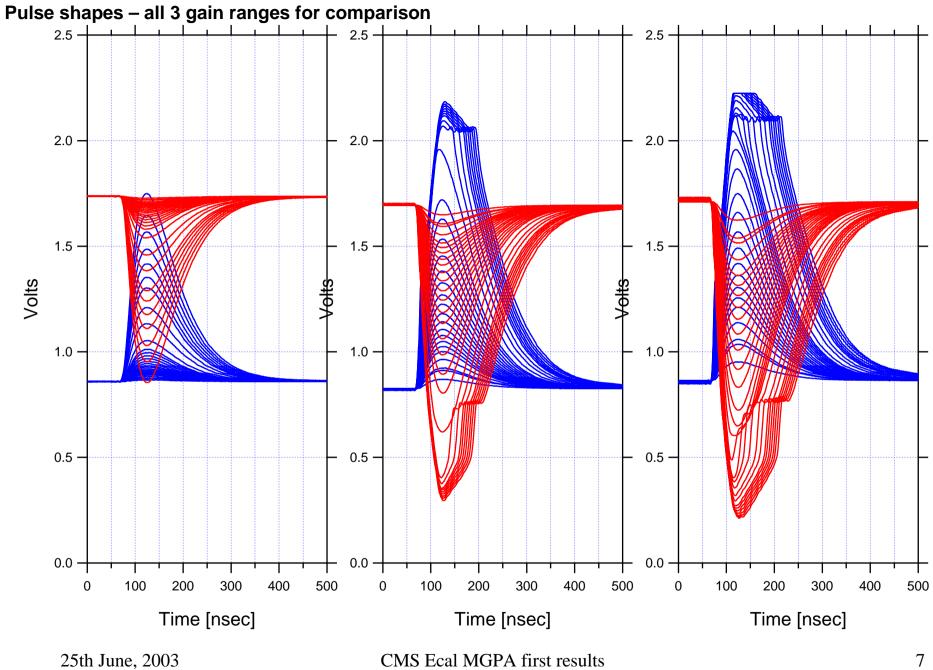

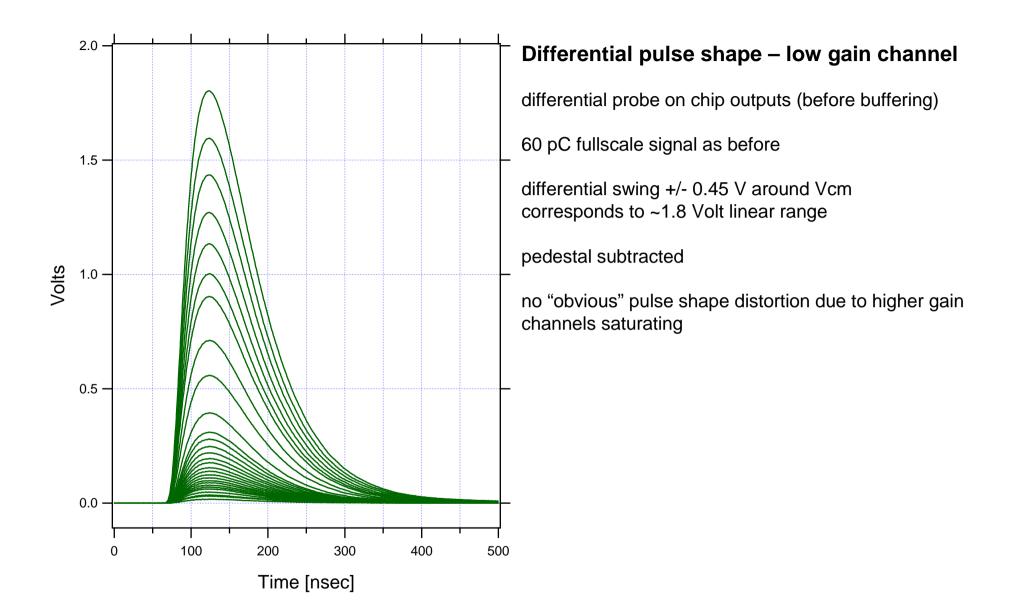

# Differential pulse shape – mid and high gain channels (60 pC fullscale signal)

25th June, 2003

CMS Ecal MGPA first results

Differential pulse shapes – all 3 gain channels compared – gain ratios 1:5.6:11.3 (cf 1:6:12)

25th June, 2003

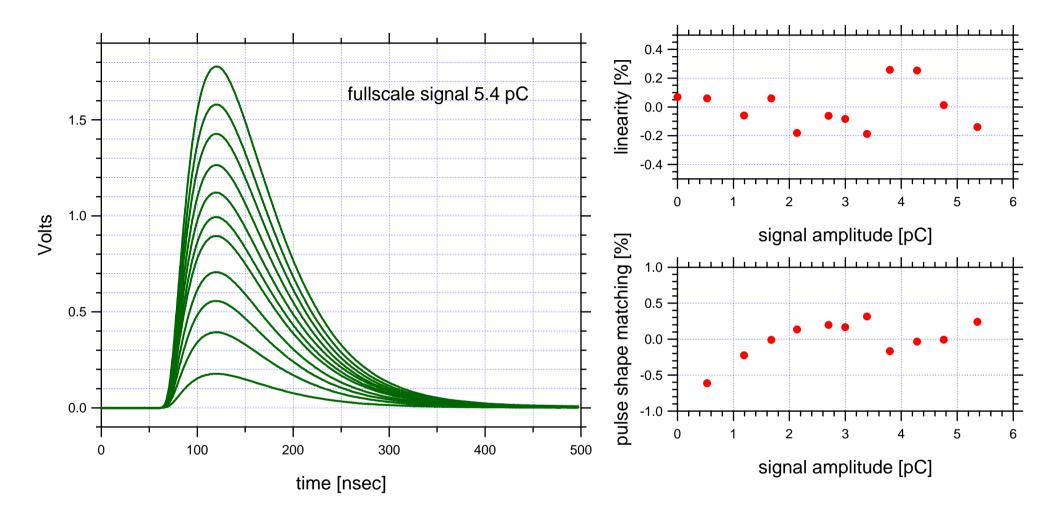

### Linearity and pulse shape matching – high gain channel

pulse shape matching in spec., linearity outside by factor ~2

25th June, 2003

#### 0.4 linearity [%] 0.2 fullscale signal 10.8 pC 1.5 -0.0 -0.2 -0.4 1.0 -Volts 10 12 n 2 6 pulse shape matching [%] signal amplitude [pC] 1.5 1.0 -0.5 -0.5 -0.0 · -0.5 --1.0 -0.0 -1.5 400 100 200 300 500 10 12 0 2 6 0 8 time [nsec] signal amplitude [pC]

### Linearity and pulse shape matching – mid gain channel

smallest signals show slower risetime - needs further investigation

#### 0.4 linearity [%] 0.2 fullscale signal 61 pC 1.5 -0.0 -0.2 -0.4 1.0 -Volts 20 30 50 60 0 10 40 pulse shape matching [%] signal amplitude [pC] 2 0.5 -1 0 -1 -0.0 -2 · 100 200 300 400 500 10 20 30 40 50 60 0 0 time [nsec] signal amplitude [pC]

### Linearity and pulse shape matching – low gain channel

similar (but worse) effect as for mid-gain channel

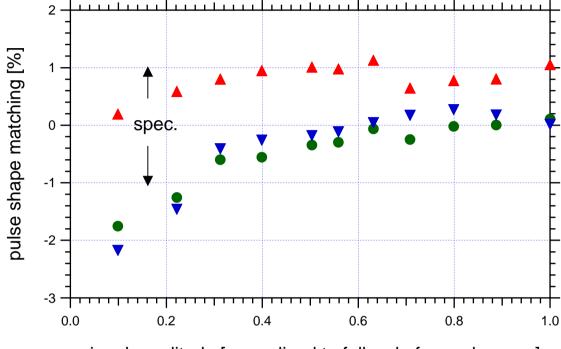

# Pulse shape matching between gain channels

### Pulse shape matching definition:

Pulse Shape Matching Factor PSMF=V(pk-25ns)/V(pk)

Pulse shape matching = [(PSMF-Ave.PSMF)/Ave.PSMF] X 100

Ave.PSMF = average for all signal sizes and gain ranges

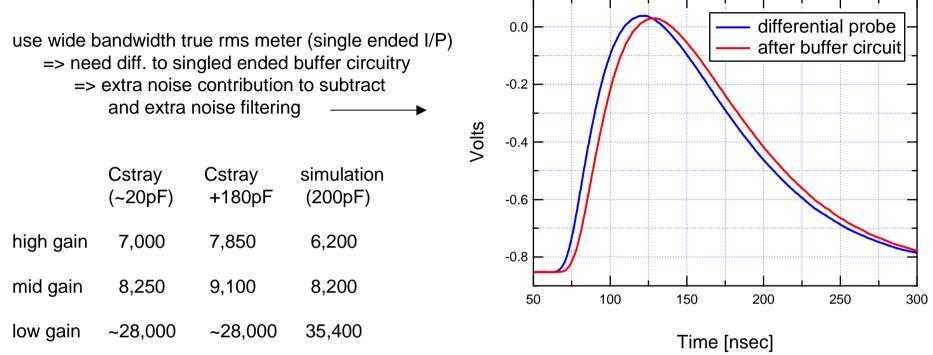

systematic discrepancies between channels can be due to mismatch in diff. O/P termination components or (<u>more likely here</u>) difference in stray capacitance from PCB layout

signal amplitude [normalised to fullscale for each range]

mismatch of stray O/P capacitance likely due to signal routing on test card

1<sup>st</sup> stage of buffering

differential O/P termination components (1% tolerance)

25th June, 2003

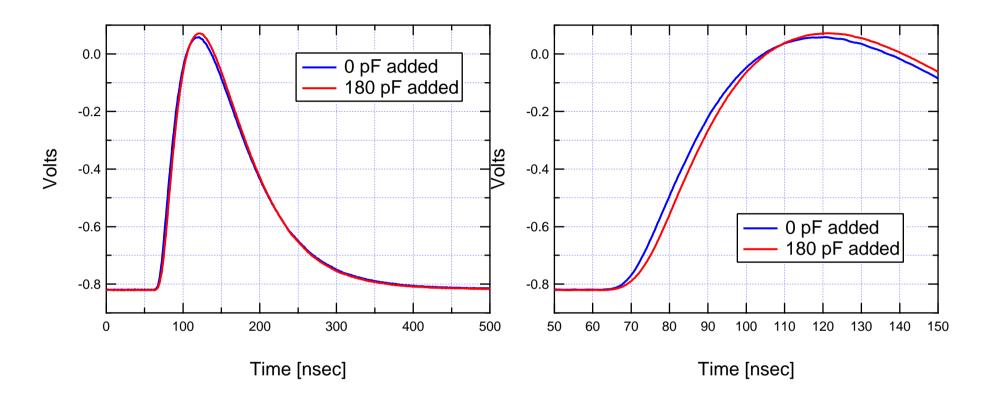

effect of input capacitance on pulse shape

pulse peak shifts by ~ 3 nsec.

# **Noise measurements**

weak dependence on input capacitance as expected

note: large uncertainty for low gain channel - buffer circuitry dominates here

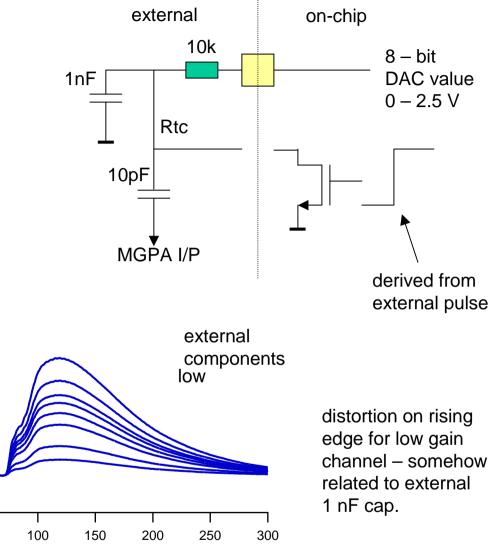

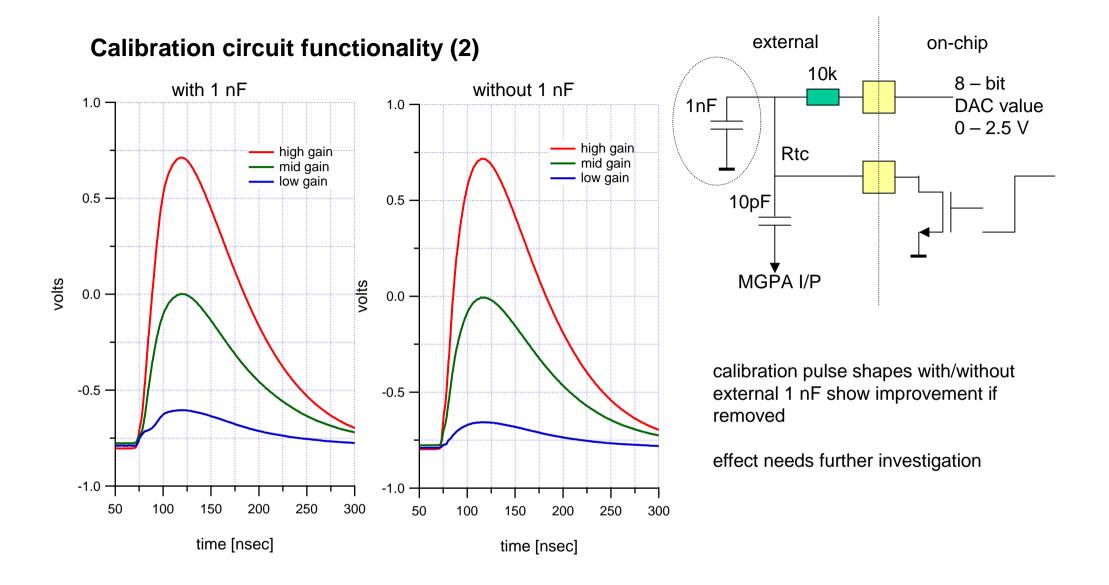

### Calibration circuit functionality (1)

### main concern so far:

high frequency instability (~ 250 MHz) can be introduced on first stage O/P when probing

not clear whether problem on chip (no hint during simulation)

or could be test board related decoupling components around first stage not as close in as would like VDDP, VS in particular

test board for packaged chips should help with diagnosis

decoupling closer in (may be cure?) bias currents easy to vary (should give clues)

# **Power consumption**

Current measured in 2.5 V rail supplying test board -> ~ 245 mA

-> chip current + Vcm divider (4mA) + power LED (3mA)

$\Rightarrow$ chip current = 238 mA

measuring bias currents and multiplying by mirroring ratios -> 235 mA

may change if further testing indicates changing bias conditions -> performance improvements worth having

# Summary

all results so far for one unpackaged chip, barrel feedback components to first stage

```

gains close to specification (1 : 5.6 : 11.3)

pulse shapes good

linearity ~ +/- 0.2% (~ 2 x spec.)

pulse shape matching within spec. apart from lowest end of mid and low gain ranges

no obvious distortion introduced on lower gain channels by higher gain channels saturating

=> good chip layout

```

noise close to simulation values (< 10,000 electrons for mid and high gain ranges)

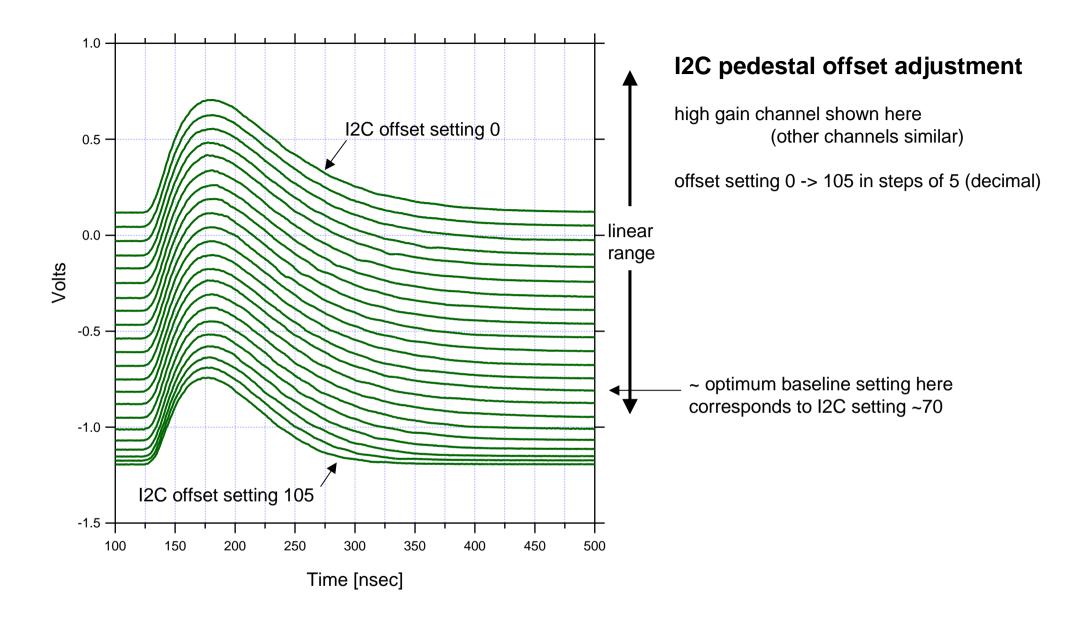

I2C features (channel offsets, calibration) fully functioning

plan to move to packaged chips as soon as available

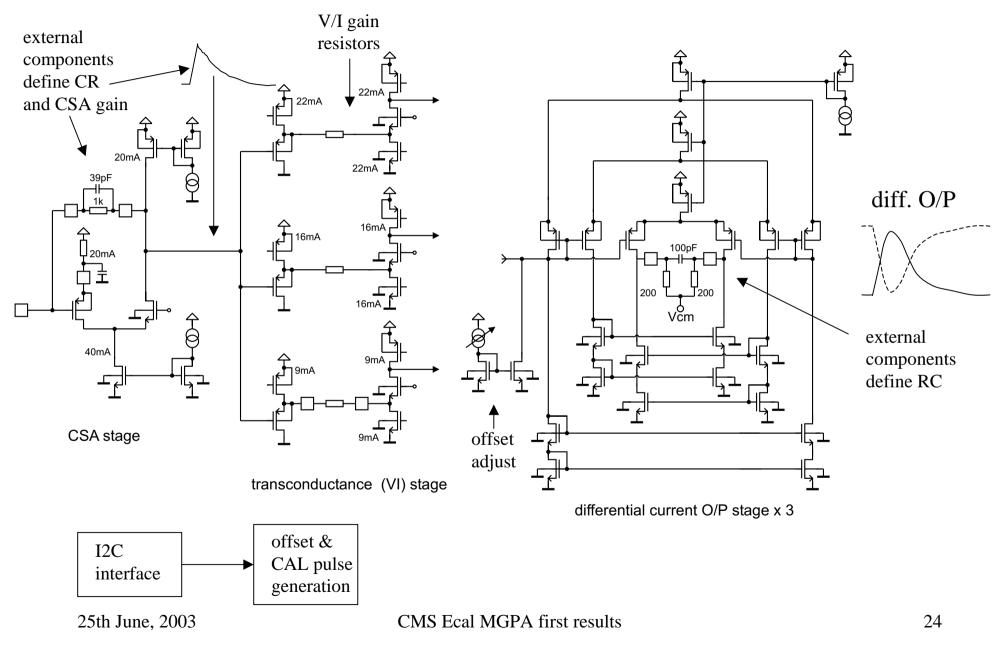

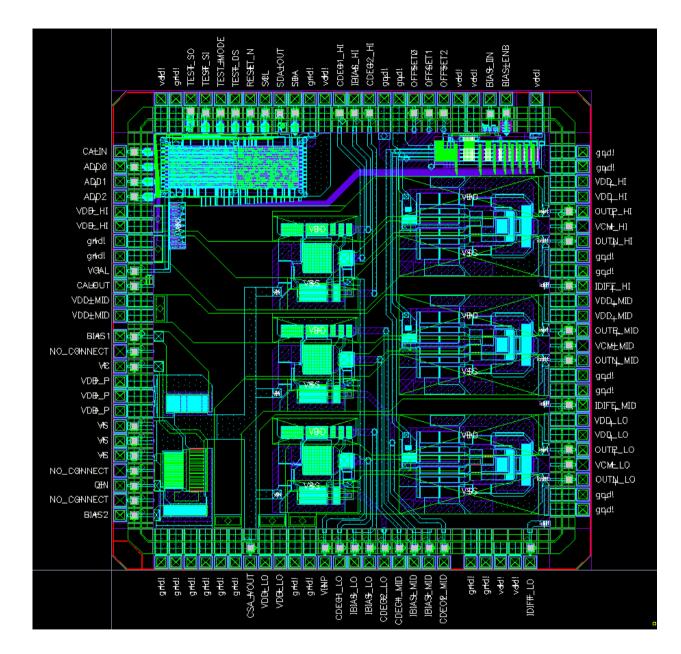

### MGPA – architecture overview

25th June, 2003