## how to reach 1/2 strip resolution in CBC3?

a few slides to aid discussion and maybe clear up any possible misunderstandings

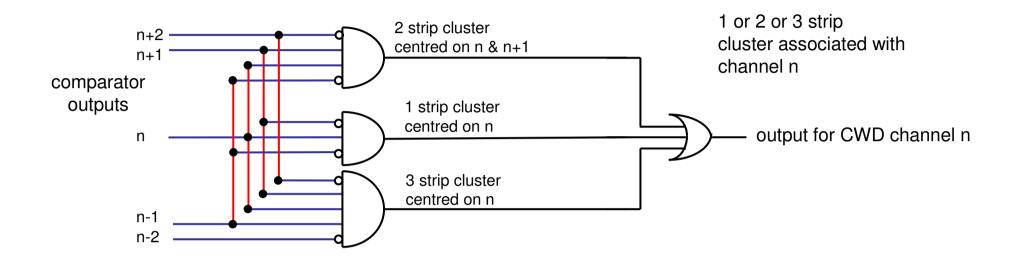

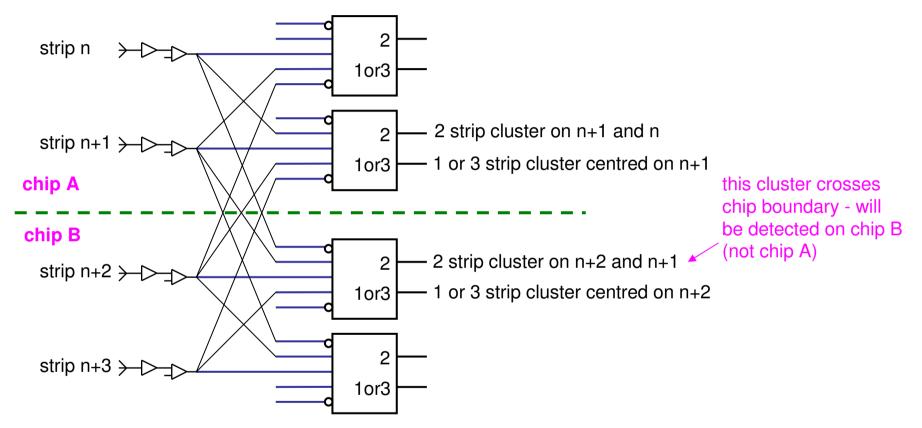

# CWD logic on CBC2

this is the current approach in CBC2 programmability not shown but can choose one of 4 options:

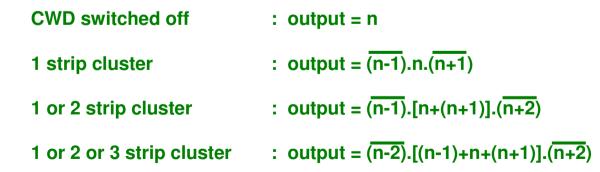

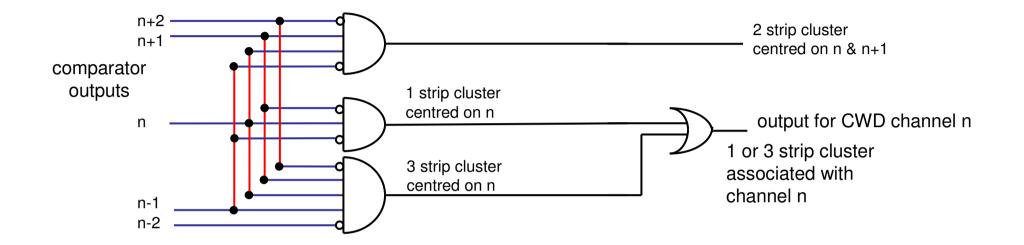

#### CWD logic with separate output for 2 strip clusters

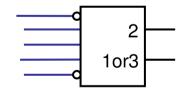

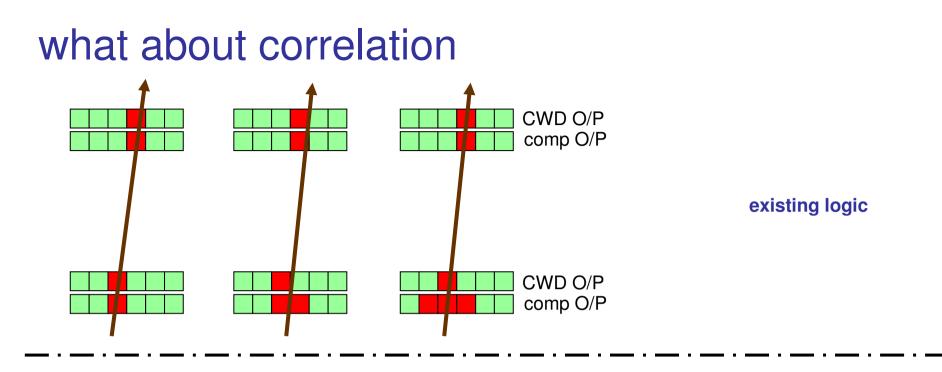

represent above as

### any consequences at chip boundaries?

I don't think so

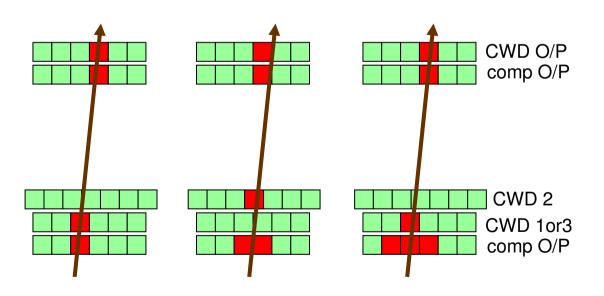

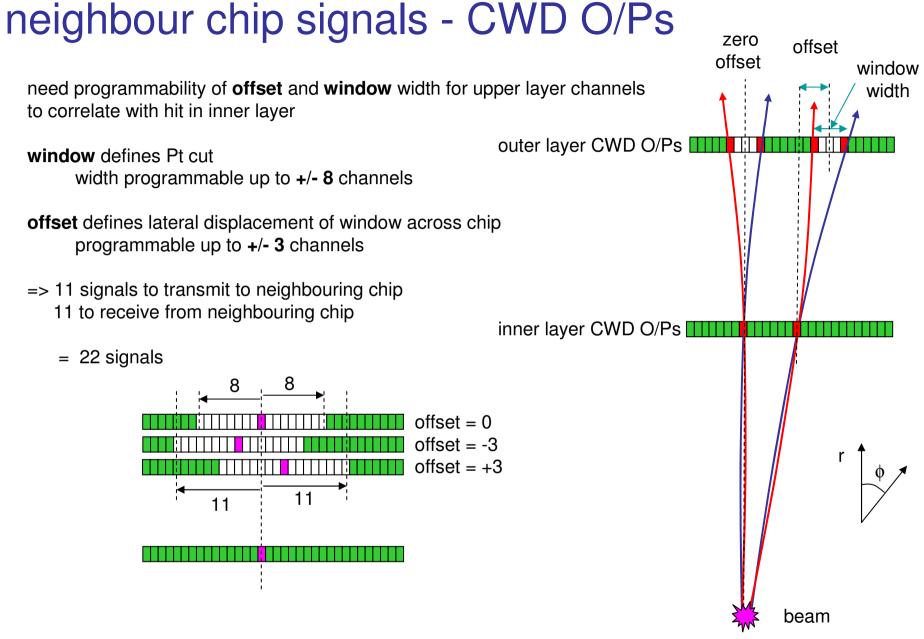

**future system** - some assumptions and questions

1/2 strip precision only required in inner (lower) layer?

can OR 1or3 output with 2 for correlation purposes?

# final comments

if assumptions on previous slide correct then ½ strip resolution (for hit in inner layer) only has implications for transmission data volume off-chip

<sup>1</sup>/<sub>2</sub> strip resolution for *correlation* and/or *outer layer window definition* means more inter-chip signals (I think) so that probably rules it out

off-chip data volume issues need further study (how to do it)

would like requirements for CBC3 to be firm by ~ March 2013 if possible (design phase should begin)

adding comp O/Ps -> 30 signals altogether, top and bottom of chip