2S-Pt module systems meeting, CERN, 23<sup>rd</sup> August, 2012.

### CBC2 test plans

M.Raymond

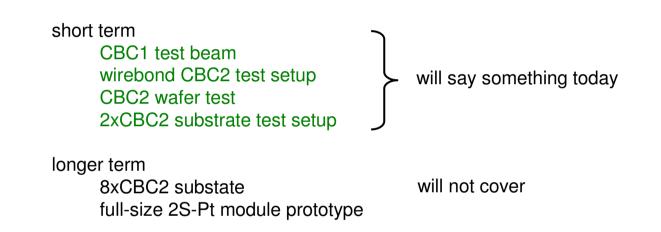

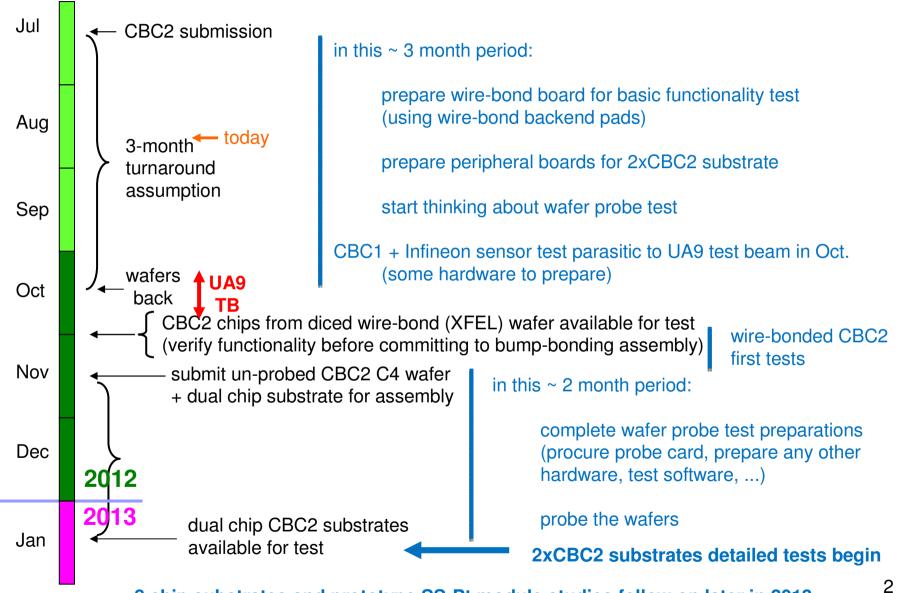

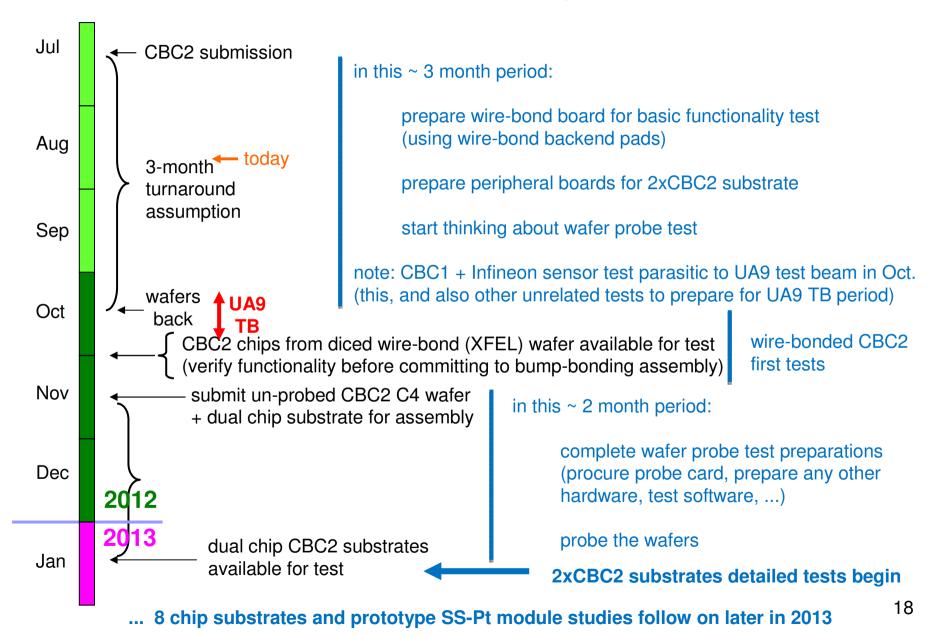

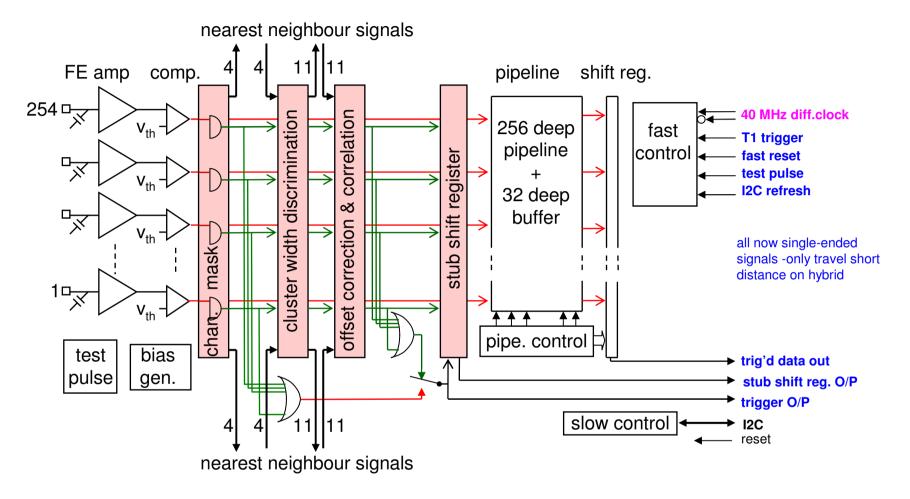

# timeline for next ~ 6 months

chip substrates and prototype SS-Pt module studies follow on later in 2013 8 ....

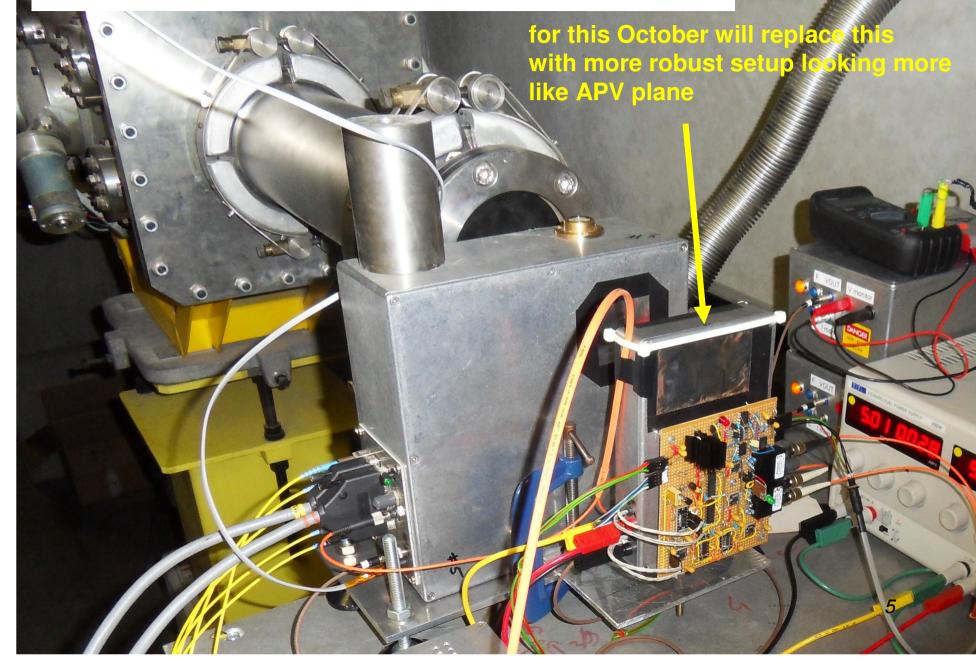

CBC1 test beam this year

# CBC1 test beam in 2011

CBC + sensor

beam tracking plane using APV

CBC + sensor operated parasitically in UA9 test

CERN H8 beam line September 2011

# CBC1 test beam in 2012 October (8 - 22)

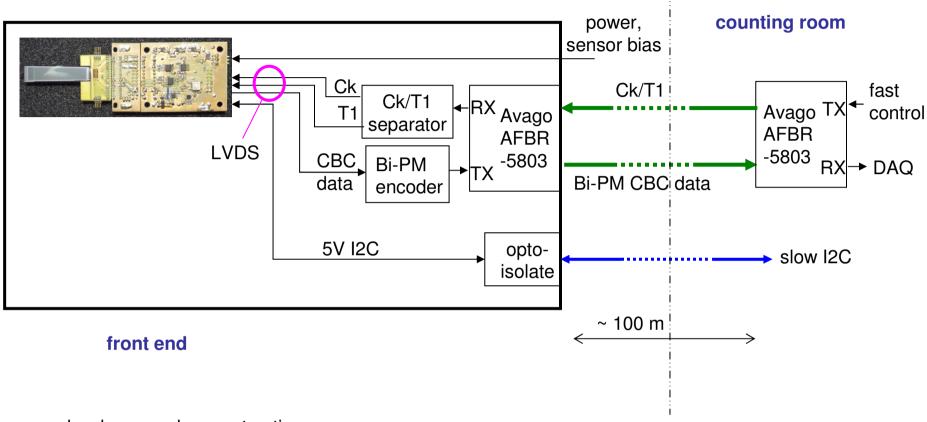

# CBC1 test beam system Oct. 2012

hardware under construction

will use Infineon 256 channel sensors from Vienna (4 received - will bond 2) reading out ~ 128 good strips (avoid bad strips region)

will give point of comparison with 2xCBC substrates using same sensors

### current hardware status

few bits left to put in

sensor to be glued and bonded this/next week

some testing required

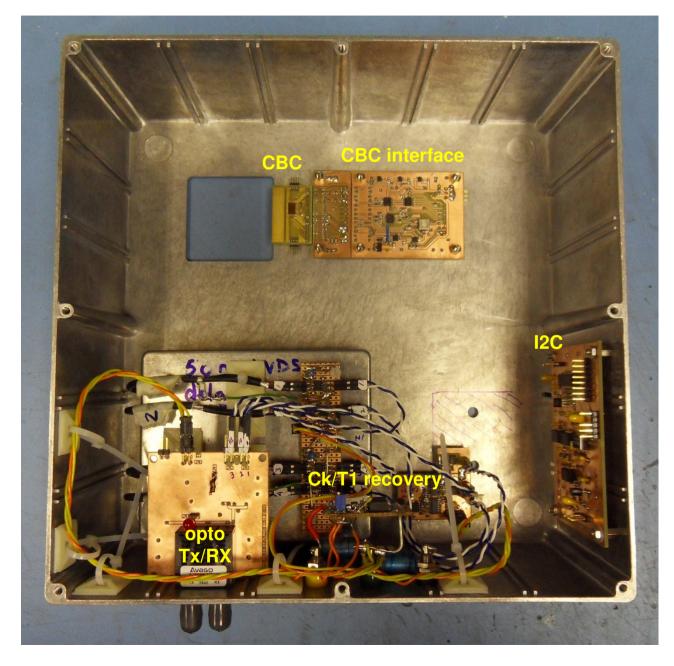

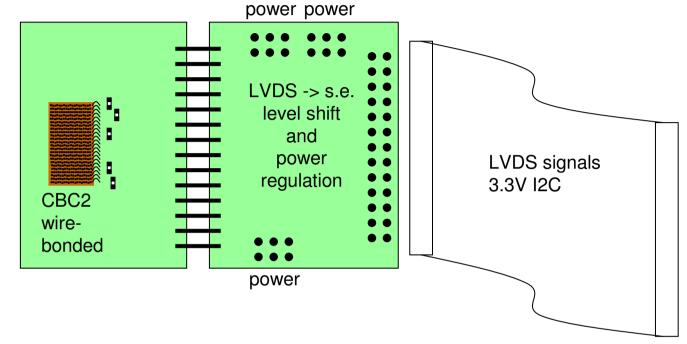

# wirebond CBC2 test setup

# wirebond CBC2 test setup

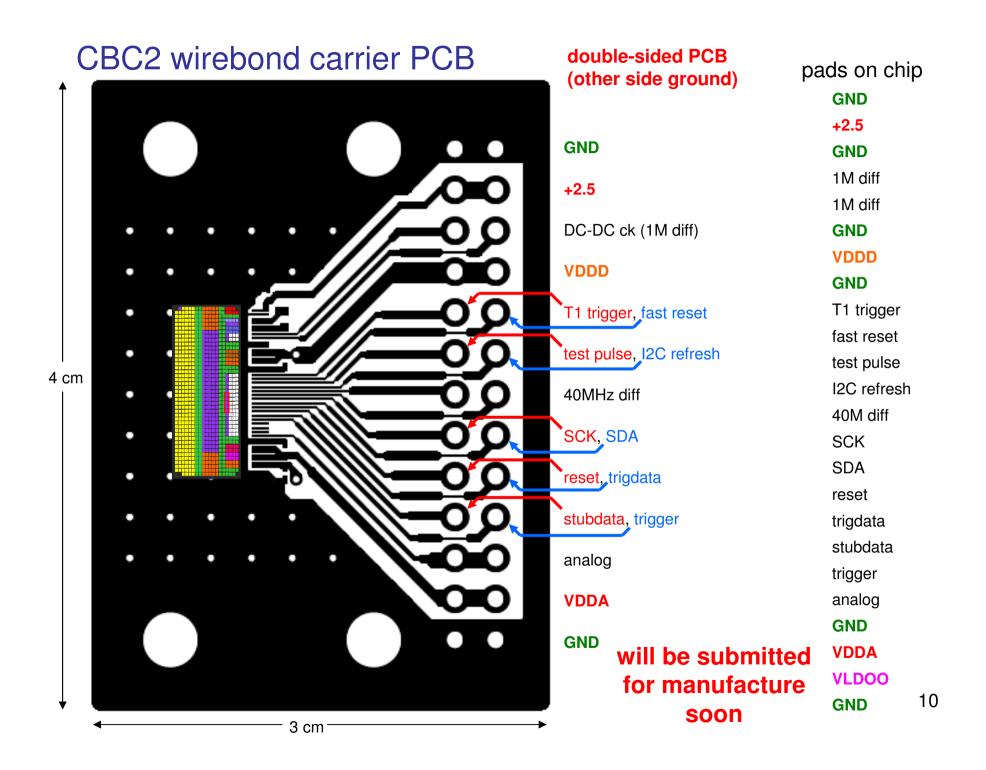

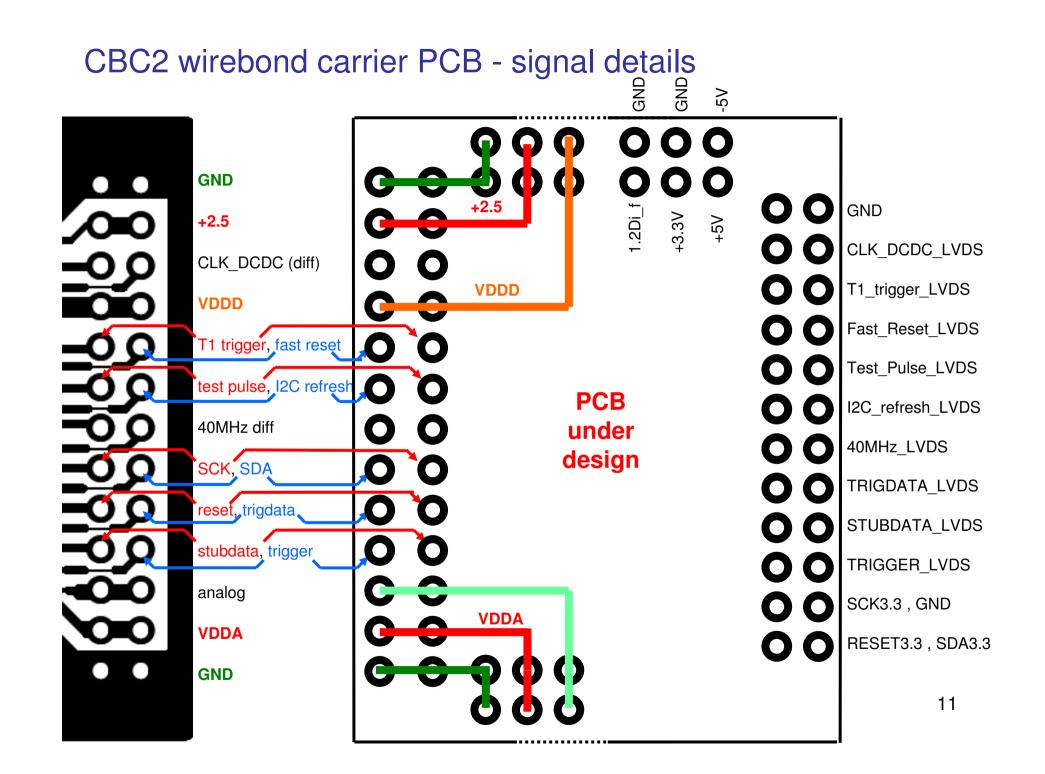

use wafer probe pads to wirebond single CBC2 die to carrier (CBC2 chips from diced wire-bond (XFEL) wafer)

allows to verify CBC2 functionality before committing to bump-bond

can also use to develop wafer probe procedures

# CBC2 wafer probing

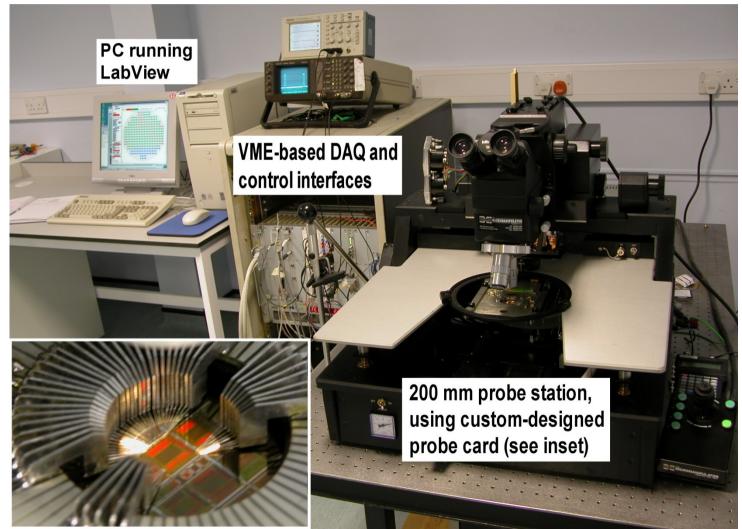

# Wafer Test Hardware

re-use APV screening system (would like to update but time is short)

need to get probe card manufactured (re-establish links with manufacturers)

Micromanipulator 8 inch semi–automatic probe station

VME based ADC (8 bits) RAL SeqSi 40 MHz CK/T1 CERN VI2C I/F

PC controls both DAQ (VME) & probe-station (RS232) 2xCBC2 substrate test setup

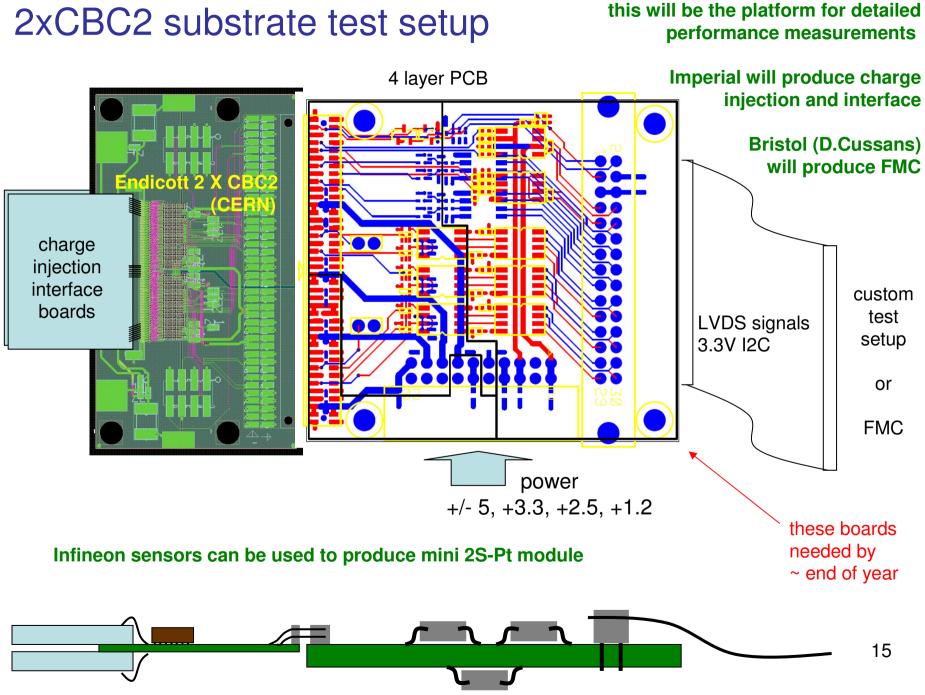

## 2xCBC2 substrate test setup

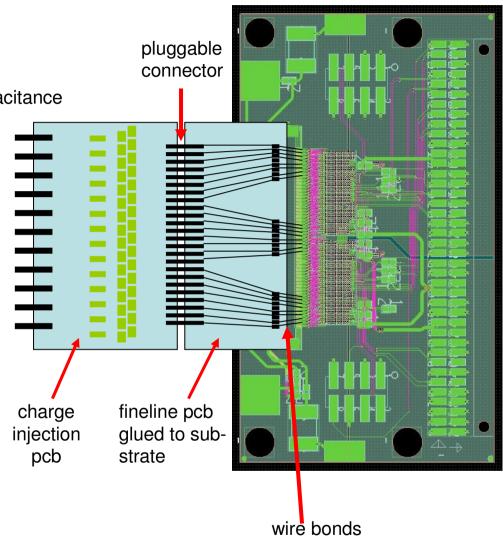

# charge injection

can only wirebond to 2xCBC substrate inputs

will want to study effects of varying external capacitance

don't want to waste substrates so propose a 2 stage approach

- 1) glue fineline pcb to substrate and wire-bond to CBC2 inputs. fineline pcb adapts to pluggable connector

- 2) can then have different variants of charge injection board that plug onto this to provide electrical interface

### summary

### short term (up to ~ end 2012 / beginning 2013)

CBC1 test beam October - hardware in preparation

wirebond CBC2

~ October/November - depending on wafer delivery should submit chip carrier boards for manufacture soon

CBC2 wafer probe

$\sim$  end 2012 - needed for 8-chip substrate production next year get probe card manufactured  $\sim$  November

2xCBC2 substrate

early 2013 interface board already close to finished, simple charge injection boards need bit more thought FMCs to be produced by Bristol

### division of labour

plan to concentrate test activity at Imperial (Davide will travel) avoids duplication of effort and extra hardware

# timeline for next ~ 6 months - repeated slide

## extra

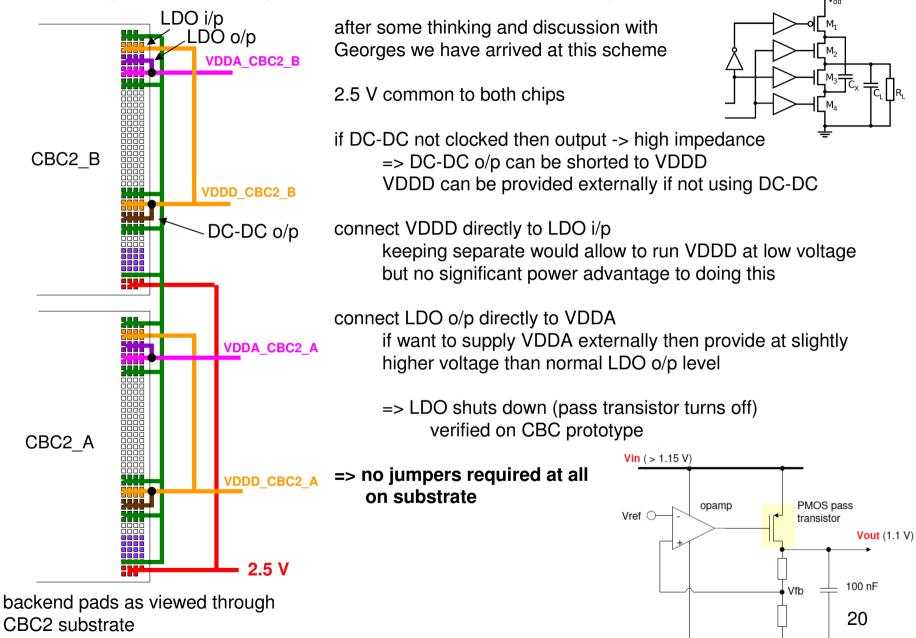

# CBC2 powering scheme on 2-chip substrate

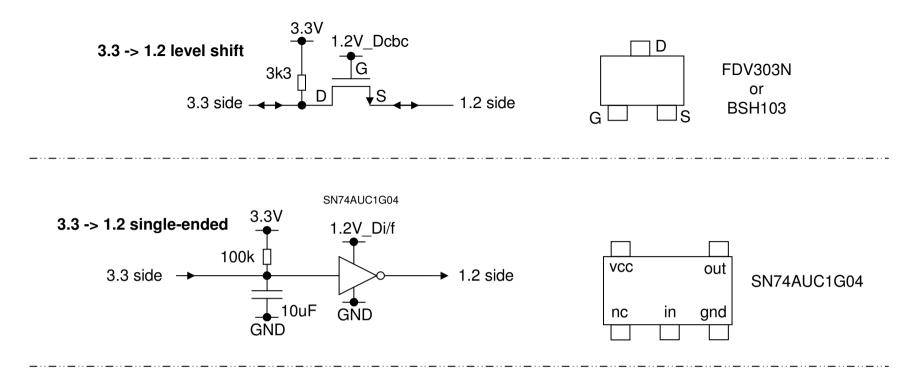

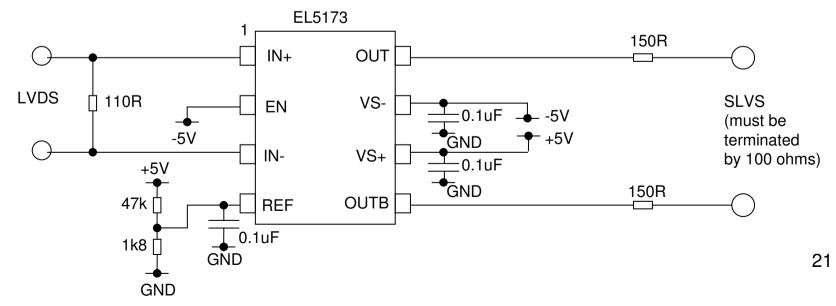

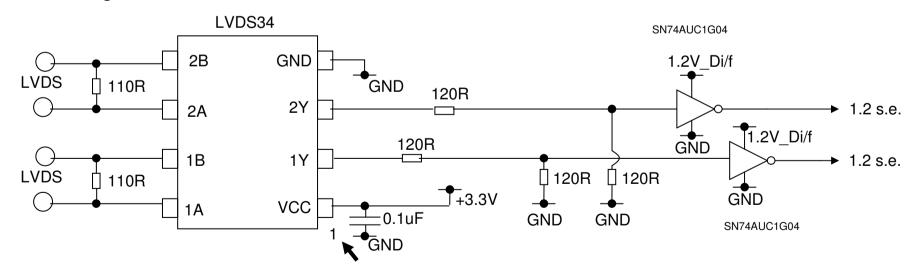

LVDS -> SLVS

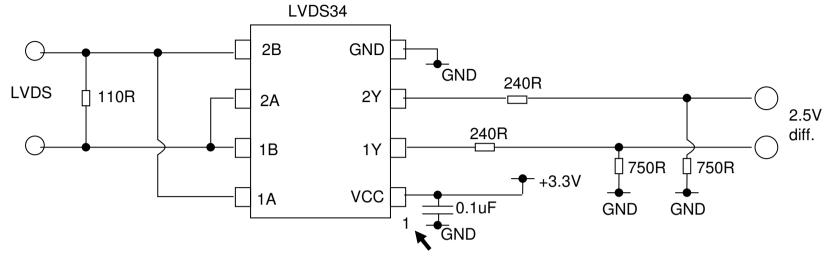

LVDS -> 2.5V diff.

LVDS -> single-ended

#### single-ended -> LVDS

23

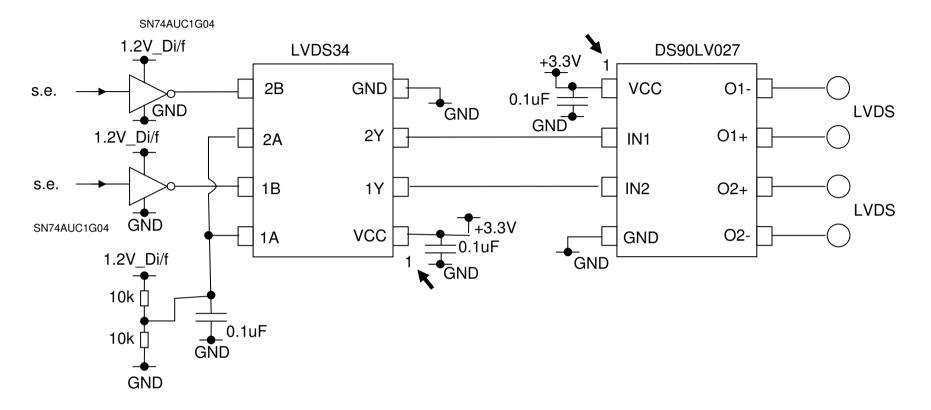

# **CBC2** architecture

#### blocks associated with Pt stub generation

channel mask: block noisy channels (but not from pipeline)

cluster width discrimination: exclude wide clusters > 3

offset correction and correlation: correct for phi offset across module and correlate between layers

stub shift register: test feature - shift out result of correlation operation at 40 MHz

fast OR at comp. O/P and correlation O/P: - can select either to transmit off-chip

for normal operation choose correlation O/P

# UK Phase II programme

CBC3 should be very close to final chip – available late 2014 incorporate architecture to transmit stub addresses slow ADC for on-chip monitoring

CBC4 pre-production iteration (2015/16) allows final bug fixes before full-wafer engineering run in 2017