2S-Pt module systems meeting, CERN, 18<sup>th</sup> June, 2012.

# **CBC** status

M.Raymond

# **Top Level status - Davide**

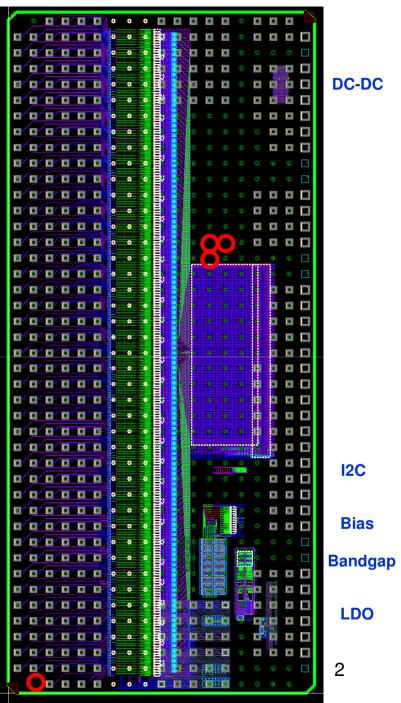

All the blocks are ready, now working on top-level routing and layout checks

Preliminary version sent to CERN to make progress with reticle

# **Submission status – Mark Prydderch**

today

$\mathbf{V}$

| ID 0 | Task Name                                           | Duration   | Start        | Finish       | T F | S S | M T     | W T | F S      | S M | T W T    | TF | S S | M | W | ΤF | S S | S M | T W           | TF  | S S | M T | W 1   | T F | S S      | MT | W | TF    |

|------|-----------------------------------------------------|------------|--------------|--------------|-----|-----|---------|-----|----------|-----|----------|----|-----|---|---|----|-----|-----|---------------|-----|-----|-----|-------|-----|----------|----|---|-------|

| 1    | 256 channel bump-bondable CBC                       | 31.35 days | Fri 01/06/12 | Thu 12/07/12 |     |     |         |     |          |     |          |    |     | - |   |    |     |     |               |     |     |     |       |     |          | -  |   | ,     |

| 2 🗸  | Memory Fan In Layout                                | 2 days     | Fri 01/06/12 | Mon 04/06/12 |     | 1   | <b></b> |     |          |     |          |    |     |   |   |    |     |     |               |     |     |     |       |     |          |    |   |       |

| 3 🗸  | Add Extra biases to Bias block                      | 4 days     | Mon 04/06/12 | Fri 08/06/12 |     |     |         |     | David    | e   |          |    |     |   |   |    |     |     |               |     |     |     |       |     |          |    |   |       |

| 4 🗸  | Add extra registers to I2C                          | 2 days     | Fri 08/06/12 | Tue 12/06/12 |     |     |         |     |          | _   | 📄 Davide |    |     |   |   |    |     |     |               |     |     |     |       |     |          |    |   |       |

| 5 🗸  | Prepare Pad Cells                                   | 2 days     | Fri 01/06/12 | Mon 04/06/12 |     | 1 1 | Ma      | rk  |          |     |          |    |     |   |   |    |     |     |               |     |     |     |       |     |          |    |   |       |

| 6 🗸  | Edit Pipeline logic layout for new shift reg length | 2 days     | Mon 04/06/12 | Wed 06/06/12 |     |     |         | Mar | <u>*</u> |     |          |    |     |   |   |    |     |     |               |     |     |     |       |     |          |    |   |       |

| 7 📰  | Top Level Assembly & Checks                         | 12 days    | Thu 07/06/12 | Fri 22/06/12 |     |     |         |     |          |     |          |    |     |   |   |    | ALL | -   |               |     |     |     |       |     |          |    |   |       |

| 8    | Design Review Preparation                           | 2 days     | Mon 25/06/12 | Tue 26/06/12 |     |     |         |     |          |     |          |    |     |   |   |    |     |     | ALL           |     |     |     |       |     |          |    |   |       |

| 9    | Final Design Review                                 | 0 days     | Wed 27/06/12 | Wed 27/06/12 |     |     |         |     |          |     |          |    |     |   |   |    |     |     | \$ <u>27/</u> | )6  |     |     |       |     |          |    |   |       |

| 10 🔳 | Post Review Corrections                             | 5 days     | Wed 27/06/12 | Tue 03/07/12 |     |     |         |     |          |     |          |    |     |   |   |    |     |     |               | 1 1 | 1   | 1 1 | ALL   |     |          |    |   |       |

| 11 🔳 | Submission                                          | 0 days     | Tue 03/07/12 | Tue 03/07/12 |     |     |         |     |          |     |          |    |     |   |   |    |     |     |               |     |     |     | 03/07 |     |          |    |   |       |

| 12   | Iteration with CERN/IBM                             | 6 days     | Tue 03/07/12 | Wed 11/07/12 |     |     |         |     |          |     |          |    |     |   |   |    |     |     |               |     |     |     |       | 1   | <u>1</u> |    |   |       |

| 13 🔳 | Re-scheduled Submission Date                        | 0 days     | Thu 12/07/12 | Thu 12/07/12 |     |     |         |     |          |     |          |    |     |   |   |    |     |     |               |     |     |     |       |     |          |    | 6 | 12/07 |

- Pre-submission design review moved to the 27/06/12

- Aim to submit design to CERN 03/07/12.

- Submission date revised from the 27/06/12 to 12/07/12

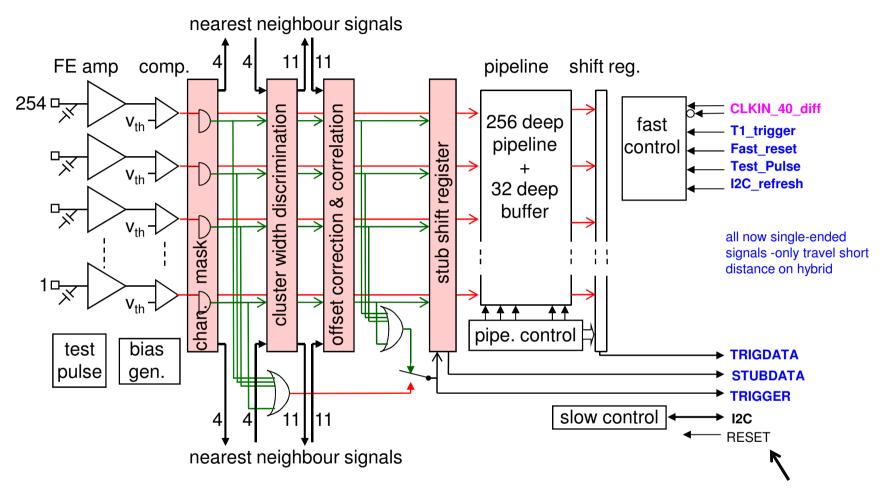

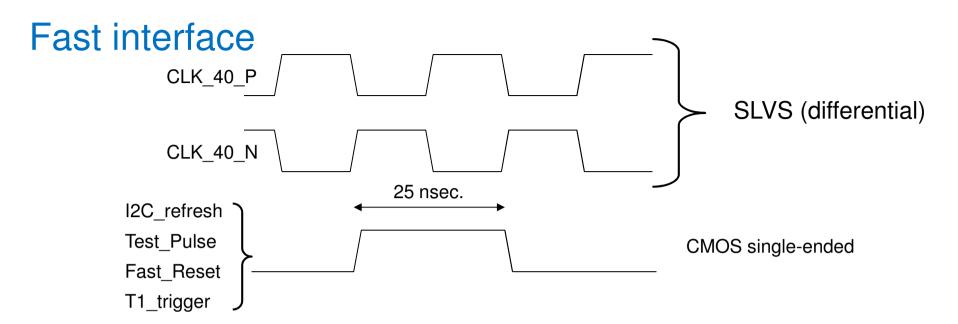

## **CBC2** interface specifications

details (exact timing and I2C register definitions) will be specified in CBC2 user manual hard reset (CMOS level) user manual for CBC1 exists (not widely circulated) and is available on request

#### I2C refresh

resets all I2C registers to majority value

### Test\_Pulse

injects charge (programmable amplitude, programmable phase w.r.t. 40 MHz) 8 groups of ~32 channels (programmable selection of group) follow with T1\_trigger ~ latency later

### Fast\_Reset

like Reset101 for APV (resynch) resets fast control logic, relaunches pipeline pointers must hold-off T1\_triggers until latency elapsed

### T1\_trigger

triggers readout of a time-slice of the pipeline memory, consecutive triggers allowed

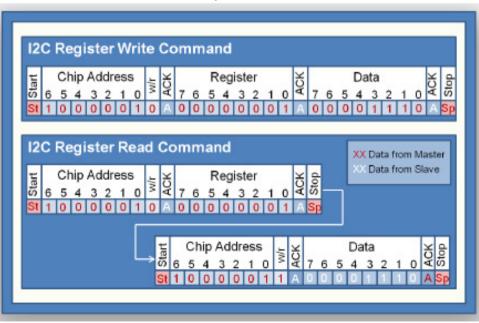

### Slow control I2C interface

up to 1 MHz operation (30 pF, 3.3k pull-up)

5-bit selectable (bonded on substrate) I2C address, CBC is always slave

internal register types include:

FE analogue bias levels, polarity, comp. hysteresis, hit detect operation, ... as in present chip, with minor changes

test pulse features

amplitude, phase w.r.t. 40 MHz (1 nsec steps), which group of 32 channels

individual channel comparator offsets 254 8-bit values

individual channel mask 32 8-bit registers

. . . . . .

Pt stub registers window offset and width

details can be made available soon after chip submitted

picture from CBC1 user manual

## Outputs – single ended

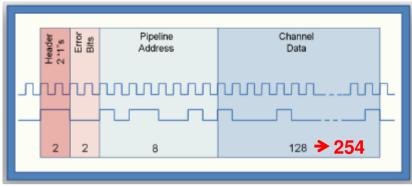

#### TRIGDATA

like for CBC1 but longer data packet  $\Rightarrow$  266 x 25ns = 6.6 usec.

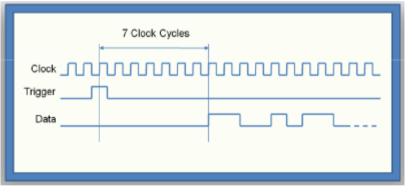

### TRIGGER

25 ns duration bit indicates EITHER (programmable): presence of Pt stub OR hit on any channel

exact timing rel. to amplifier input to be confirmed

#### STUBDATA

test feature contents of shift reg at correlation output shifted out at 40 Mbps can be disabled

#### pictures from CBC1 user manual

#### TRIGDATA data frame

### TRIGDATA data frame start w.r.t. T1\_trigger

### TRIGDATA "back-to-back" frame gap

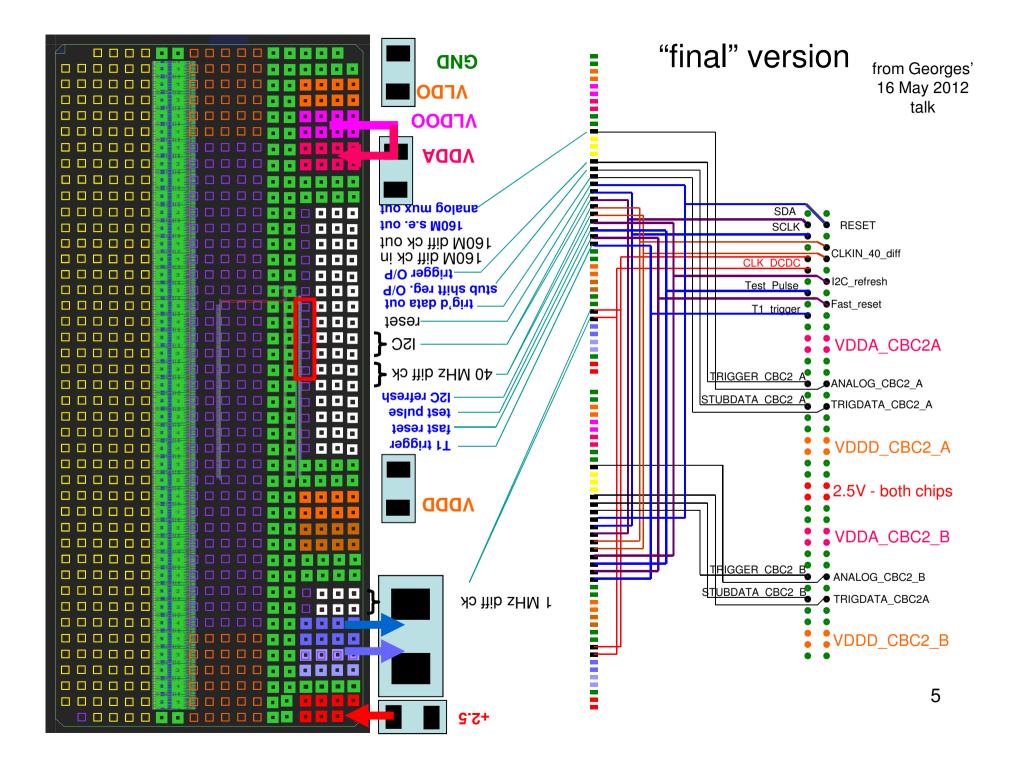

### HARD RESET & DC-DC

RESET

CMOS level, active high resets I2C registers and interface, and other logic after re-programming desired register values, follow with Fast\_Reset

CLK\_DCDC

1 MHz differential clock - 2.5 V levels should be synchronous to 40 MHz BX clock

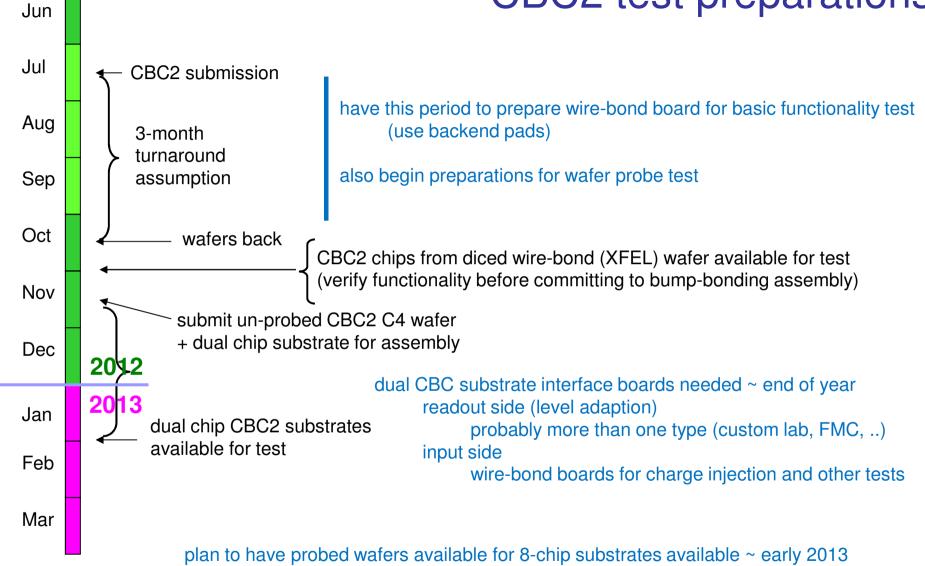

## **CBC2** test preparations

## CBC2 testing - division of labour

chip verification will be split between Imperial and RAL (Davide)

- some duplication inevitable but will try and avoid too much

- will develop more detailed plan once chip gone

# UK CBC development plan

submission to UK funding agency very soon – phase II tracker readout main objective is:

To complete development of a readout and triggering chip suitable for the SS-Pt module bringing the chip to a final state ready for mass production.

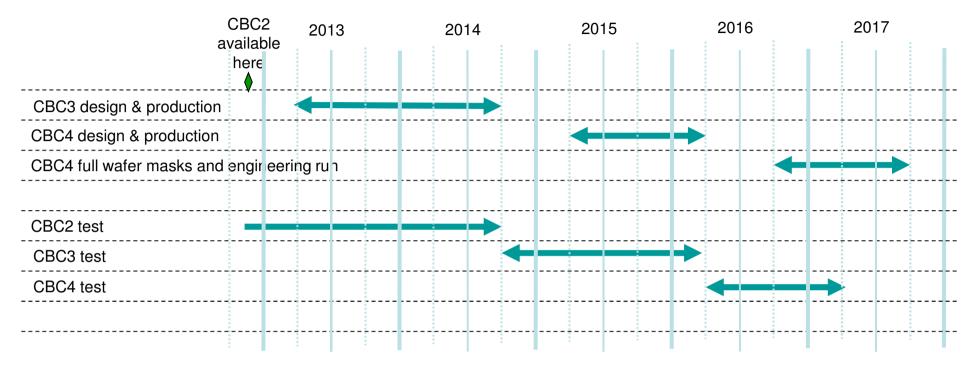

CBC3 should be very close to final chip – available late 2014 CBC4 pre-production iteration (2015/16) allows final bug fixes before full-wafer engineering run in 2017