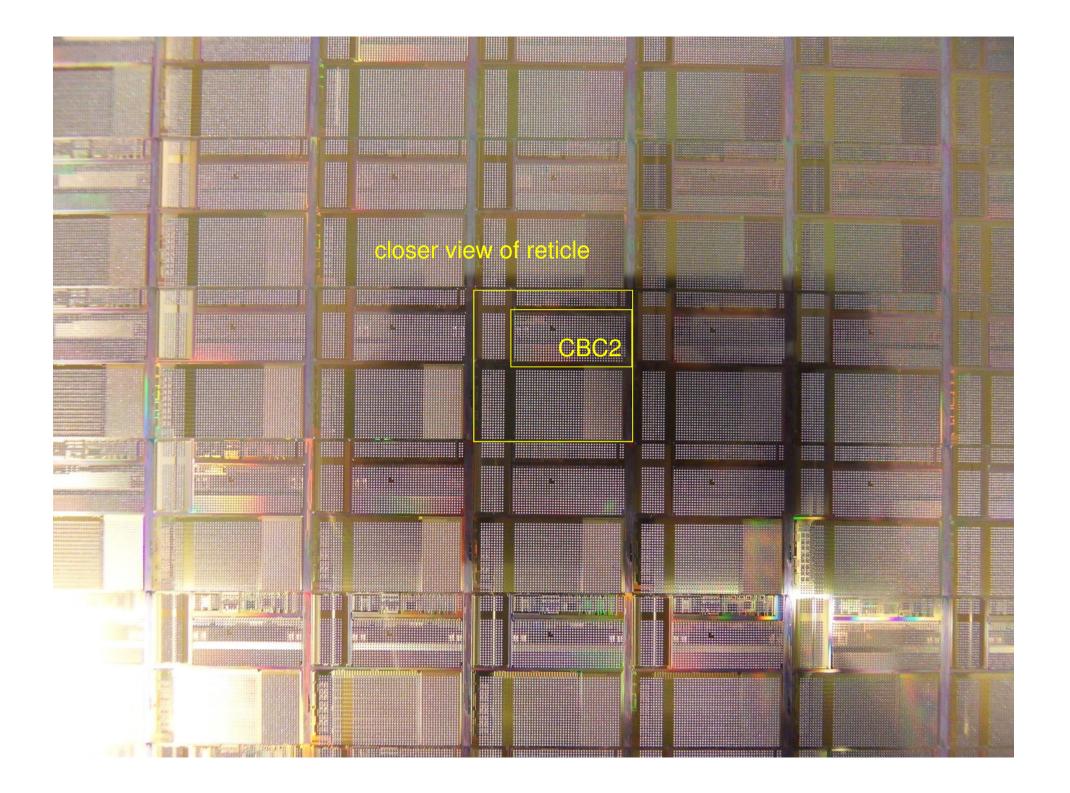

#### CBC2 wafer testing results

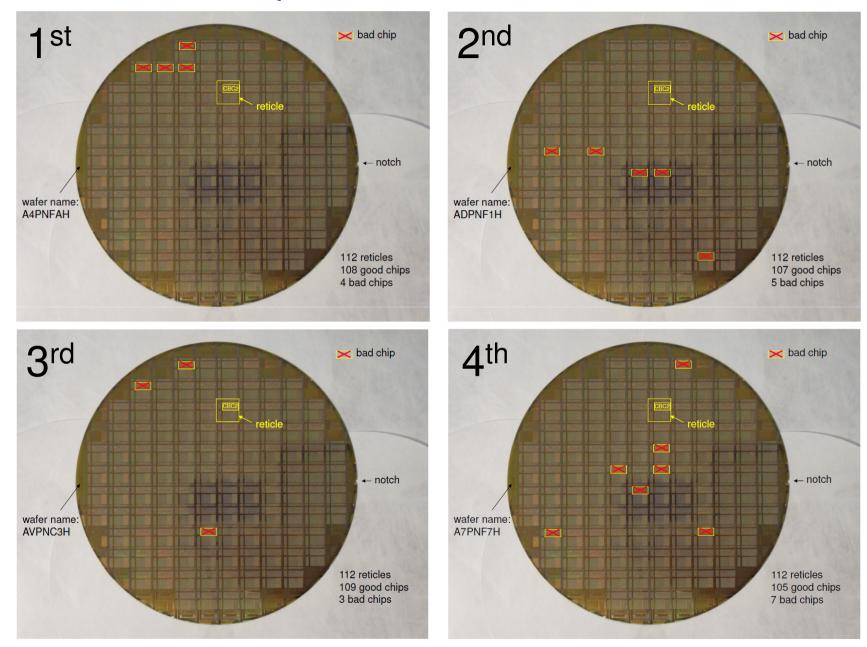

4 (of 8) wafers now probed 1<sup>st</sup> wafer - March 2013 -> 2CBC2 hybrids 2<sup>nd</sup> - September 2013 -> 8CBC2flex hybrids 3<sup>rd</sup> & 4<sup>th</sup> - August 2014 -> new 8CBC2flex hybrids

will describe evolution of test procedures & show some analysis of results

Mark Raymond, systems meeting, 30<sup>th</sup> September, 2014.

#### wafer test development

1<sup>st</sup> wafer, A4PNFAH

no I2C registers contain stuck bits (write & read back all 1's and all 0's) all channels respond to test pulse power consumption and some biases swept

2<sup>nd</sup> wafer, ADPNF1H, some additional tests basic offset tuning all pipeline locations accessed looking for stuck cells

3<sup>rd</sup> & 4<sup>th</sup> wafers, A7PNF7H & AVPNC3H, further refinements implemented recommended offset tuning procedure s-curves for pedestals & s-curves with test pulse acquired fully automated procedure - takes ~ 5 mins per chip

#### wafer results maps

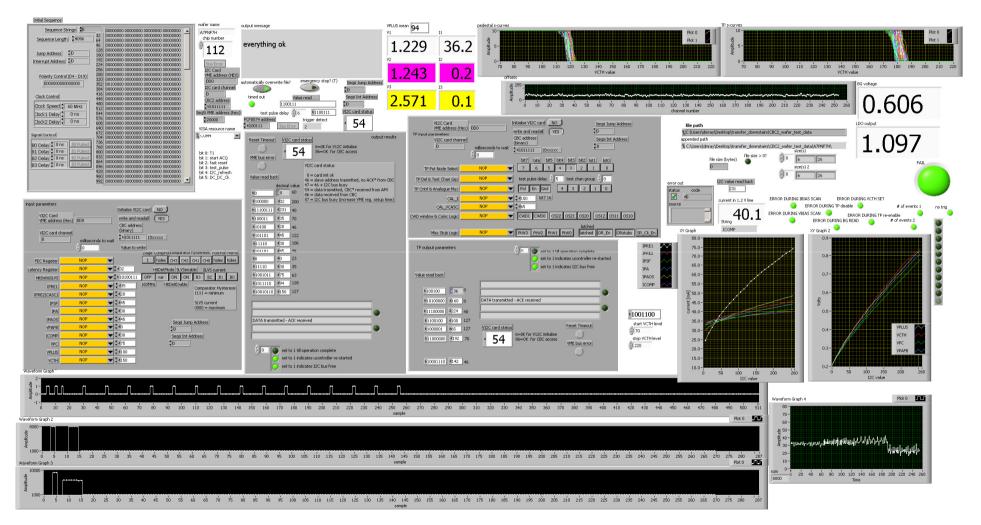

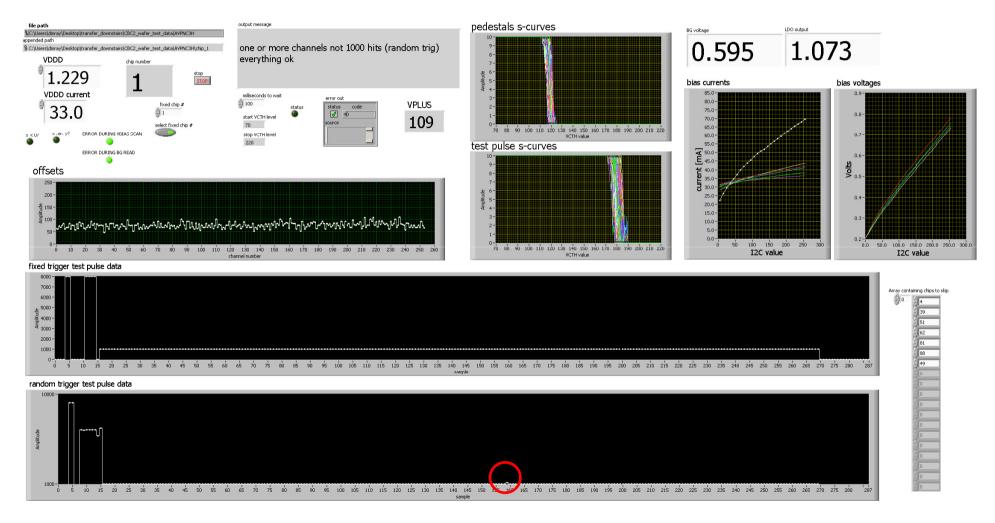

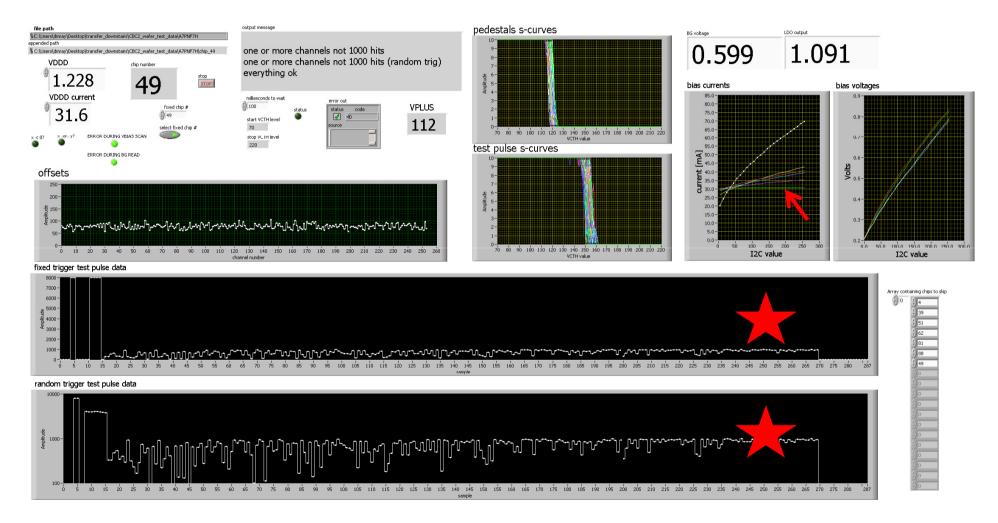

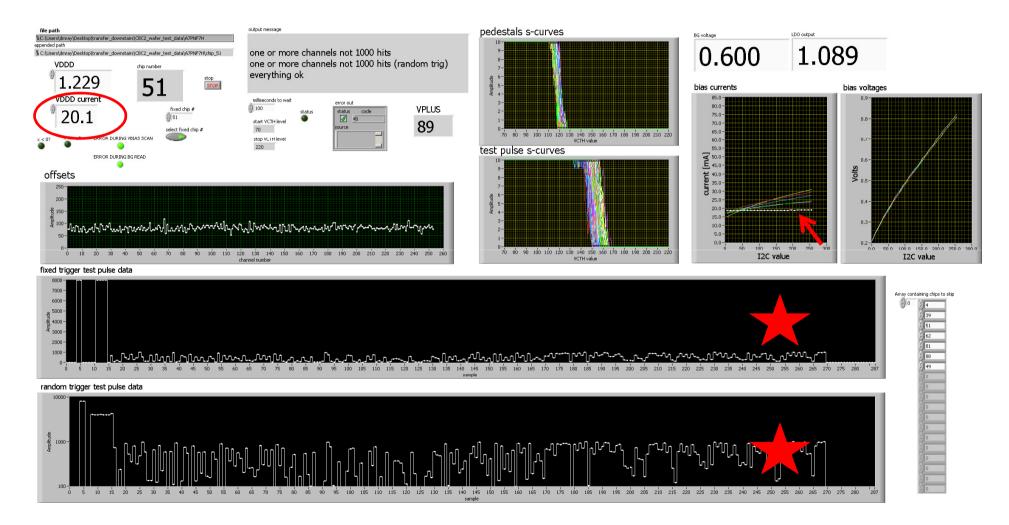

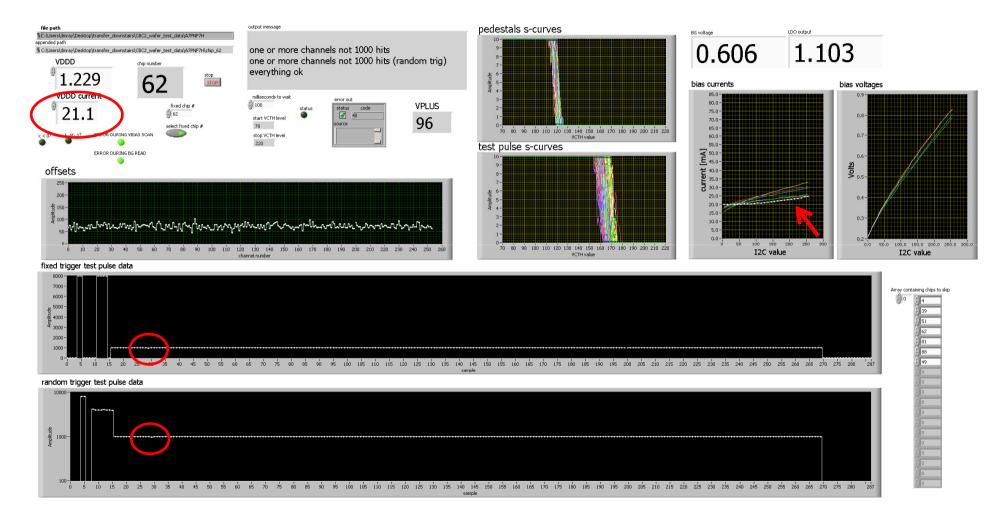

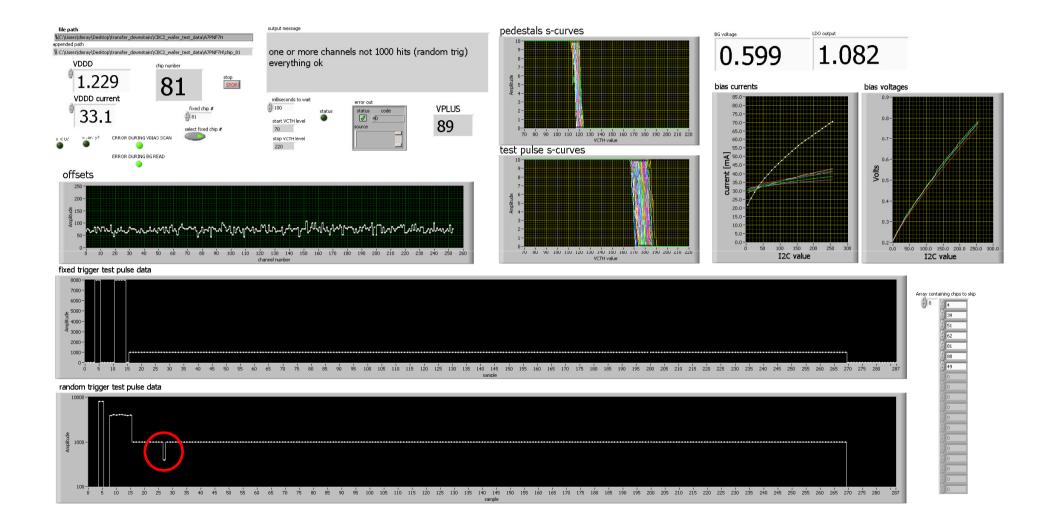

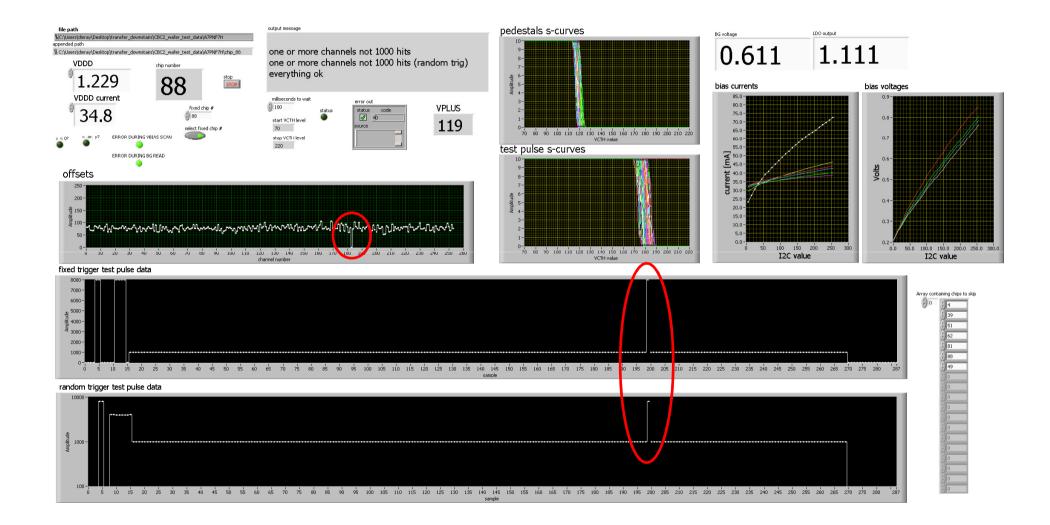

## LabView front panel for individual chip test

latest version used for wafers 3 and 4

analysis of data from wafers 3 and 4 follows

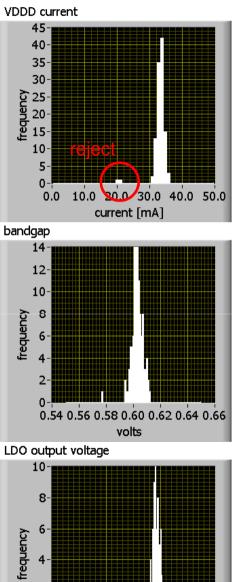

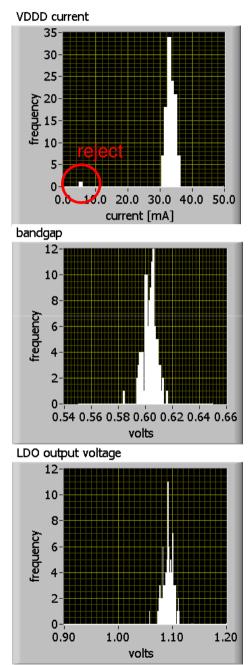

## histograms

data from all chips from both latest wafers

including rejects

bandgap voltage

LDO output

4-

2-

0-

0.90

1.00

volts

1.10

1.20

#### **AVPNC3H**

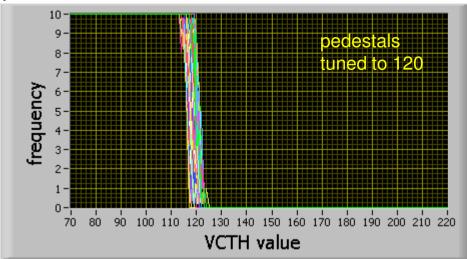

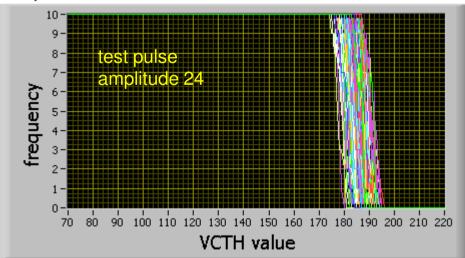

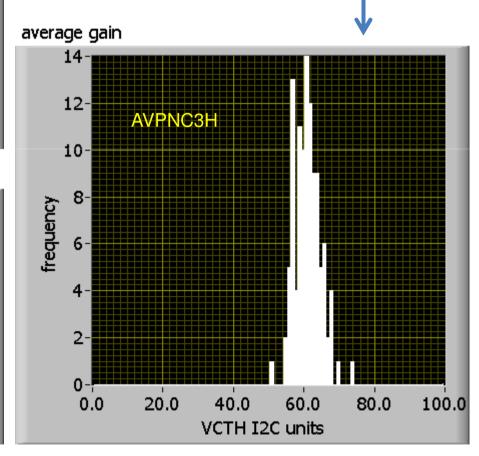

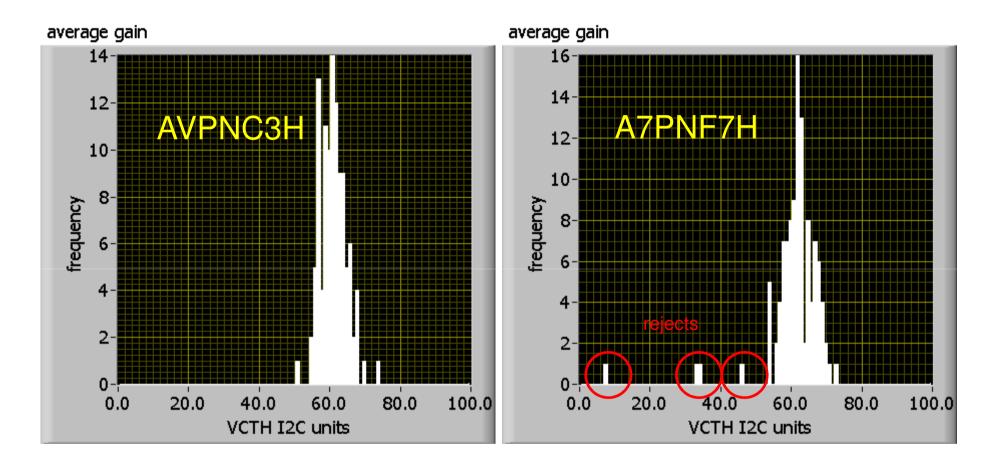

#### s-curves

pedestal s-curves

test pulse s-curves

for each channel subtract pedestal from test pulse (s-curve mid-points)

-> gain for each channel

take average of all 254 channels on the chip

do this for all chips on the wafer and histogram

#### comparing wafers

not much difference in average gain for these two wafers

but relies on test pulse charge injection capacitors matching

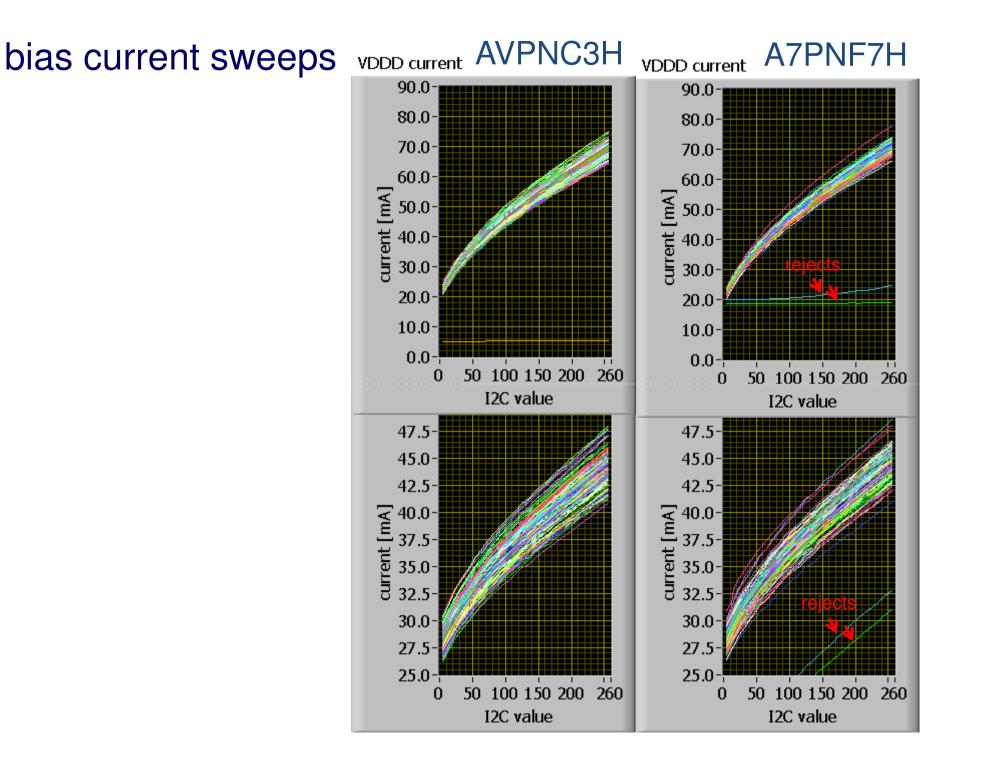

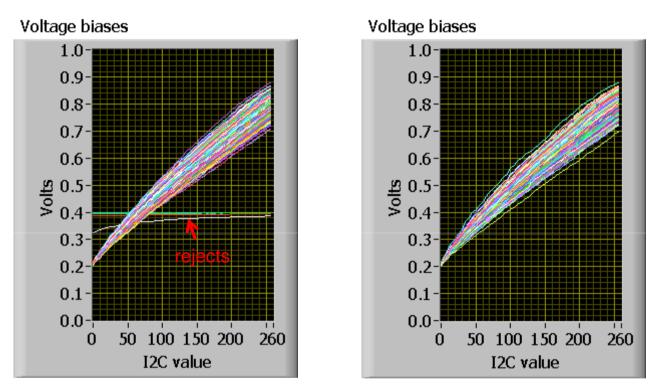

#### bias voltage sweeps

**AVPNC3H**

#### A7PNF7H

all voltage biases (VPC, VPLUS, VCTH, VPAFB) for all chips

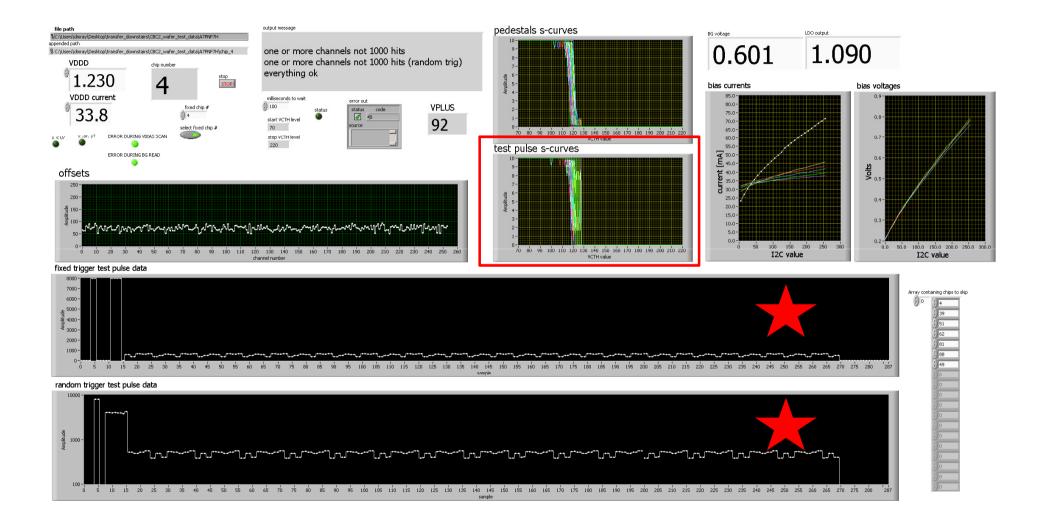

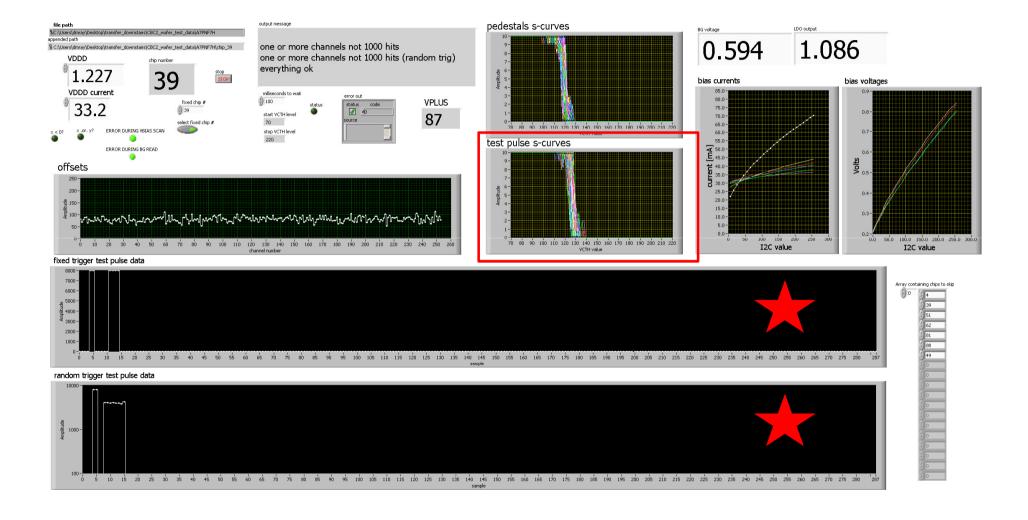

## AVPNC3H chip#1 - small problem

1 bit in pipeline stuck high

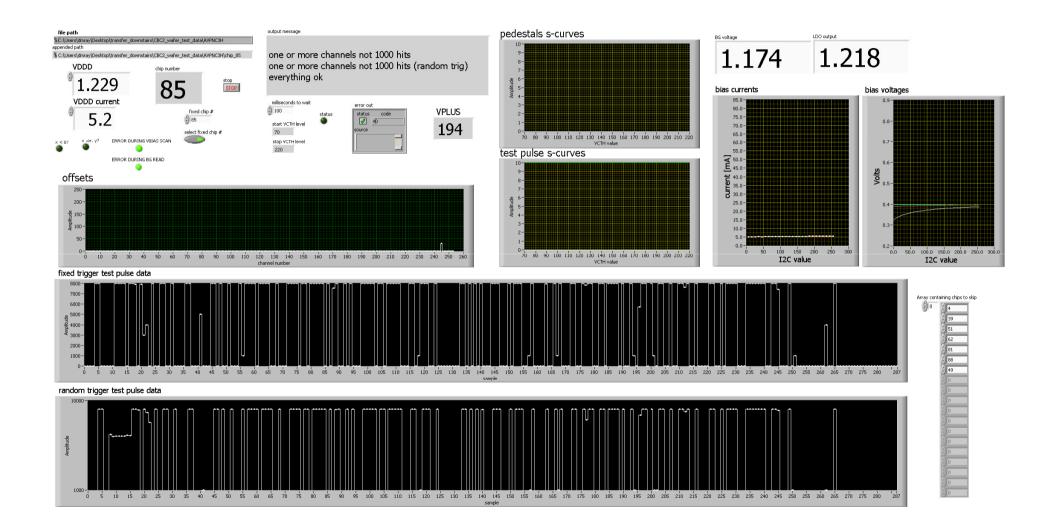

#### AVPNC3H chip#85 - big problem

one bias current not working

IPRE1 not working

IPRE1 not working

1 bit in pipeline stuck low

1 channel output stuck high

#### summary

wafer yields to date

1<sup>st</sup>, 4 rejects (balls damaged)

2<sup>nd</sup>, 5 rejects

3<sup>rd</sup>, 3 rejects

4<sup>th</sup>, 7 rejects (one rejected by eye)

more rigorous test procedure for last 2

test takes ~5 mins per chip

faster I2C would help - present interface runs at 100 kHz

#### extra

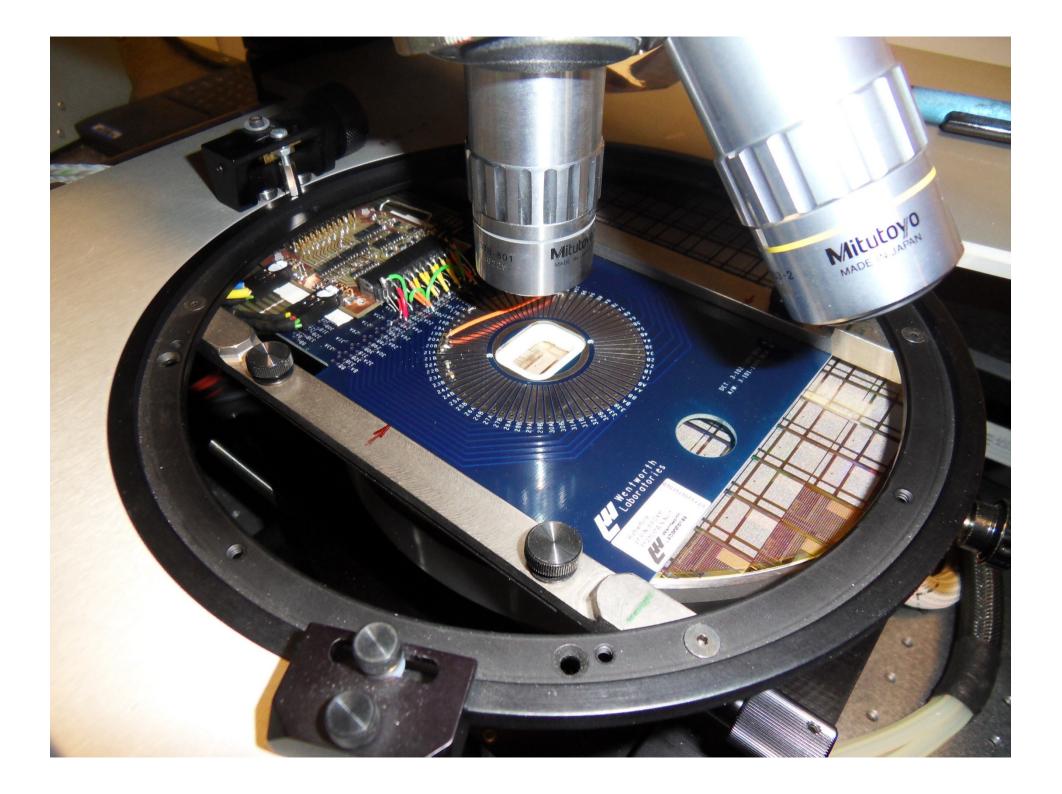

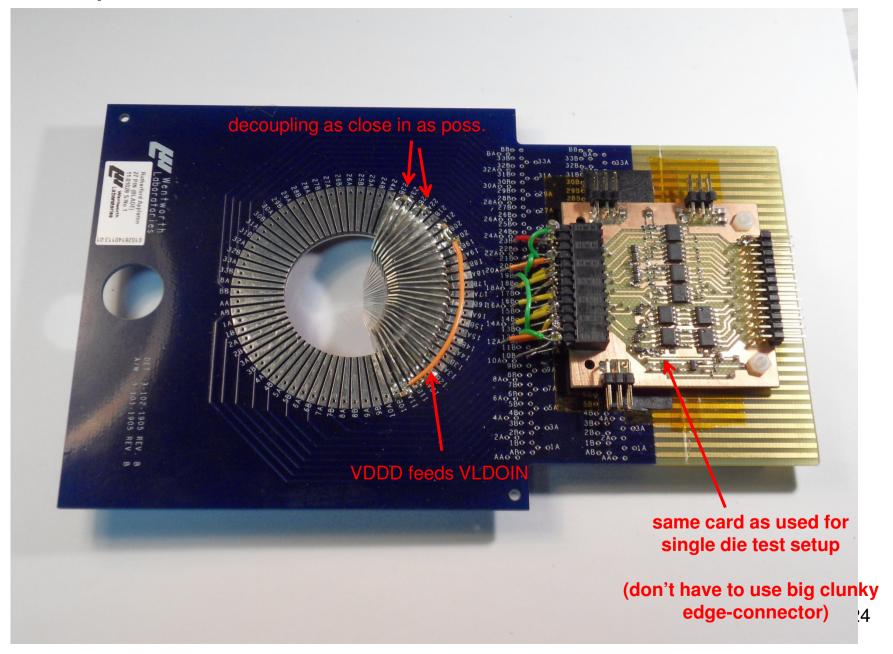

#### blade probe card for CBC2

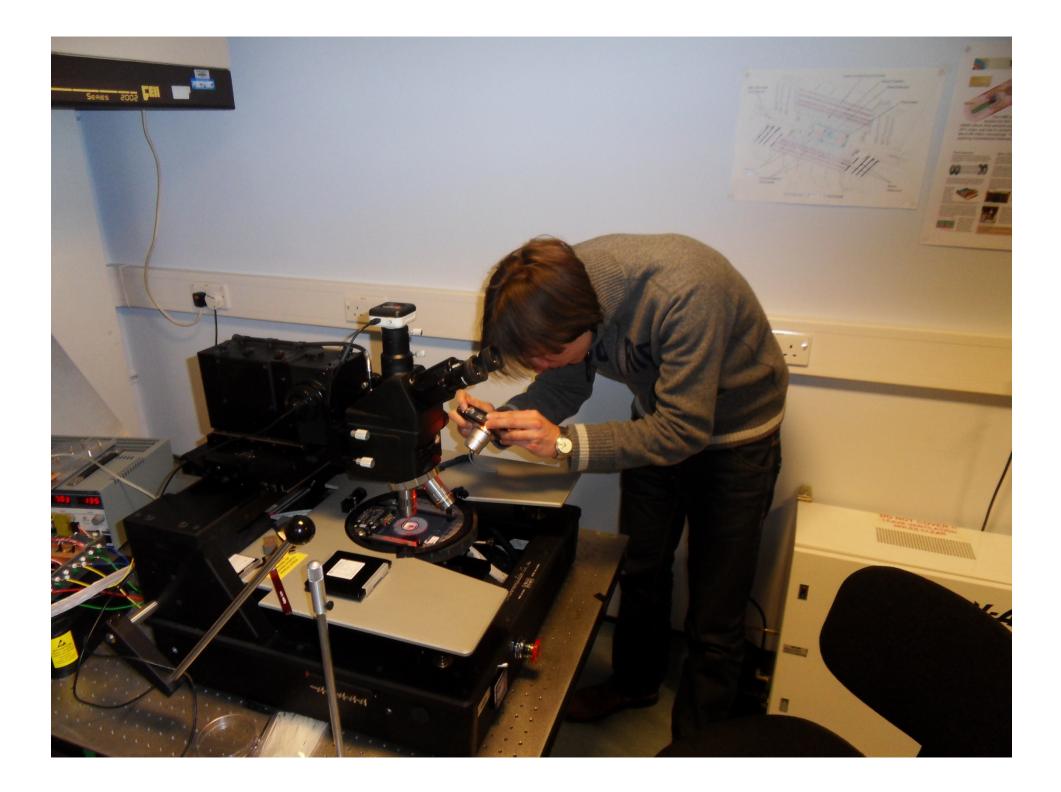

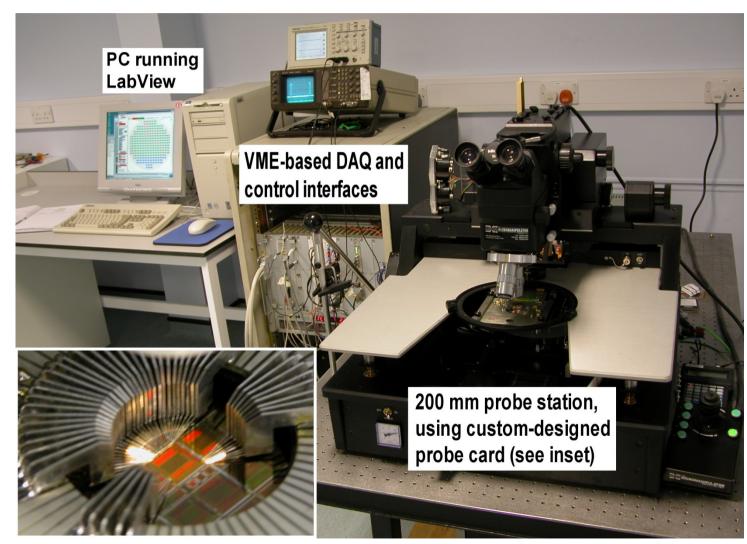

# Wafer Test Probe Station

will re-use some of APV probe-card interface hardware

ancient PC now replaced and probe-station controlling software checked ok

Micromanipulator 8 inch semi–automatic probe station

VME based ADC (8 bits) RAL SeqSi 40 MHz CK/T1 CERN VI2C I/F

PC controls both DAQ (VME) & probe-station (RS232)

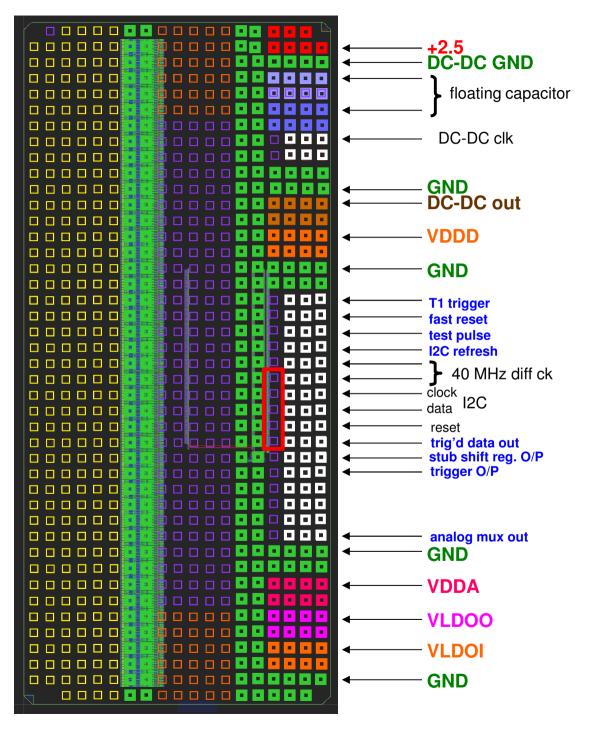

## probe card signals

27 altogether

160 MHz signals left out

can try and use DC-DC and LDO but unlikely to work well necessary associated capacitors a long way away from pads