# **CBC3** preparations

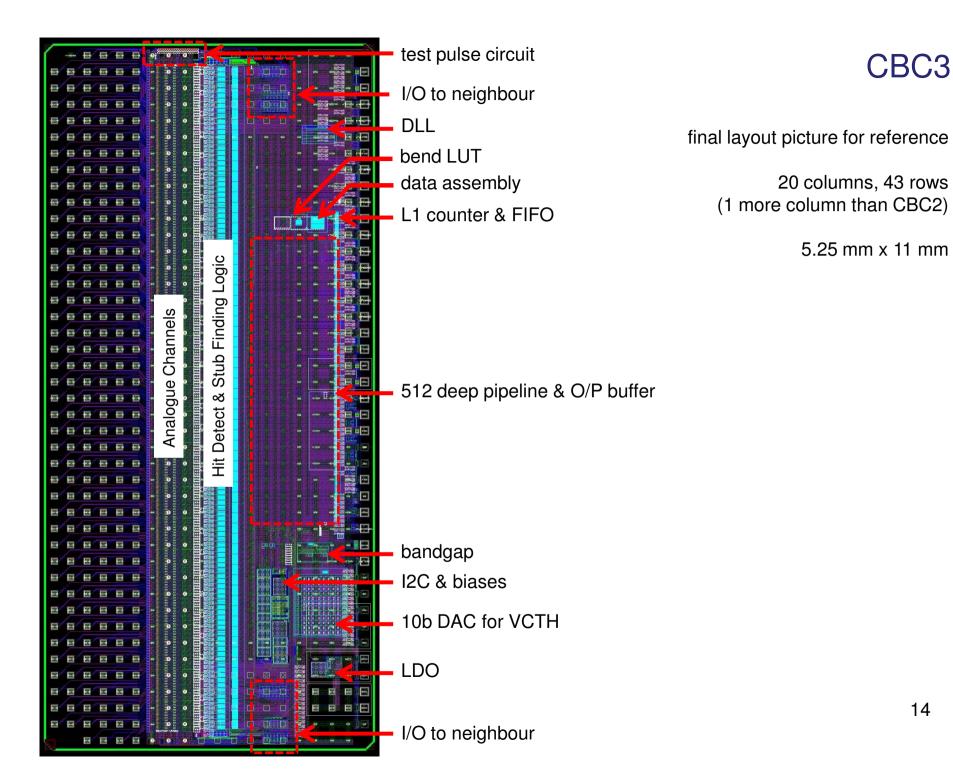

#### CBC3

production status

documentation

test system ideas

hardware & software

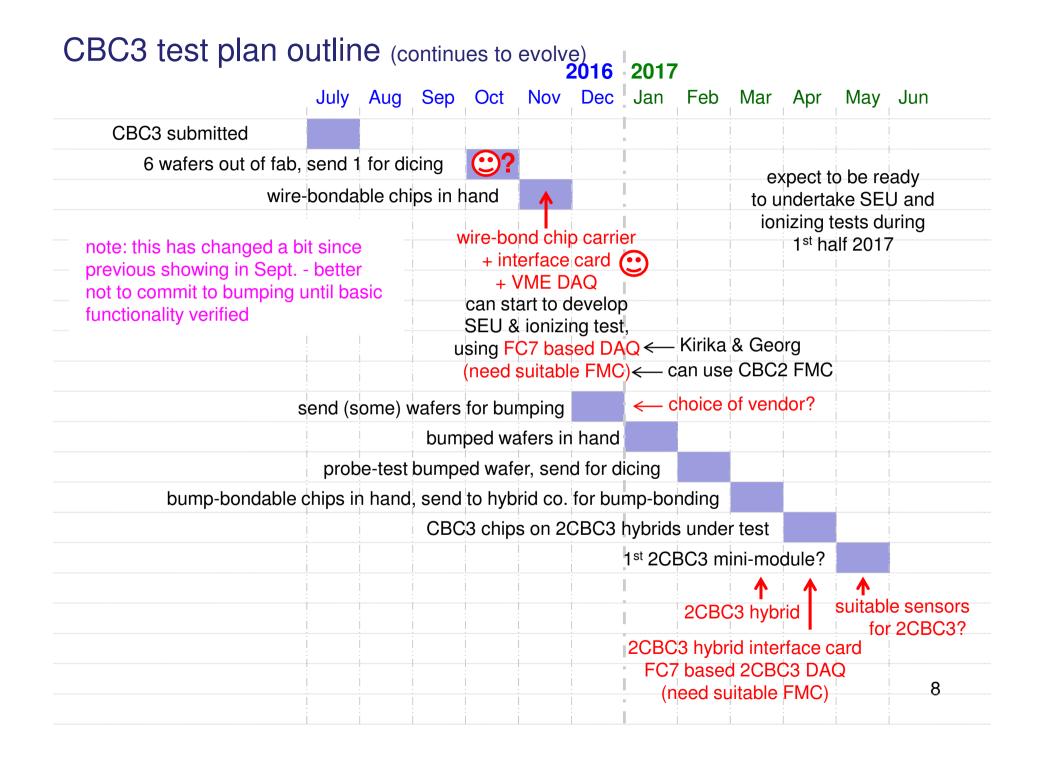

test plan schedule

modelling

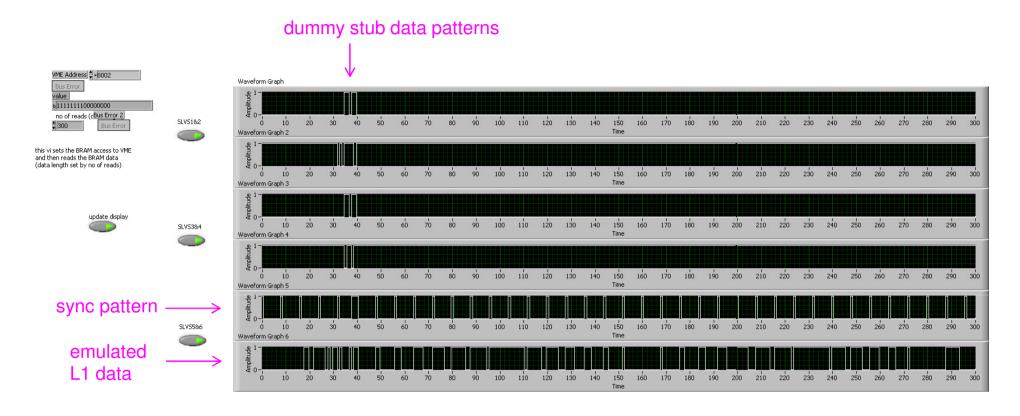

sync pattern generation

systems meeting, 20th September, 2016.

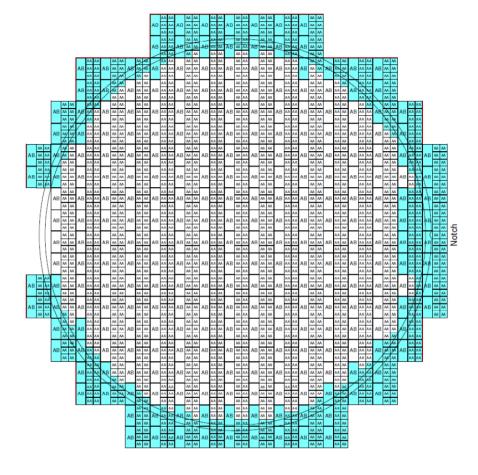

## **CBC3** production

CBC3 sharing wafer with GBT-SCA chip

1 CBC3: 6 SCA

SCA is wire-bond chip CBC3 has one wire-bond column

186 CBC3 chips / wafer

6 wafers shipped from MOSIS to CERN 18th October

1 will be thinned (280 um) & diced

1/2 CBC3 dice (93) available (more than enough)

5 to be used for bumping

=> ~850 bumpable chips

if necessary can buy more engineering wafers later (if available) or a full production lot

## **CBC3** documentation

for the less familiar a user manual is required

will certainly appear, but not yet ready

for more expert users (who want to start preparations now)

spec document describes interfaces

http://www.hep.ph.ic.ac.uk/~dmray/CBC documentation/CBC3 Technical Spec V1p3.docx

I2C address list

preliminary version exists and being used for DAQ firmware/software development

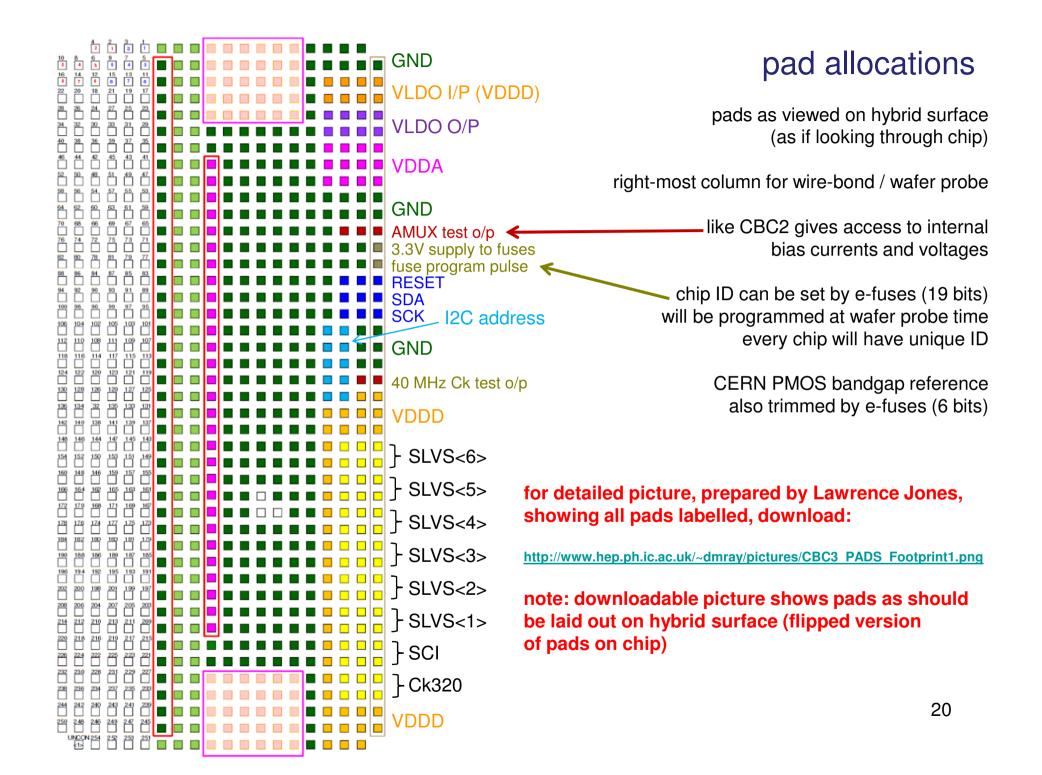

pad layout

http://www.hep.ph.ic.ac.uk/~dmray/pictures/CBC3 PADS Footprint1.png

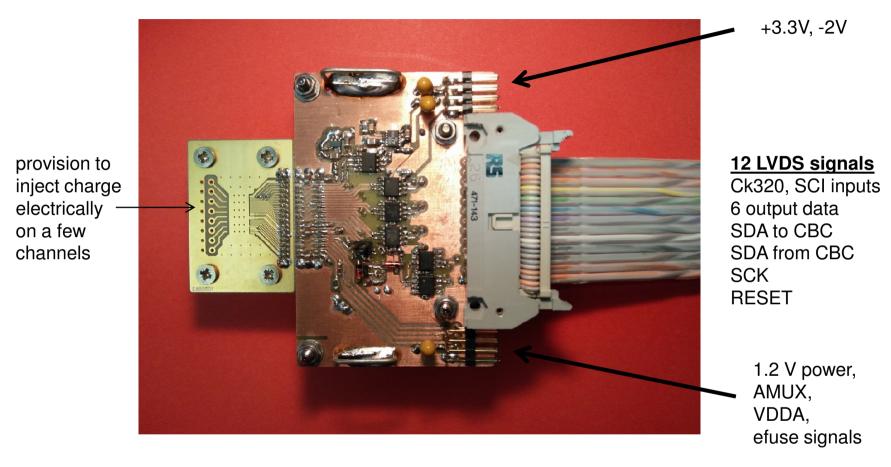

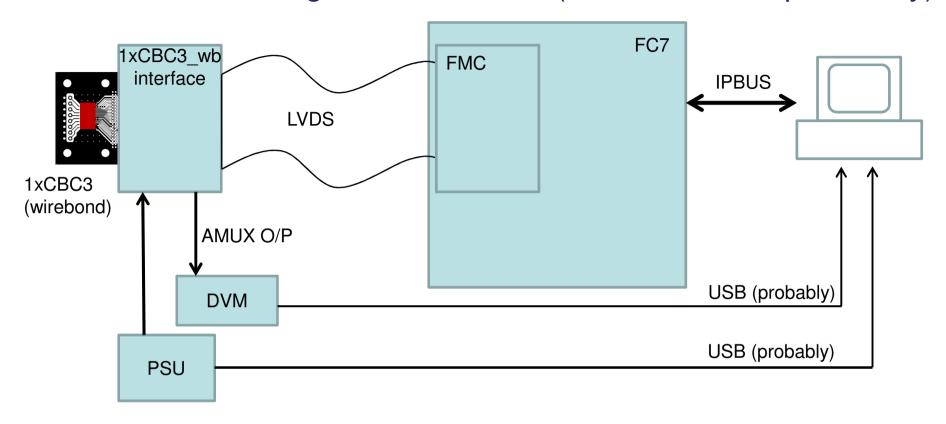

## single wirebonded chip test system

can be connected to VME DAQ and control system

first tests, develop probe tests, efuse blowing, ..

similar interface card will be mounted (piggyback) on probe card ← probe card ordered

can also interface to FMC (FC7)

will be used for ionising and SEU tests

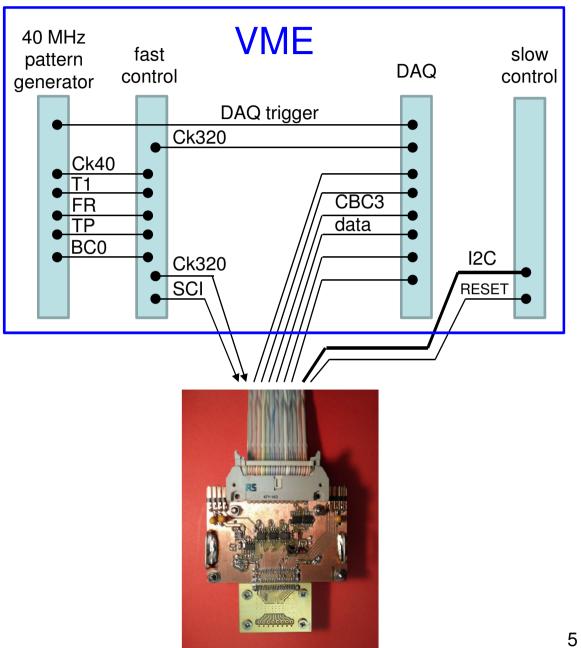

## VME DAQ system hardware

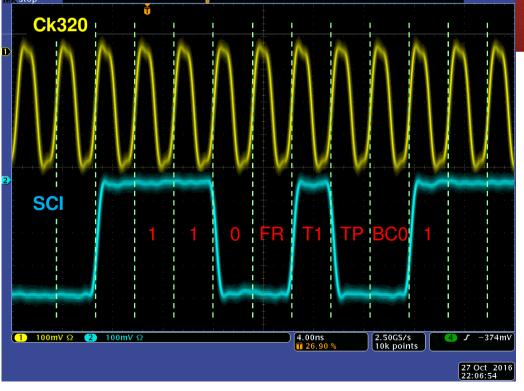

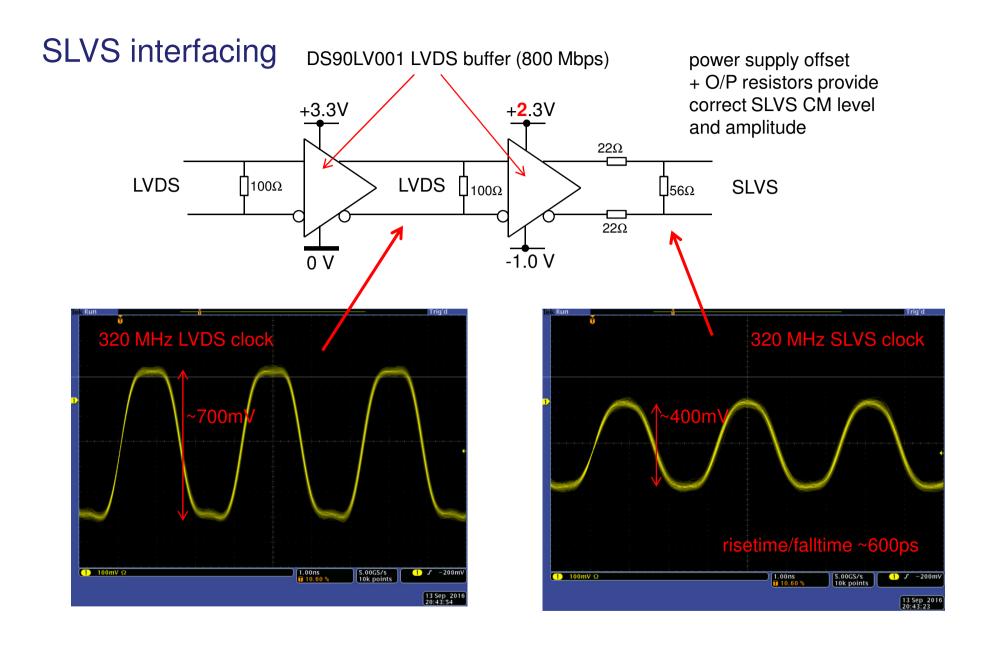

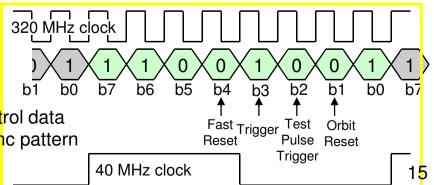

## fast control signals from VME system

LVDS signals buffered by DS90LV001 chips (see last time)

diff. probes here

← 320 MHz

$\leftarrow$  320 Mbps

## basic VME DAQ software ready

# CBC3 system model requirements

- What are the requirements for the CBC3 system model?

- What is it to test or interface to? CIC

- What type of output data is it required to produce?

- What is the level of complexity

- Cycle accurate?

- Simplified FE analogue circuitry as digital on/off signals?

- What tool environment is it to be used in?

- Current status

- Mixed-signal model created and runs with Cadence AMS simulator

- Mixture of RTL, gate level and transistor level blocks are modelled

## CIC sync pattern generation thoughts

SLVS<5> has the sync bit

SLVS<1>, <2>, <3> and <4> can have fixed repetitive data by setting VCTH so that all channels are permanently firing, and then using channel mask to unmask 3 specific seed and window channel combinations

SLVS<6> can also have fixed repetitive data by triggering readout, but not a 25 nsec repetitive pattern

#### SLVS <1> .... <6>

| S1<7> | S2<7> | S3<7> | B2<3> | Sync  | R |

|-------|-------|-------|-------|-------|---|

| S1<6> | S2<6> | S3<6> | B2<2> | Error | R |

| S1<5> | S2<5> | S3<5> | B2<1> | OR254 | R |

| S1<4> | S2<4> | S3<4> | B2<0> | SoF   | R |

| S1<3> | S2<3> | S3<3> | B1<3> | B3<3> | R |

| S1<2> | S2<2> | S3<2> | B1<2> | B3<2> | R |

| S1<1> | S2<1> | S3<1> | B1<1> | B3<1> | R |

| S1<0> | S2<0> | S3<0> | B1<0> | B3<0> | R |

## extra

for SLVS -> LVDS just use one DS90LV001 (0 and 3.3V supplies)

CM acceptance range of LV001 can cope with SLVS levels

## software - for ionizing and SEU tests (assume UK responsibility)

based on CBC2 middle-ware

control and DAQ procedures PSU current monitoring AMUX O/P monitoring processes need to be synchronized (e.g. monitor PSU current and/or AMUX O/P while sweeping I2C parameter) data-logging (time-stamping) required for ionizing tests

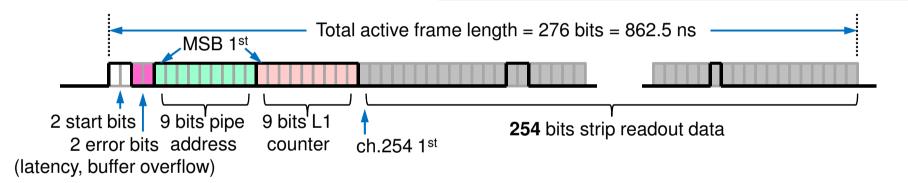

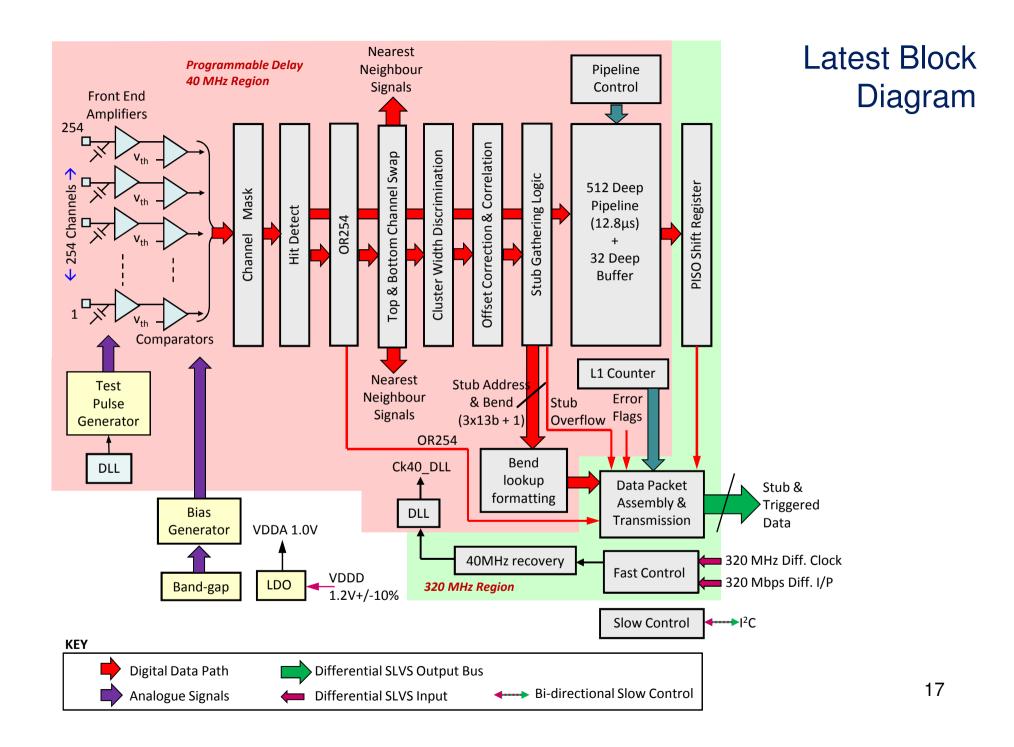

## CBC3 digital interfaces

output data: up to 3 stubs data transmitted to CIC/BX → 6 SLVS diff pairs @ 320 Mbps 25 ns

S1<7> S2<7> S3<7> R B2<3> **Sync** S1<6> S2<6> S3<6> B2<2> Error R S2<5> R S1<5> S3<5> B2<1> **OR254** S1<4> S2<4> S3<4> SoF R B2<0> S2<3> S3<3> R S1<3> B1<3> B3<3> R S2<2> S3<2> B1<2> S1<2> B3<2> S2<1> S3<1> R S1<1> B1<1> B3<1> S3<0> S1<0> S2<0> B1<0> B3<0> R

#### readout data

readout data frame length 950 nsec => up to 1 MHz L1 triggering capability

R = L1 triggered readout data time flow **top** to **bottom** (e.g. S1<7> output first)

#### fast control

320 MHz clock 320 Mbps fast control line

40 MHz generated from fixed sync pattern in fast control data normal command structure can't be confused with sync pattern

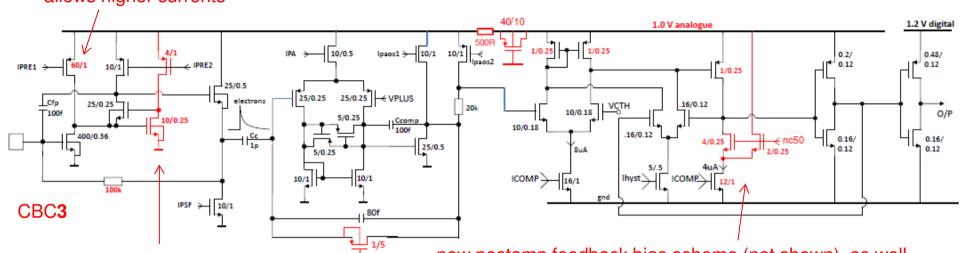

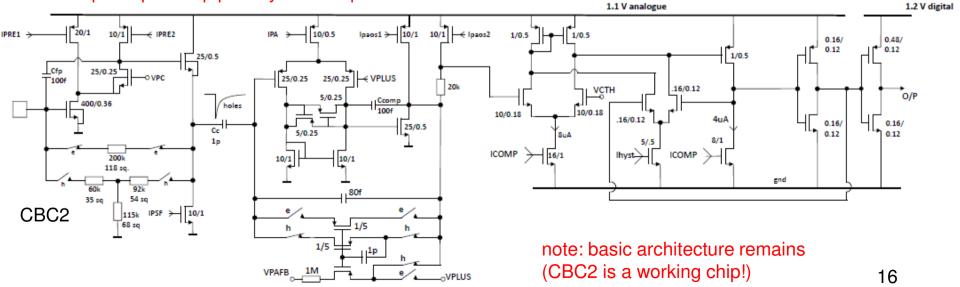

## increase in bias FET allows higher currents

### CBC2 vs. CBC3

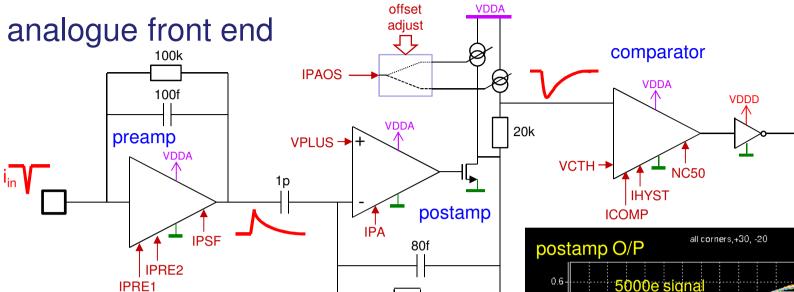

new preamp cascode bias scheme to eliminate "shadow effect"

new postamp feedback bias scheme (not shown), as well as current neutral comparator, addresses CM effects observed when many channels fire

#### pre & postamp polarity switch options removed

VPAFB

**VPAFB**

main design changes

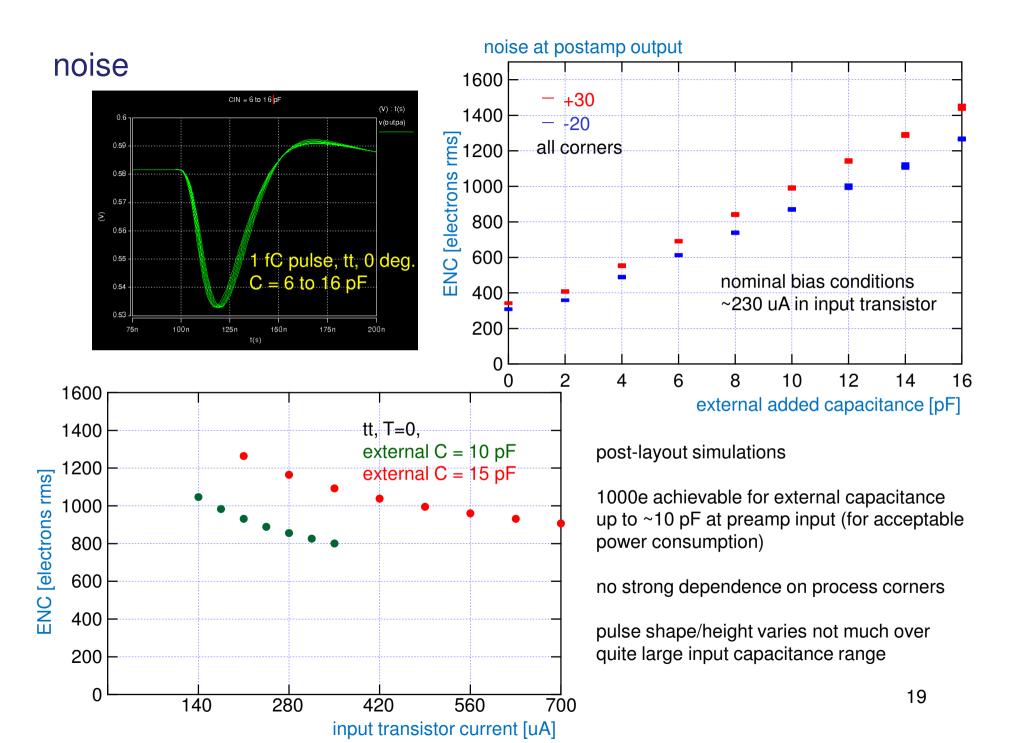

optimised for n-in-p sensors faster shaping (return to baseline within 50 ns) VCTH linear, monotonic and 10-bit CBC2 "shadow" and CM effects addressed

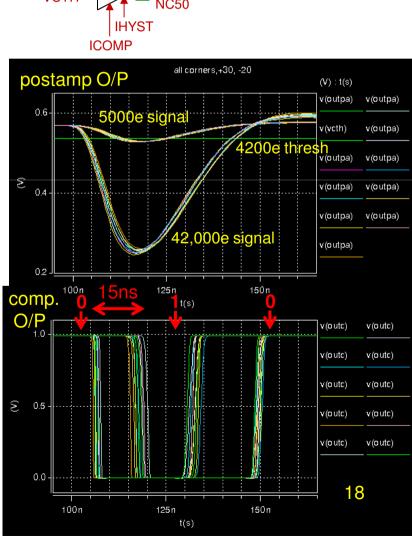

> post-layout timewalk simulation