### CBC3 wafer probe test status

systems meeting, 4<sup>th</sup> April, 2017

## wafer probing

some delay because of a fault with usual prober - had to switch to alternative 300 mm machine

different control instructions and setup procedure => software changes

5 CBC3 wafers now tested and despatched to PacTech - delivered yesterday (3<sup>rd</sup> April)

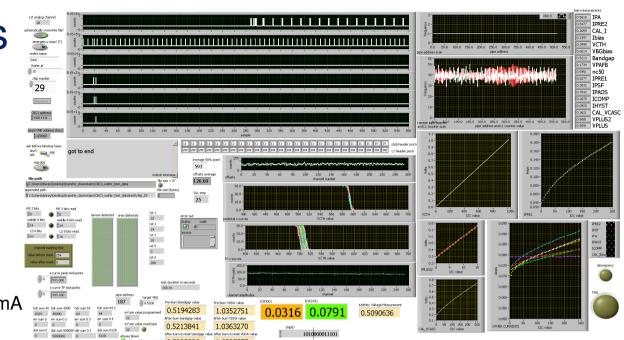

## wafer probe tests

all tests run at full speed (320 MHz)

categorize failures as:

- I2C failure no response stuck bits in registers

- power current too high I<sub>VDDD</sub> > 50mA, I<sub>VDDA</sub> > 200mA

- pipeline any stuck bits

- stub logic

wrong address or bend info returned

chip failed immediately if any test failed up to here

• channel

high/low or non-uniform gain (one or more channels) large spread on offsets after tuning

• other

DLL, physical damage noticed, file not written, ....

for more details on tests see last time:

http://www.hep.ph.ic.ac.uk/~dmray/systems\_talks/2017/CBC3\_status\_Feb\_2017.pdf

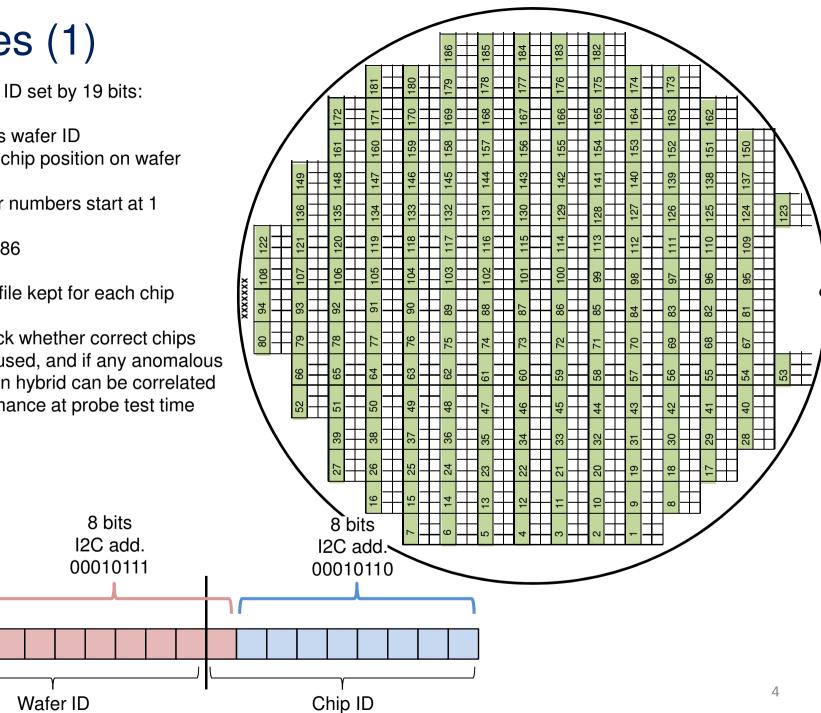

# e-fuses (1)

unique chip ID set by 19 bits:

10 bits wafer ID 9 bits chip position on wafer

CBC3 wafer numbers start at 1

chips 1 -> 186

LS 3 bits

I2C add.

00011000

test results file kept for each chip

=> can check whether correct chips have been used, and if any anomalous behaviour on hybrid can be correlated with performance at probe test time

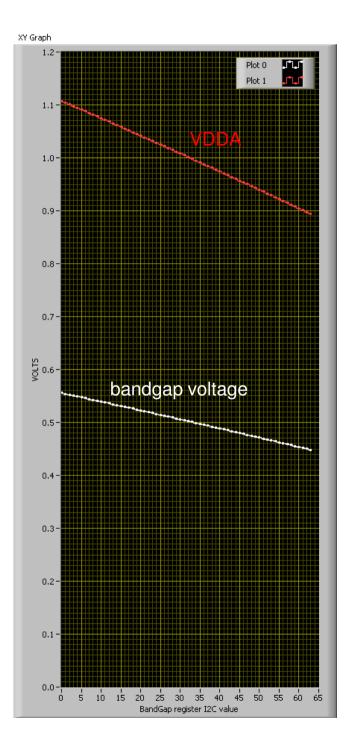

# e-fuses (2)

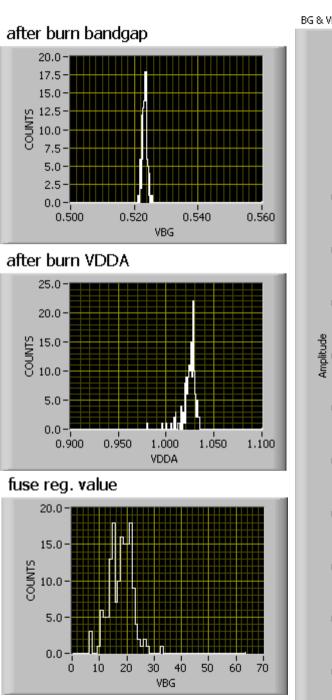

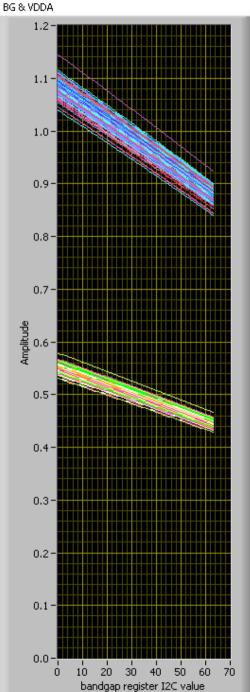

bandgap tune register swept and BG voltage measured through analogue mux

VDDA also measured - should be 2x bandgap

determine register setting which gives voltage closest to desired BG output

for now have chosen 0.52 V as target

(bit arbitrary, decided no need to aim for absolute minimum VDDA)

can be overridden later if desired

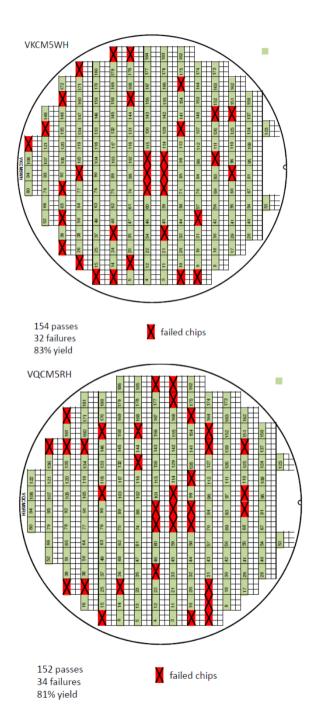

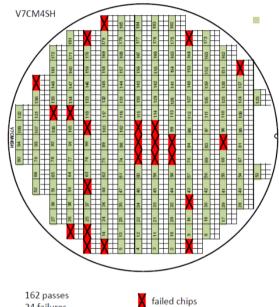

24 failures 87% yield

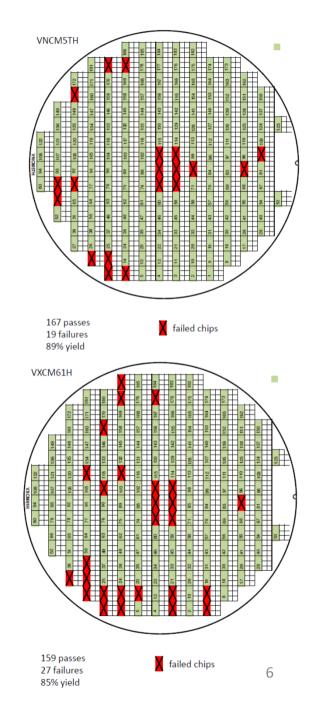

## wafer probe failure summary

|             | VQCM5RH | VKCM5WH | VXCM61H | V7CM4SH | VNCM5TH |

|-------------|---------|---------|---------|---------|---------|

| yield [%]   | 81      | 83      | 85      | 87      | 89      |

| I2C failure | 0       | 5       | 5       | 0       | 2       |

| power       | 0       | 0       | 3       | 0       | 0       |

| pipeline    | 5       | 4       | 0       | 0       | 3       |

| stub logic  | 1       | 1       | 2       | 1       | 0       |

| channel     | 20      | 18      | 14      | 19      | 14      |

| other       | 8       | 3       | 2       | 4       | 1       |

some chips fail in more than one category - first to occur is one listed in table channel failure is largest category - some examples on next slide channel failure if any channel shows gain > +/- 10% from the mean

most (~all) of failures in centre of wafers are channel failures

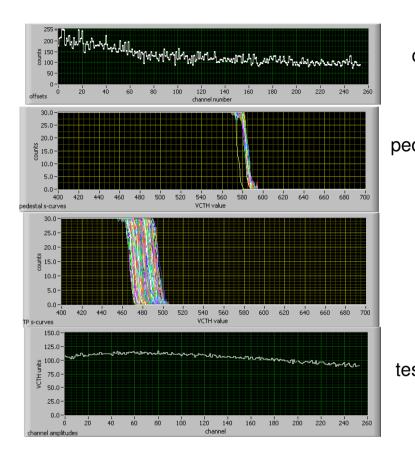

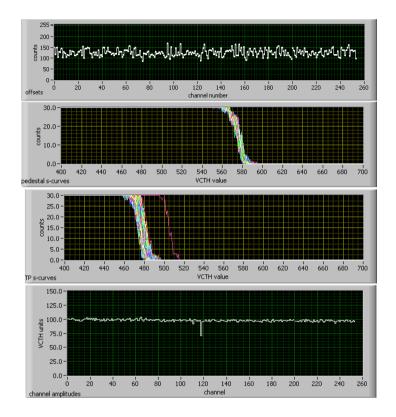

## types of channel failure

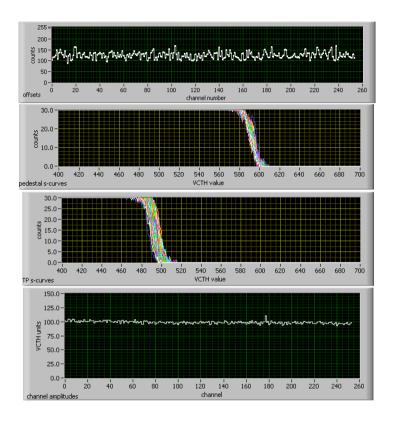

200. נוקילקוביון הרמוביוולמתיקה שלמומין ונוגוטלע המהומיוישל בלמחונטלע לכלוגי גע מטלע איז גע offset values after tuning 180 200 220 240 60 80 100 120 140 160 offsets channel number 30.0 25.0 20.0 pedestal s-curves 원 특 15.0· 10.0 5.0 0.0 620 640 540 560 580 600 660 680 400 420 44n 460 480 500 520 VCTH value pedestal s-curves 30.0 25.0 20.0 test pulse වි 5 15.0 s-curves 10.0 5.0 0.0 480 500 520 540 560 580 620 420 440 460 600 640 660 680 400 VCTH value P s-curves 150.0 125.0 와 100.0 도 test pulse - peds 75.0 CHLD 50.0 ( = gain) 25.0 0.0 60 80 100 120 140 160 180 200 220 20 40 240 channel

channel amplitude

this chip shows an obvious trend across the chip in the gain picture, and also in the offsets after tuning

this problem more often observed on chips at the edge of the wafer

this chip shows a problem on several channels

problem typical of chip in centre of wafer

700

700

## more types of channel failure

single channel with low gain

single channel with slightly high gain but still a failure

### post test data analysis

this first batch of wafer testing was a bit rushed - to get wafers quickly to bumping company

aggravated by problem with usual probing machine

but test protocol was quite thorough, and all chips passed should work well

post test data analysis limited to visual scan through data - chip by chip

more automated post test data analysis can be developed

will be interesting to look for correlations between any bad behaviour observed on hybrids and probe test data

chip ID enables this & also allows us to be certain what chip ends up where

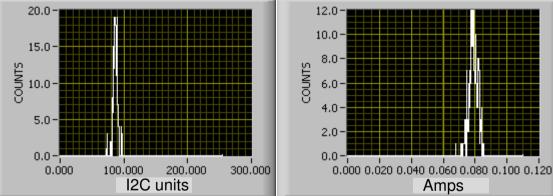

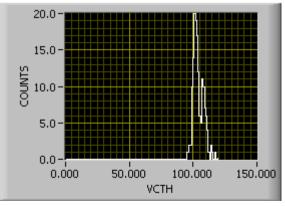

## data examples

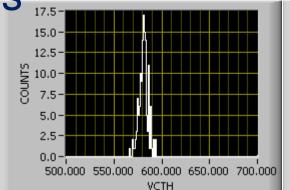

cumulative plots of data for one of the wafers illustrates across wafer spread

all these chips were passed

after fusing bandgap values distribution narrow

larger spread in VDDA values - suspect due to variable probe contact

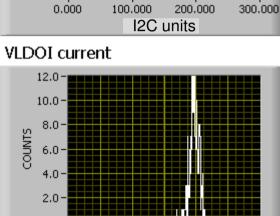

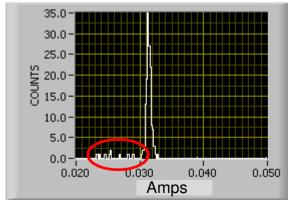

## other data examples ERAGE 50% POINT

all these chips were passed - no obvious performance issues

few chips with low VDDD current values - suspect measurement issue

maybe power supply current not given enough time to settle - needs further investigation

#### MINIMUM OFFSET VALUE

#### **VDDD** current

#### average channel amplitude

MAXIMUM OFFSET VALUE

20.0

15.0

10.0

5.0

$0.0 \cdot$

COUNTS

Amps

#### summary

5 wafers probed and now with bumping company

ability to probe wafers at full speed now confirmed

yield quite high (> 80%) but noticeable pattern of failures in centre of wafers

will further refine probing tests and post test data analysis using remaining 3 wafers