# Report to the Calorimeter R&D Review Panel

CALICE Collaboration June 2007

| 1 |     | cutive Summary                                          |    |

|---|-----|---------------------------------------------------------|----|

| 2 | Ove | rview of the CALICE Collaboration                       | 5  |

|   | 2.1 | Introduction                                            | 5  |

|   | 2.2 | Physics prototype program                               |    |

|   | 2.3 | Technical prototype program                             |    |

| 3 |     | ECAL based on scintillator                              |    |

|   | 3.1 | Introduction                                            |    |

|   | 3.2 | Detector configuration.                                 |    |

|   | 3.3 | Development items.                                      |    |

|   | 3.4 | The prototype detector and its performance              |    |

|   | 3.5 | Beam test at DESY                                       |    |

|   | 3.6 | Future plans and milestones                             |    |

|   | 3.7 | Remaining issues                                        |    |

| 4 |     | ECAL based on silicon                                   |    |

| • | 4.1 | Introduction                                            |    |

|   | 4.2 | The electromagnetic calorimeter concept                 |    |

|   | 4.3 | Current status of the project                           |    |

|   | 4.4 | The prototype in test beam                              |    |

|   | 4.5 | The second generation prototype                         |    |

|   | 4.6 | Schedule of the beam test                               |    |

|   | 4.7 | Alternative option for the silicon active device : MAPS |    |

|   | 4.8 | References                                              |    |

| 5 |     | Tile HCAL                                               |    |

| J | 5.1 | Introduction                                            |    |

|   | 5.2 | R&D programme                                           |    |

|   | 5.3 | Silicon photo-multipliers                               |    |

|   | 5.4 | Operational experience and calibration                  |    |

|   | 5.5 | Future test beam programme                              |    |

|   | 5.6 | R&D towards a realistic tile HCAL for the ILC           |    |

|   | 5.7 | Conclusion                                              |    |

| 6 |     | Tail Catcher and Muon Tagger (TCMT)                     |    |

| Ü | 6.1 | Introduction                                            |    |

|   | 6.2 | TCMT Prototype                                          |    |

|   | 6.3 | TCMT Readout                                            |    |

|   | 6.4 | LED System                                              |    |

|   | 6.5 | Test Beam                                               |    |

| 7 |     | gas Digital Hadron Calorimeter                          |    |

| , | 7 1 | Introduction                                            |    |

|   | 7.2 | Detector R&D                                            |    |

|   | 7.3 | Electronic readout system                               |    |

|   | 7.4 | The HaRDROC-based readout system.                       |    |

|   | 7.5 | Developments beyond the Prototype Section               |    |

|   | 7.6 | Conclusions                                             |    |

|   | 7.7 | References                                              |    |

| 8 |     | VFE development                                         |    |

| J | 8.1 | Introduction                                            |    |

|   | 8.2 | Physics prototype ASICS                                 |    |

|   | 8.3 | Technological prototype ASICs                           |    |

|   | 8.4 | Conclusion                                              |    |

|   | 8.5 |                                                         | 59 |

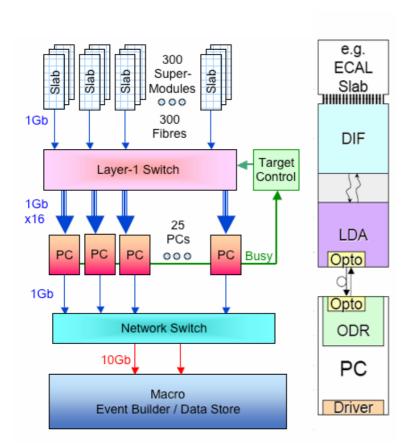

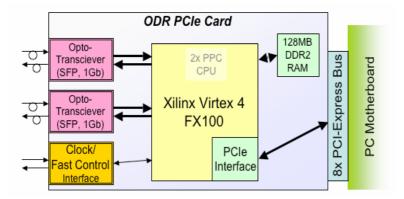

| 9 Tl | he DAQ development                         | 60 |

|------|--------------------------------------------|----|

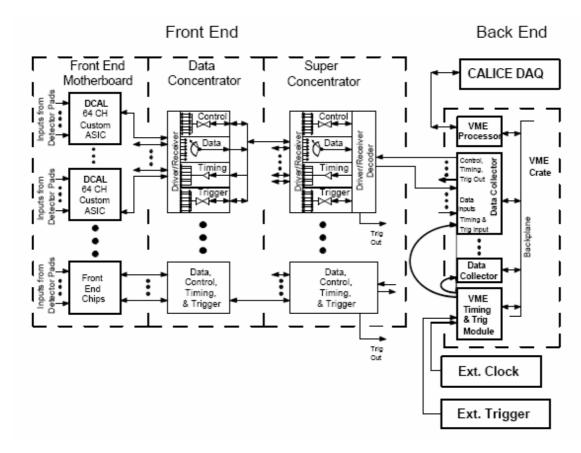

| 9.1  | Overview                                   | 60 |

| 9.2  | Layout                                     | 60 |

| 10   | The software for CALICE R&D                | 64 |

| 10.1 | Introduction                               | 64 |

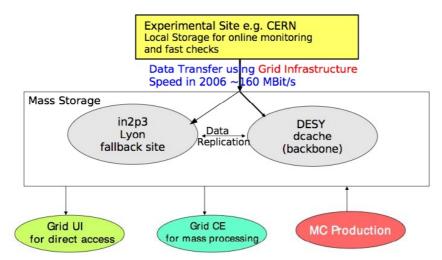

| 10.2 | Data Transfer and Management Scheme        | 64 |

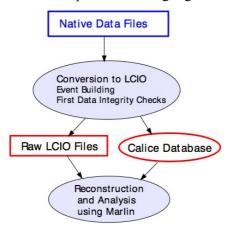

| 10.3 | Data Processing Scheme                     | 65 |

| 10.4 | Software Details                           | 65 |

| 10.5 | Summary and Outlook on software for CALICE | 66 |

| 10.6 | Bibliography                               | 66 |

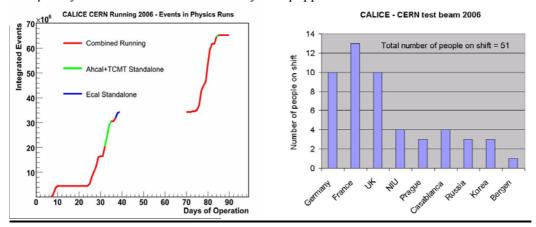

| 11   | The test beam effort                       | 67 |

| 11.1 | Overview                                   | 67 |

| 11.2 | Beamline installation                      | 67 |

| 11.3 | Calorimeters                               | 67 |

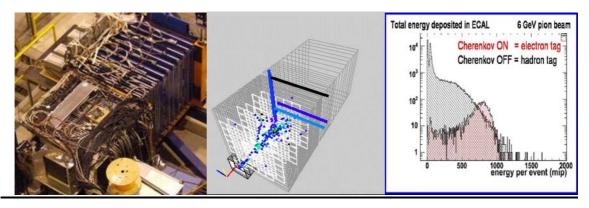

| 12   | First preliminary test beam results        | 69 |

| 12.1 | Introduction                               | 69 |

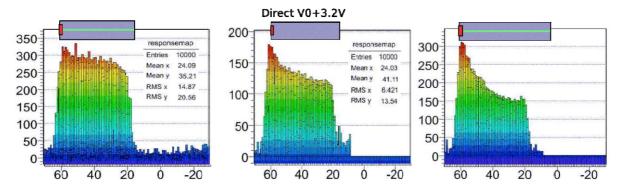

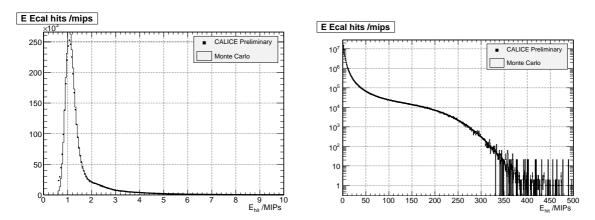

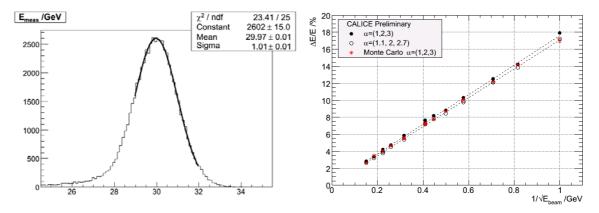

| 12.2 | The ECAL data                              | 69 |

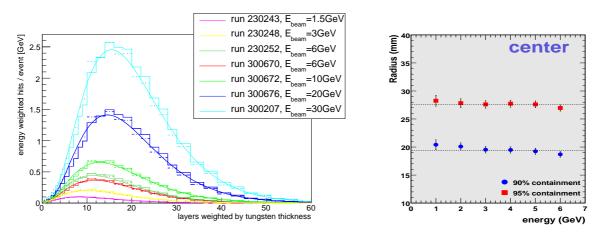

| 12.3 | The AHCAL data                             | 71 |

| 12.4 | Combined calorimeter data                  | 73 |

|      |                                            |    |

## 1 Executive Summary

The CALICE collaboration is undertaking a major program of R&D into calorimetry for the ILC. It has members from many institutes and is represented in all three major ILC regions. The collaboration has a coordinated approach and, due to its size, is able to efficiently share its expertise across many different detector studies.

The main direction of the collaboration R&D is to study particle flow (PFA) calorimetry, software compensation and individual particle reconstruction. As such, the studies are concentrating on fine granularity calorimeters with a high degree of longitudinal segmentation. These studies include comparison of simulation models with data to measure their degree of agreement, the technical issues of building a detector optimised for PFA calorimetry, and development of algorithms for software compensation and particle flow reconstruction.

The collaboration is studying several technologies for electromagnetic and hadronic calorimeters with a goal of comparing their performance in terms of ILC physics requirements. By performing this work within a common framework, a meaningful comparison of the various proposed detectors can be made.

Two major electromagnetic calorimeter prototypes have already been built and exposed to beam within the last year. A major dataset of around 100 million events was accumulated, covering a wide range of energies and incident angles with both electrons and pions. The data from these beam tests are being analysed and first results are now available. Calibration and correction procedures are still at too preliminary a stage to quote final resolutions, but the detector performance is in reasonable agreement with simulation expectations.

The first hadronic calorimeter prototype was also run in the beam tests last year. A significant amount of data was acquired, both with this calorimeter alone and combined with the electromagnetic calorimeter and again, preliminary results from the analysis of these data are now ready. The first stage was to understand the response to electromagnetic interactions and compare to simulation. Having verified the level of agreement of the detector response, then measurements of hadronic showers become meaningful and results on these studies are now becoming available.

These tests will continue over at least the next 18 months to incorporate several other electromagnetic and hadronic detector technologies and so allow comparisons between them. These will be done with identical mechanical structures where possible so as to keep systematic differences under control.

The large size of the CALICE collaboration allows a high degree of shared experience, effort and equipment. Many of the various detector technologies use the same on- and off-detector readout electronics. They all share the same DAQ and online software system. The offline software is also common to all studies. To allow rapid and easy access to data throughout the collaboration, data management and processing are widely based on grid tools.

Beyond the beam tests, ILC-like prototypes are planned to address the mechanical, technical and integration issues of a realistic detector. These will again include several electromagnetic and hadronic calorimeter technologies. They will also use a DAQ system which would meet the requirements of such a system for the ILC.

We believe an appropriate evaluation of calorimeter technologies for the ILC can only be made by a direct comparison of the options within a well-controlled environment. Such an approach results in a high degree of commonality, leading to a more efficient use of resources, both in terms of funding and effort. We also believe this broad program of work is best coordinated by the experts involved directly in the studies. The CALICE collaboration has already made significant progress towards fulfilling these goals and aims to complete them over the next few years.

## 2 Overview of the CALICE Collaboration

#### 2.1 Introduction

The CALICE collaboration is undertaking a major program of R&D into calorimetry for the ILC, directed towards the design of an ILC calorimeter optimised for both performance and cost. It now has over 200 members from 41 institutes worldwide including all three major ILC regions, and is by far the largest group studying calorimetry for the ILC. New groups continue to join CALICE and these have recently included institutes in India, Canada and Spain.

The main direction of the collaboration R&D is to study particle flow (PFA) calorimetry and software compensation. This is a very broad area and there are many proposals for ways to build a calorimeter optimised for such a concept. Really determining which is the "best" solution would be a difficult task without a systematic and fair comparison of the options. One critical aspect of CALICE is that it is a large enough collaboration that it can study a significant number of these options and can ensure that they are compared in a meaningful way. Specifically, CALICE covers both electromagnetic calorimeters (ECAL) and hadronic calorimeters (HCAL). However, within these broad ranges, it also covers digital (also called binary) and analogue readout for both types of calorimeter. For the ECAL, CALICE groups are studying silicon and scintillator sensitive layers, while for the HCAL, the collaboration is looking at several scintillator and gas detectors. There is a common mechanical converter structure for comparing both the analogue and digital HCALs and similarly there will be a common structure for the comparing the analogue and digital silicon ECALs. Furthermore, the collaboration also includes R&D into tail catcher and muon tagger (TCMT) detectors, which should allow an optimisation of the calorimeter design in terms of the HCAL interaction length compared to cost.

There are two main R&D directions within CALICE; the "physics prototypes" and the "technical prototypes". These have very different aims. The physics prototypes are being used to acquire large data samples in beam tests so that the agreement of the various available physics simulations can be checked. This will allow the design and optimisation of ILC detectors based on similar technologies with a high degree of confidence in the simulation. In contrast, the technical prototypes are designed to be a first attempt at building semi-realistic "ILC-like" calorimeter modules. These are intended to give crucial information on the real integration issues and constraints of building such a calorimeter.

The size of the collaboration means it can benefit enormously, in terms of efficiency, effort and cost, from sharing many aspects of the R&D work. Specifically, for the physics prototypes, the design, and indeed physical boards, of the readout electronics is common for the silicon ECAL, scintillator ECAL, scintillator HCAL and TCMT and there are plans to use them further for the one of the gas HCALs. The DAQ online software and raw data format has been common for all detectors used in the beam tests and future physics prototype beam tests will also use these collaboration-wide tools. These data all have a common offline format, specifically LCIO, which allows shared analysis techniques throughout the collaboration. This common offline structure is also used for ILC physics and global detector studies, allowing the output of the beam test studies to be efficiently transferred into detector optimisation work.

Longer term, the technical prototypes will also have large amounts of commonality. The front-end, on-detector electronics for several of the detectors will be implemented in ASICs all designed in a similar fashion. Furthermore, the second generation DAQs for use with the technical prototypes will have a common basis. This will again allow a single set of off-detector readout electronics, control/timing and online software to be used for all such tests. For analysis of the data, again a common offline software format will be used for all detectors.

We believe this coordination not only makes CALICE highly efficient in terms of cost and effort, but also allows the collaboration, possibly uniquely, to make meaningful and systematic comparisons between the various calorimeter technology choices for the ILC.

## 2.2 Physics prototype program

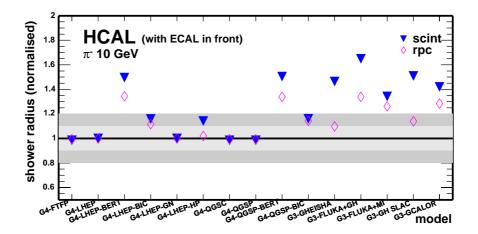

The goal of producing a calorimeter which is capable of delivering the best PFA and software compensation performance requires detailed simulation studies. However, particularly for hadronic interaction simulations, the simulation models can vary substantially between each other. Figure 2-1 shows an example of these differences, specifically a comparison of the shower radius for 10GeV pions in the HCALs, using various simulation physics models. This shows that there are differences of up to 60% between the models and that both scintillator and gas calorimeters have these uncertainties. This is a significant issue in any calorimeter design work.

Figure 2-1: Radius of showers from 10GeV pions in both scintillator (blue triangles) and gas (pink diamonds) HCALs as a function of various simulation models.

To overcome this problem, CALICE is conducting a major physics prototypes program, which involves testing the two main ECAL technologies along with at least two types of HCAL technology in electron and hadron beams. Since the degree of simulation agreement will depend on the technology, this must involve calorimeter prototypes with detector technologies and materials close to those proposed. This will allow differentiation between the many available models so as to use one which agrees well with data and hence enable the optimisation of the ILC calorimeters to proceed with confidence. An additional aim of the physics prototypes program is to gain experience of operating real calorimeter systems with the proposed technology and to measure their performance. This is considered a crucial intermediate step to designing a larger scale detector, particularly as many of the proposed technologies are novel. The physics prototype beam test campaign started at DESY with an electron beam in May 2006 and continued at CERN with electron and hadron beams in the summer of 2006. Further data were taken at DESY in March 2007. For the future, a second CERN run is scheduled for summer 2007 and a run will take place at FNAL on the same timescale. Following this, the focus will move to FNAL by the end of 2007. There will be beam tests with electron and hadron beams at FNAL at various periods throughout 2008.

Historically, the first ECAL physics prototype was the silicon-tungsten sampling calorimeter with analogue readout. It consists of 30 layers of silicon wafers interspersed between tungsten sheets. Each wafer layer contains a 3×3 array of silicon wafers, each containing 36 1×1cm² diode pads. There are around 10,000 channels in total occupying a volume of approximately (18cm)³. The ECAL assembly bas been paced by the silicon wafer production and there were delays in this production during 2005 and 2006. However, these have now been overcome and the total required number of functional wafers is now effectively in hand. Around 80% of these have now been assembled into detector planes and the rest are expected to be completed by July 2007. The readout is through a custom on-detector ASIC and VME readout boards. The prototype was exposed to beams at both DESY and CERN in 2006 when approximately half and two-thirds

complete, respectively. The upcoming CERN and FNAL beam tests in 2007/8 will be with the completed calorimeter.

The second ECAL physics prototype is a scintillator-tungsten sampling calorimeter, again with analogue readout. It consists of 27 layers of scintillator strips, with each layer covering an  $18 \times 18 \, \mathrm{cm}^2$  area. The scintillator strips are  $1 \times 4.5 \, \mathrm{cm}^2$  in their transverse dimensions and each layer contains a  $4 \times 18$  array of strips, for a total of around 2,000 channels. This calorimeter uses silicon photomultipliers (SiPM) to detect the scintillator light. In addition, it uses the same on-detector electronics as the scintillator HCAL (see below) and the same readout electronics as the silicon ECAL. This reuse of existing equipment and expertise illustrates well the power of a large collaboration like CALICE. A test stack of one-quarter size (the full depth of 27 layers, but with only a  $9 \times 9 \, \mathrm{cm}^2$  area in each layer) was assembled and tested in a beam at DESY in March 2007. The rest of the physics prototype is under construction and will be completed in January 2008 for the FNAL beam tests in that year.

The scintillator HCAL is a sampling calorimeter with 38 layers of steel absorber sheets instrumented with scintillator tiles which have analogue readout using SiPMs. Each layer has a 96×96cm<sup>2</sup> area and the total volume is approximately (1m)<sup>3</sup>. The tiles are of varying sizes, with the highest granularity central region using 3×3cm<sup>2</sup> tiles, increasing to 12×12cm<sup>2</sup> for the outermost tiles. This HCAL has around 8,000 channels in total. The readout from the SiPM is through a custom on-detector board (which was reused by the scintillator ECAL). The HCAL then uses the same VME readout boards as both ECALs. The HCAL assembly has been mainly paced by the manufacturing rate of the SiPMs used to read out the tiles. These are now all in hand and the HCAL will be fully assembled by May 2007. Around two-thirds of the layers were installed in time for the CERN beam tests in summer 2006. The completed detector will take data at CERN and FNAL in 2007/8.

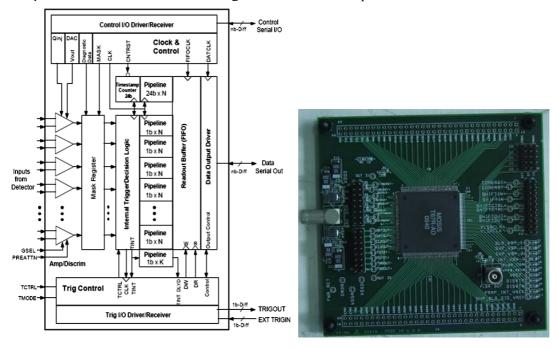

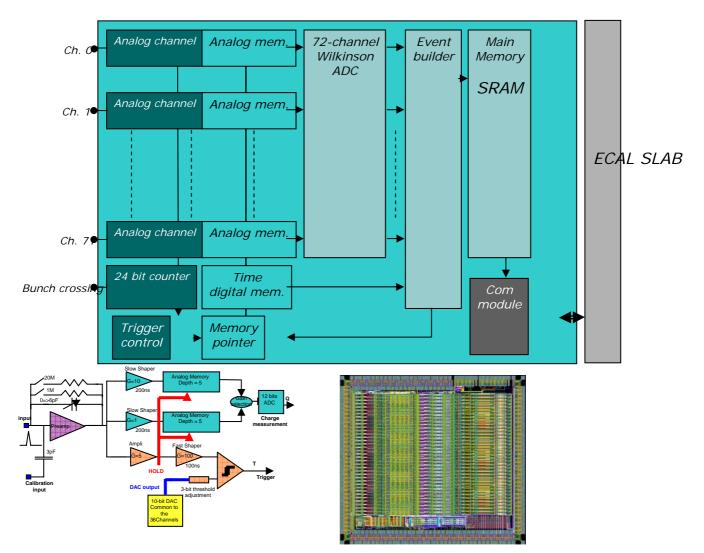

The digital HCAL is a binary readout gas-steel sampling calorimeter. The sensitive layers will be mainly resistive plate chambers (RPC) although as the tests progress, one or more layers, up to the complete stack if production goes smoothly, will be replaced with gas electron multiplier (GEM) or micro-megas detectors. This will give invaluable experience of operating all these detectors and will allow their performance in terms of crosstalk, noise rates, etc, to be measured in realistic operating conditions. In all cases, the pads will be 1×1cm<sup>2</sup>, giving around 350,000 channels, each reading one bit. The readout electronics for the HCALs are based on on-detector, custom-designed ASICs which can run with ILC-like timing as well as in triggered mode as needed for the beam test. As such, they already fulfil many of the requirements of a second-generation technical prototype readout chip. These ASICs can be used with all the gas technologies and so will allow the different detector types to be tested in a very similar environment. The off-detector readout will be through VME, simplifying the integration into the common DAQ and online software system. As one of the main aims of the beam tests is to compare the performance of the various HCAL options, the same absorber structure and tail catcher as for the scintillator HCAL will be used for all cases, so as to eliminate any spurious differences which might otherwise arise. Hence, the digital HCAL will also be around (1m)<sup>3</sup> in volume. A test with layers of a smaller area, but still using the full readout chain, will take place at FNAL in summer 2007 and this will incorporate both RPC and GEM detectors. The full-size version of the gas HCAL physics prototype should be completed by the middle of 2008 and will then take data at FNAL.

The HCALs are complemented by a TCMT detector consisting of 96cm of iron instrumented with 16 layers of 5mm×5cm scintillator strips, which tag shower leakage and detect muons. It has a total of around 300 channels. The scintillator strips use the same SiPM readout as the scintillator HCAL and also have the same downstream readout electronics, again demonstrating the efficiencies of collaborative R&D. The TCMT detector was completed in 2006 and took data in the CERN beam tests that year. It will also participate in the beam tests at CERN and FNAL in 2007/8.

#### 2.3 Technical prototype program

The technical prototype program is growing rapidly and has expanded significantly in the last year. The aim of this effort is to understand the real-world issues of building a calorimeter for the ILC. Hence, the technical prototypes are being designed to be a "best guess" of how such a calorimeter module might look

in terms of mechanical structure, cooling, sensitive layers, on-detector electronics and off-detector readout. As such, they will give an indication of the likely integration issues and so will be invaluable for the eventual detector technical designs.

These "ILC-like" calorimeter modules will be tested in beam when complete and this part of the program is scheduled to start in 2009. However, unlike the physics prototypes, the aim would not be to accumulate a high statistics sample for comparison with simulation, but to assess the functionality (signal/noise, leakage, timing resolution, etc.) of the modules. As such, they do not need to be fully populated. This effort started with the EUDET grant, which provided funding to help build technical prototypes of the silicon ECAL and the scintillator HCAL. The expansion of the gas HCAL effort to include European groups has enabled work to start on a gas HCAL technical prototype also. There are no firm plans for a scintillator-tungsten ECAL technical prototype at this stage.

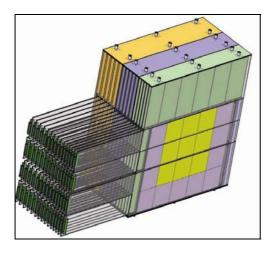

The ECAL technical prototype will be mechanically the size of a LDC current design detector ECAL module. This is specifically 1/40 of the total barrel calorimeter, being approximately 1×1.5m² in area and 30 layers deep. It will be partially equipped with silicon wafers; the middle third of the module will have 28 of the 30 layers equipped for 1/7 of their length while the remaining 2 layers of the 30 will be fully populated. The module is scheduled to be completed in 2008 and exposed to beams from mid 2009 onwards. In addition, as the tests progress, several layers will be replaced with digital ECAL MAPS sensors, allowing a controlled comparison between them in a very similar environment.

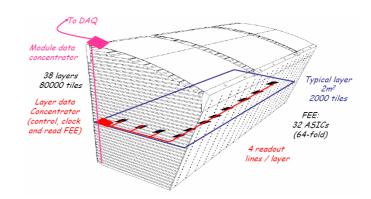

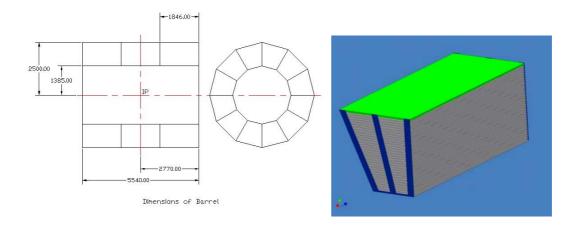

In a similar way, the scintillator HCAL technical prototype will also represent a fraction of 1/32 of the barrel HCAL of a calorimeter close to the LDC design. It would correspond to a half-octant of the half-barrel, with an area of approximately  $1 \times 2m^2$  and a depth of 40 layers, although again, not all will be instrumented. It is scheduled to be complete on the same timescale as the ECAL and the two will be tested together. The gas HCAL technical prototype study started more recently and so is less well-defined at this stage. It is likely to be similar in size to the scintillator HCAL, around 1/36 of a barrel HCAL detector.

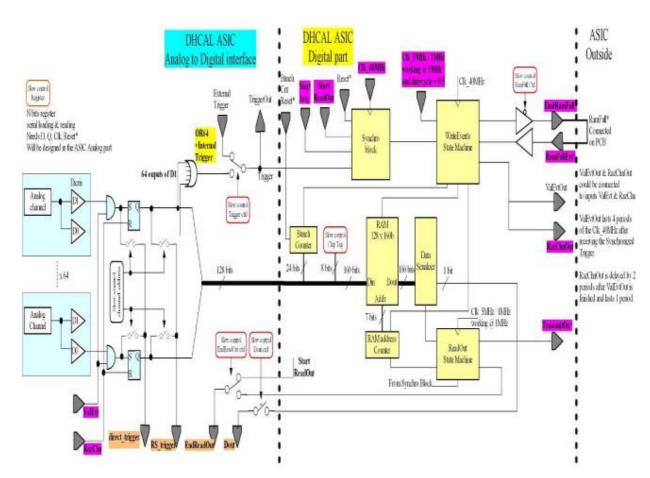

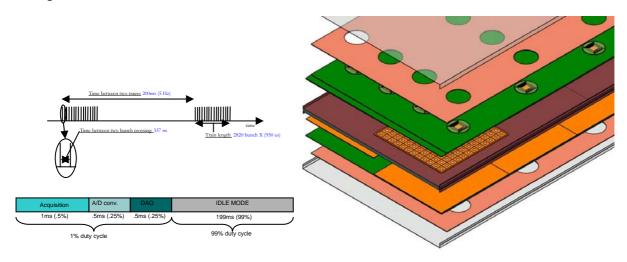

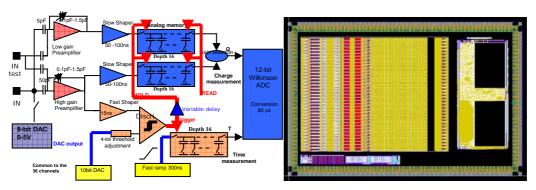

The on-detector readout for the technical prototypes will use second-generation ASICs. These will be different for the various detectors but will be designed with a common basis, such that they will have a very similar back-end and DAQ interface. This means they will share significant parts of the control and readout designs, with obvious benefits in terms of debugging, upstream interfaces and reduced design effort. They will be able to operate within an ILC-like timing structure and will not require an external trigger. They will also buffer data with no deadtime during an ILC-like beam spill and then read out between spills. Furthermore, the ASICs will be embedded on the detectors and will have the ability to be powered down to reduce the heat load before the next spill. As such, they will incorporate effectively all the features which would be needed for an eventual ILC readout chip. One novel feature of the ASIC used for the HCAL is that it will incorporate a TDC which will allow O(ns) timing of hits, to allow for non-prompt neutron identification.

The off-detector control, timing and readout will be with a prototype DAQ system which would in principle be capable of operating at the ILC. It will be common to all detectors, with the system-dependent differences restricted to a well-defined interface to each. The system will be triggerless, as expected with most DAQ concepts at the ILC. It will also be based on the concept of no off-detector custom electronics, with only commercial components being used; in particular, there will be none of the traditional crates used in previous HEP experiments. This will give invaluable experience in the real applications of these DAQ ideas.

## 3 The ECAL based on scintillator

#### 3.1 Introduction

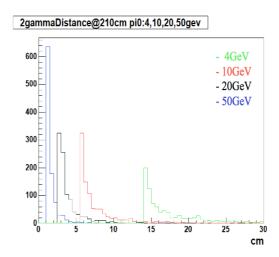

At ILC, the most important role of the Electro-magnetic Calorimeter (ECAL) is to identify photons in jets, since final states are dominated by jets coming from quarks and gluons produced in the decays of electroweak bosons and Higgs particles. Most photons are produced by the two-photon decay of neutral pions in the jets. The opening angle of two photons from the neutral pion decay becomes smaller and smaller with increasing pion energy, as shown in Figure 3-1.

Figure 3-1: Distance distribution between two photons from neutral pion decays at the ECAL sitting 210 cm from the IP.

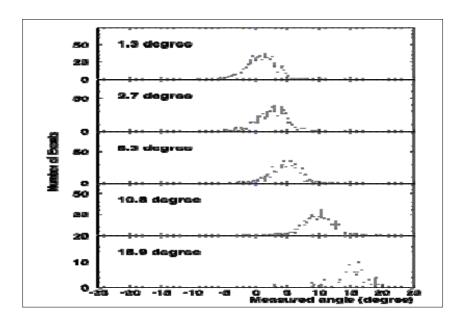

An ECAL granularity of around 1cm will allow the resolution of photons from the decay of neutral pions with energies up to around 50 GeV. It will also allow the efficient separation of charged and neutral energy deposits when used in conjunction with the tracking detector, an essential feature for Particle Flow Algorithms. To achieve such a highly segmented ECAL, we adopted scintillator as active material. The scintillator is a robust, stable, easy to assemble, and reliable material of which we have extensive experience. A sandwich structure is indispensable to measure the EM shower shape in the longitudinal direction. To reduce the Molière radius of the EM shower, we chose to use Tungsten absorber. In order to read out the scintillation light from the scintillator, we employ a wavelength shifting fibre to make the detector more homogeneous along the fibber direction. Our previous ECAL prototype with 1 cm x 20 cm strips showed fairly uniform response to minimum ionizing particles (MIP) [NIM A 557 (2006) 460-478]. One of the results of angle resolution is shown in Figure 3-2.

This long strip scintillator detector also showed good tracking performance in a single particle environment. The scintillation photons must be converted to an analogue signal. This photon detector must have a very small size, and must operate in a strong magnetic field. We have been developing a Multipixel APD to satisfy these requirements. These detectors have greatly improved photon counting capability with respect to previously available devices, and will be useful in many different light detection applications.

Figure 3-2: The angle resolution of long strip ECAL prototype.

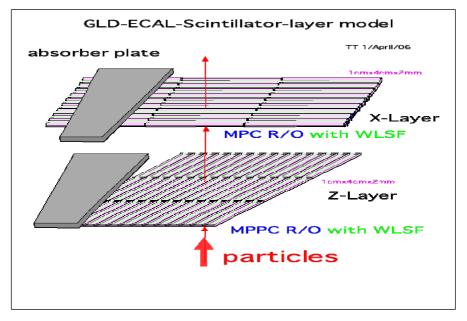

## 3.2 <u>Detector configuration</u>

The ILC-ECAL consists of 1 cm x 4 cm x 0.2 cm strips, aligned orthogonally in adjacent layers. This reduces the number of readout channels with respect to a granularity of 1 cm x 1 cm, while keeping the same effective granularity. The mean Moliere radius of this ECAL detector is 29 mm which means that about 5 strips in each layer will receive electrons in a typical E-M shower. The thickness of the Tungsten absorber material is 3 mm at 90 degrees to the beam direction, as shown in Figure 3-3. At the end of every strip, a photon sensor is attached to receive the scintillation light via the WLS fiber.

Figure 3-3: Scintillator ECAL model of orthogonal oriented short strips with tungsten absorbers.

## 3.3 Development items

#### 3.3.1 Photon sensor (MPPC)

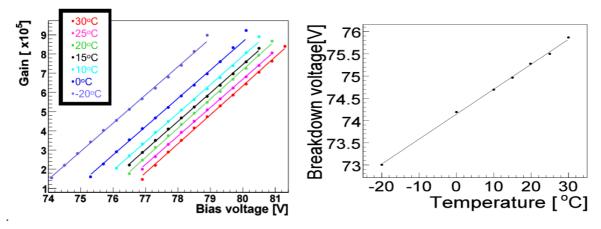

The new photon sensor is named "MPPC" (Multi Pixel Photon Counter), which we are developing together with the Hamamatsu Photonics Company. It is a silicon photon sensor, designed to operate at room temperature. The size of the photon detection area is 1mm x 1mm, which contains 40 x 40 small pixels of 25 x 25 microns, giving a total of 1600 pixels, which are connected in parallel. Each pixel operates in the limited Geiger Mode region, giving an ON/OFF signal of with a gain of about 3 x 10<sup>5</sup>, depending on the bias voltage. The number of photons in the detector is proportional to the pulse height of the output signal for low light input. The basic understanding of this sensor and various improvements are in progress. A current MPPC which has dimensions of 3 mm x 4 mm x 1.3 mm, currently the smallest plastic package of the Hamamatsu product. In Figure 3-4, we show the response of a typical MPPC as a function of the applied bias voltage.

Figure 3-4 Left: The MPPC amplification gain is plotted as a function of the bias voltage at various temperatures. Right: The MPPC breakdown voltage as a function of the temperature, which is extracted from the left figure.

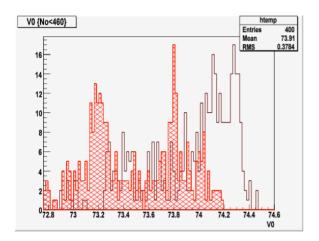

This sample of MPPCs has very uniform characteristics, as can be seen in Figure 3-5 (left), where we show the relation between the gain and the over-voltage (defined as applied bias voltage - breakdown voltage) for a large sample of MPPCs. In this figure, there are two colours which correspond to the two different delivery times.

Figure 3-5 Left: The variation of breakdown voltage with temperature is 56mV/degree for this particular MPPC. Right: The distribution of Vb for 809 MPPCs.

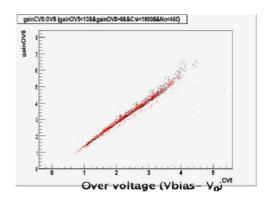

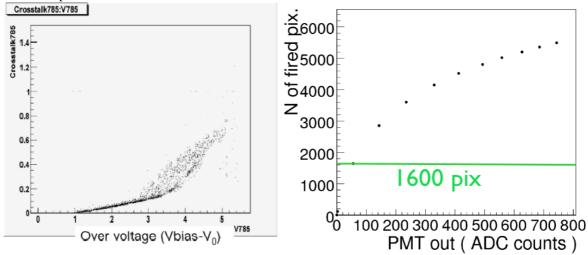

Once a pixel in a photon sensor has fired, there is a possibility to have signal at the neighbouring pixel. It is called as cross talk. Even in the darkness, the MPPC may have signals, although the signal is equivalent with a single pixel firing. If two or more bigger signals are seen, they must be due to the cross talk. The cross-talk probability distribution for 468 MPPCs is shown in Figure 3-6, which shows fairly uniform behaviour as a function of the over voltage. This cross-talk probability is expected to be reduced by future sensor improvements.

Figure 3-6: Left: The cross talk probability distribution for 463 MPPCs as a function of the overvoltage. Right: MPPC linearity measured by LED system as a function of input light measured by a photo-multiplier.

In Figure 3-6, we have unexpectedly good linearity than the number of pixels which is 1600 in this particular MPPC. This measurement has been carried out with a 100 ns gated ADC, which leads an idea of rapid recovery of pixels in the photon sensor. To ensure the linearity of the ECAL system, we need to increase the number of pixels in a MPPC. Further sensor development is required to increase the number of pixels.

#### 3.3.2 Scintillator and its fabrication

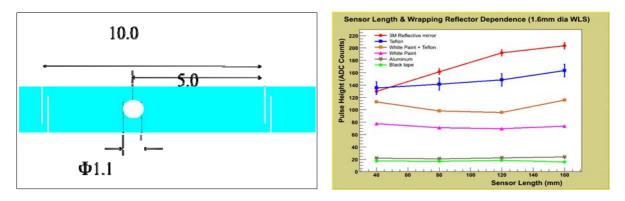

We are studying the ECAL using scintillator from different scintillator producers. One is commercially available from the Kuraray company which makes a casting scintillator plate. We have machined this scintillator plate to produce the mega-strip structure whose cross section is shown in Figure 3-7 where one can find a hole for the fiber and grooves to prevent light leak to the neighboring strips.

Figure 3-7 Left: Cross section of mega-strip scintillator. Right: The light amount received with different reflector materials.

The other scintillator is developed by Kyungpook University. It is manufactured using an extrusion method, which allows an outer light shield of TiO2 and the central hole (for the WLS) to be incorporated directly into the long scintillator strips. They are also trying to produce a mega-strip using an extrusion method.

#### 3.3.3 Reflector

We have studied how the detected light depends on what material is used to cover the scintillator; the results are shown in Figure 3-7. The 3M radiant mirror film [http://www.3m.com/] is seen to give the largest signals. At present this is not commercially available, but the company says it will soon produce a similar reflector.

## 3.3.4 Wavelength shifting fiber

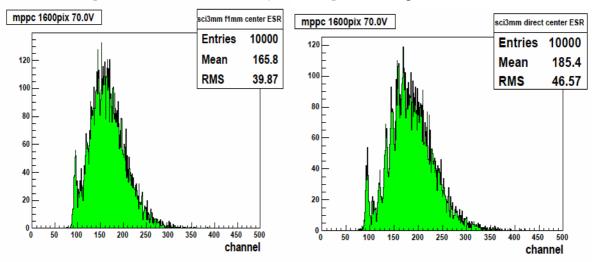

We have been studying the light collection from the scintillator. In order to reduce the non-uniform response of the scintillator, we set a light collection fiber in a straight hole at the center of the scintillator. This fibre contains Y11 wavelength shifter, and absorbs scintillation light (which has a wavelength of about 400 nm) and emits it at a wavelength of 550 nm. Although this emission wavelength is a little longer than the most efficient wavelength for the MPPC, we have measured a signal of 23 photo electrons (p.e.) from a 1 cm x 4.5cm x 0.3cm scintillator strip with a WLSF using a MPPC for a minimum ionizing particle (MIP). The number of photon electron distribution by a MIP is plotted in Figure 3-8.

Figure 3-8 Left: The energy deposit distribution by a mip with a wave length shifting fibre read out. Right: The energy deposit distribution by a mip without a wave length shifting fibre via direct read out.

The peak efficiency of the MPPC is at a wavelength of around 400nm, so we tried to directly attach the MPPC to the scintillator, without a WLSF. While reducing the number of photo electrons to a half of that with the WLSF, it shows a narrow distribution of the number of detected photons. This approach makes the detector construction easier, since we do not need to carefully align the MPPC to a WLSF.

#### 3.4 The prototype detector and its performance

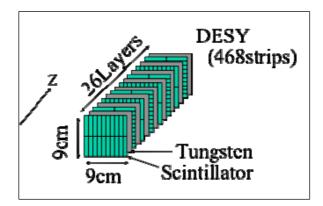

A prototype ECAL detector was constructed at Shinshu University and tested at the positron beam line at DESY.It consists of 26 layers of scintillator, each with 18 scintillator strips, interleaved with 3.5mm thick super-hard Tungsten plate. The strips are aligned in orthogonal directions in successive layers, as shown in Figure 3-9.

At each end of each scintillator strip, we made a small rectangular hole (4 mm x 1.3mm) to hold the MPPC. We have constructed three types of detector, each with 13 layers: Kuraray scintillator with and without the WLSF, and one of the extruded Korean scintillator. We prepared three types of ECAL combining these

three detector types. The MPPC signals are read out by the electronics system of the AHCAL (Analog Hadron calorimeter of scintillator tile with SiPM read out).

Figure 3-9: A schematic view of scintillator ECAL prepared for the DESY beam test.

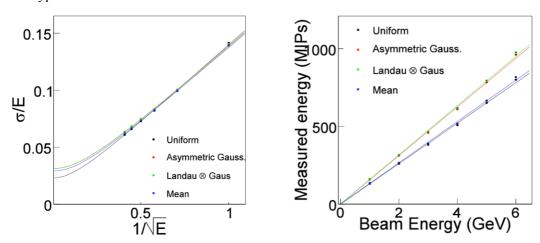

## 3.5 Beam test at DESY

The detector performance was tested at the DESY synchrotron. Positrons with energies energies of between 1 and 6 GeV were injected onto the ECAL at various points. The detector was calibrated by removing the tungsten plates, and firing positrons at the centre of each scintillator strip position. The breakdown voltage of each MPPC was measured at the laboratory prior to the beam test. The bias voltages of the photon sensors were set 2.5 V higher than the breakdown voltage in the case of the strips with WLSF, and 3.5 V higher for the the other detectors.

Some preliminary results of the beamtest are presented here. The basic performance of this ECAL is shown in Figure 3-10, where we show the linearity and energy resolution when using various calibration methods which we are presently investigating. The homogeneity of a strip along its length is shown in Figure 3-11 for the three types of scintillator.

Figure 3-10 Left: The energy resolution of the prototype scintillator ECAL detector tested at DESY beam with different calibrations. Right: The linearity of the ECAL with different calibration methods.

Figure 3-11: Homogeneity of a scintillator strips. Left: Kuraray scintillator with a WLSF. Middle: Kuraray without WLSF. Right: KNU scintillator.

## 3.6 Future plans and milestones

The prototype ECAL detector of 468 MPPCs has been successfully constructed and tested. Its performance has been measured and shows reasonable characteristics. Moreover, we are planning to build a larger detector, 4 times bigger than the current prototype. Using the next prototype, we will test neutral pion reconstruction at the pion beam line at Fermilab, where we will place a target in front of the ECAL module. The pi- + neutron -> pizero + proton charge exchange process pizero producing process will be employed to identify neutral pions using this ECAL module in 2008.

We will further improve the scintillator and the photon sensor. The MPPC photon sensor should have a smaller cross talk rate; we will work on this together with the Hammamatsu Photonics. The Korean scintillator will consist of extruded mega-strips with an embedded WLS fiber. This new production procedure is simpler and should improve the response uniformity.

## 3.7 Remaining issues

We have not yet verified the possibility of neutral pion reconstruction using a detector simulation, although we plan to test this using real pi-zero data at Fermilab in 2008. Only one third of hadrons interact in the ECAL, so we will need to use a HCAL system to fully measure hadron and eventually jet energies. The best combination of ECAL/HCAL detectors is not yet known.

## 4 The ECAL based on silicon

#### 4.1 Introduction

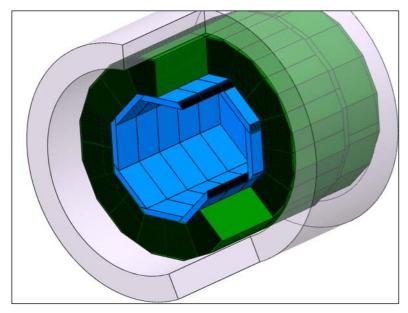

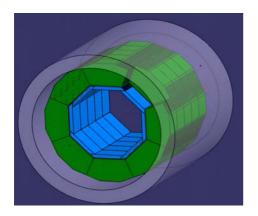

At the future e+e- linear collider, the detector must be able to perform a very efficient particle flow reconstruction. One of the ways to perform it consists in instrumenting calorimeters with a high degree of tracking capabilities, making possible a reliable track-shower association (TCA) and energy estimation. To optimize the TCA and the energy resolution, both the electromagnetic (ECAL) and hadronic (HCAL) calorimeters must be put inside the coil. Figure 4-1 shows the general geometry of the calorimeter system, which avoids any blind region in the middle of the shower development.

Figure 4-1: General view of the calorimeter system internal to the coil. The thin ECAL is represented in blue.

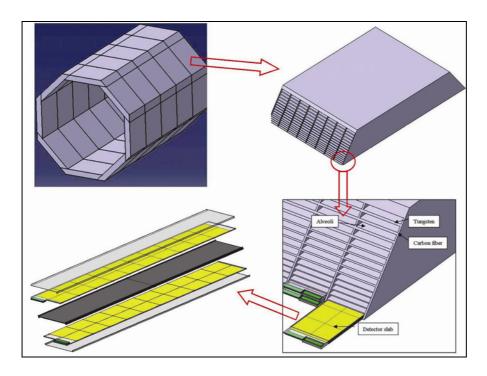

Therefore, the available space for both calorimeters is constrained by the internal radius of the coil and a compact ECAL is mandatory for shower separation giving in addition enough space for a large number interaction lengths in the HCAL. In addition, it has been shown that a "tracking calorimeter" could be the right choice to optimize the performance of the pattern recognition, since it produces a 3D view of the shower development inside the calorimeter. Such a calorimeter must have a large segmentation with small readout pad size and a good shower to shower separation, i.e. a small Molière radius but also a small hadronic shower spatial dispersion. Basic construction units of the electromagnetic calorimeter are modules, mechanical stiffness of which is ensured by a carbon fiber skeleton, minimizing dead region. A detailed version of the proposed ECAL geometry is shown in Figure 4-2.

Figure 4-2: Cross section of the barrel part of the detection system (top left) and basic construction elements of the electromagnetic calorimeter, with at the end (bottom left) the basic detector element, called detector slab.

## 4.2 The electromagnetic calorimeter concept

All these considerations led to choose high Z number and density material for the radiator going naturally for the tungsten, which has a Molière radius  $r_M$  of 9mm and a radiation length ( $X_0$ ) of 3.5 mm. For the active part of the device, silicon PIN diodes seem perfect apart from their cost. The individual e.m. energy resolution needed and the future cost evolution will drive the area of silicon and therefore the number of layers. Many studies have been performed with 40 layers, as given in the TESLA TDR [1], while a prototype under construction will have only 30 layers. The pad size comes from a compromise between

- 1. the density of extraction lines of the readout,

- 2. the electronics cost with the total number of channels,

- 3. the effective Molière radius of the calorimeter.

A pad size of 1x1cm<sup>2</sup> has been adopted for the first studies and first prototype, but the second generation prototype as well as the recent studies use 5x5 mm<sup>2</sup>.

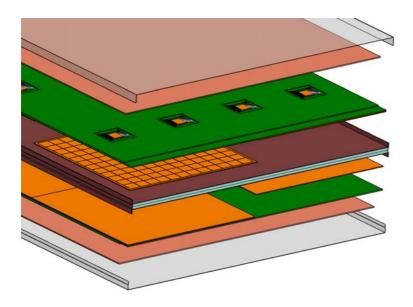

The basic detection units are detector slabs (Figure 3.2) which consist of a stiffening H-structure from carbon fiber material embedding a tungsten sheet overlaid by silicon pad sensors. The entire slab is shielded by an aluminum envelope and is slit into the module. As shown in Figure 4-3, for the final project, the only possible geometry design locates the VFE chip inside the detector. That will be possible only if

- 1. the power dissipation is low enough,

- 2. the duty cycle reduce sufficiently the power dissipation. If not, a cooling system has to be designed in this thin device.

- 3. A 500 GeV electromagnetic shower crossing the VFE chip does not disturb it too strongly.

All these points are part of the CALICE R&D program. Ensuring the behavior of the first ECAL prototype in the test beam, for the prototype, the VFE chips are located outside, on the external part of the PCB.

Figure 4-3: Schematic view of a possible detector slab. Green is the PCB in which the VFE are included, the silicon matrices (orange) are glued on PCB. The tungsten sheet (light blue) is wrapped in carbon fibre (brown). An overall protection sheet in aluminium (grey) surrounds everything.

## 4.3 Current status of the project

The agenda of the project concerns also the construction of a second generation of prototype, this time as close as possible to the final detector. This second generation is partially funded by the EU program EUDET. The test with hadron beams is foreseen to be done together with the different HCAL options of CALICE.

Figure 4-4 Left: Schematic view of the first generation prototype. Right: ECAL prototype at CERN test beam area in 2006.

## 4.4 The prototype in test beam

#### 4.4.1 General description

The ECAL prototype mimics the final project with tungsten wrapped in carbon fiber, with 30 layers and a pad size of 1x1cm<sup>2</sup> but the very front end (VFE) electronics is located outside the device, on the same PCB on which the silicon wafers are glued. The schematic view of the prototype is shown in Figure 4-4, with different shade of grey for the three stacks, each one with different tungsten thickness. This choice

ensures a good resolution at low energy, due to the thin tungsten in the first stack, and a good containment of the e.m. shower due to a tungsten thickness 3 times larger in the third stack. The overall thickness is about 20 cm or  $24X_0$ . The structure is realized by carbon fiber wrapping half of the tungsten sheet, leaving free slots between each tungsten sheet, called alveoli. In these free slots, detector slabs are slit. The detector slab consists of 2 active readout layers surrounding one tungsten sheet. The active layer is made of PCB 14 layers (2.1mm) and 500 microns high resistivity silicon wafers.

#### 4.4.2 The active device

The wafers are cut in matrices of 62x62 mm with 36 pads, while the space reserved for the guard ring is about 1mm. It must be noted that there is only one set of guard ring per matrix. The production, made in Russia, managed by the MSU group, and in Czech Republic, managed by the IOP- ASCR, is of very high quality, with a typical leakage current less than a few nA/pad for all the pads, apart from a few per cent of the production, where 1 or 2 pads among the 36 of a matrix go up to 20 nA/pad. The matrix will work in overdepleted mode around 250V bias voltage. The prototype is still under completion with silicon ratio about 50% from Russia and 50% from Prague. This prototype will be completed in June 2006.

The connection to the PCB is realized by conductive glue for each pad, with an AC coupling mode of the readout. For the final project, it is considered to use amorphous silicon deposited directly on the pad, to provide the resistance and capacitance. This is the object of an R&D program inside the CALICE-ECAL groups. For the prototype, the AC coupling is realized using discrete components put directly on the PCB, before the amplification in the VFE chip.

#### 4.4.3 The very front end electronics

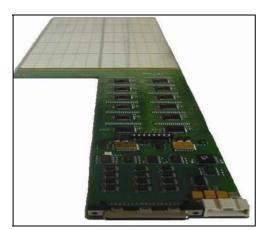

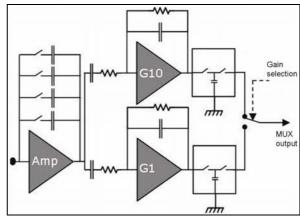

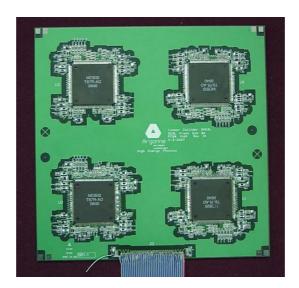

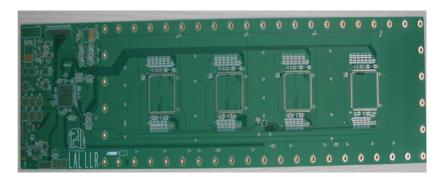

The PIN diodes are read by a VFE chip developed by the LAL-Orsay group. It consists of a preamplifier, a shaper with two possible gains and a multiplexer. This chip treats 18 channels, with low noise and high dynamic range. It provides a linearity of 0.2%, a signal uniformity better than 2% and less than 0.2% of cross talk. These values are measured over the 600 MIPS dynamical range. The PCB with the silicon matrix and the VFE on the side are shown on Figure 4-5. The schematic view of the VFE is also presented in Figure 4-5.

Figure 4-5 Left: PCB equipped with silicon matrices. Right: VFE schematic used for the prototype and VFE chip.

#### 4.4.4 Assembly

The wafers are glued on the PCB by an automat controlled by a PC. The glue is a conductive glue from Epotek. Four years after the assembling, no problem is observed. The process has been studied to be useable down to a pad size of  $5x5 \text{ mm}^2$ .

#### 4.4.5 First test of the device

One of the important advantages of the silicon is the response stability with time and temperature. In order to check that, the detector is intercalibrated with dedicated muon runs, by fitting the m.i.p. peak. This intercalibration is then used for all the year run period. After run analysis leads to observe, after 2 years of running, (DESY 2005 and CERN 2006) a number of dead cells of the order few per mill. The signal over noise observed as the mip peak to the standard deviation of the noise is about 8, with some dispersion from PCB to PCB, but also wafer to wafer. Most of the problems of common noise are related to the connexion at the PCB end toward the CALICE readout card (CRC) VME readout card.

Analysing the runs taken at CERN with electrons from 10 to 50 GeV/c, the detector shows a very good behaviour, and the overall performance seems well described by Geant4 simulation. It must be noted however some problems under investigation which have to be solved for the future.

- 1) The readout electronics shows some common mode on the pedestal, during the data taking

- 2) A very strong signal on one pixel, induced a common pedestal shift in the same wafer

- 3) The floating guard ring induced a cross talk at long distance between pads.

- 4) A loss of about 20% of signal in the guard ring region, even with a staggering of 1.2 mm layer to layer. These problems should be cleared off for the second generation prototype already under design.

## 4.5 The second generation prototype

A second generation of prototype, as close as possible to the final detector is under design now. The goal is to have this prototype in test beam in 2009.

#### 4.5.1 The new wafers

The silicon wafers will have a new design of the guard ring and a pixel size of 5x5 mm<sup>2</sup> and depending of the cost, wafers of 6" would be used, which reduces the ratio of the guard ring region over the pixel active region. Quality test of delivery are under development in LLR and Clermont LPC, able to deal with the new geometry. The wafers them self are under design studies at Prague, IOP-ASCR.

#### 4.5.2 The new VFE chip

On the readout side, a new VFE ASIC will be directly mounted on the PCB, without packaging, and ion the opposite side of the silicon matrix. This new ASIC will include the ADC and the storage of the digital signal during the spill (similar but longer to the one during the bunch train). It will also have a good linearity up to 3000 mips, which is needed by the final project.

#### 4.5.3 The new PCBs

One group of the collaboration is performing longer term stability studies of the gluing process. The assembling process could be, a priori, easily transfered to industry for the final project, through the use of stichable PCB assembled before to build the detector slab made of two layers above and below a tungsten sheet, the overall wrapped in carbon fiber. In order to minimize the loss in the case of something goes wrong during the gluing and assembling processes, the unit size of PCB will just be about  $20x20\ cm$ . Since the VFE ASIC being very close to the active silicon wafer, the number of layer in the PCB can be reduced, and the PCB thickness could go down to about  $800\ \mu m$ .

#### 4.5.4 The new mechanics

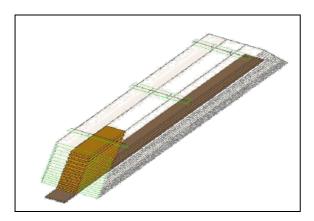

The new module will be as close as possible to the module for the final detector. The new prototype is therefore expected to be a kind of module "zero" for the final detector. For a question of cost, this prototype will have the full length of a barrel module but only half of the width, 3 instead of 7 alveoli. We therefore will have this time a prototype 1.6 m long, about 54cm wide and about 18cm thick. The number of layers is 30, with only two stacks for what concerns the tungsten thickness (optimising the energy resolution

at low and medium energy). The alveoli will be 18 cm wide, which optimises the use of 4" as well as 6" wafers. Figure 4-6 shows a schematic view of this new module prototype.

Figure 4-6: Schematic view of the new ECAL prototype, with silicon coverage over a slab of full length and a region of full depth

## 4.6 Schedule of the beam test

The tests of the ECAL prototype foreseen in 2007 at CERN period are the following:

- ➤ Detector completed mid of 2007, test of hadron shower with full prototype

- > Test of the optimised layers staggering, impact on energy resolution

- > Test of the ASIC VFE in high energy em shower

In the year 2008, the EUDET prototype will be designed and finalized before a construction which must lead to having this new prototype in test beam before the end of 2009.

## 4.7 Alternative option for the silicon active device : MAPS

The studies of silicon-tungsten ECALs include work on a digital ECAL where the cells have binary read out. Since such threshold readout does not retain information on the number of particles passing through the cell, then to avoid a non-linear response, the probability of more than one particle hitting the cell should be low. The high density of particles in an EM shower therefore requires the cells to be very small. A typical shower density for the highest energy EM showers expected at the ILC is  $100 \text{ MIPs/mm}^2$  which corresponds to an average of 1 MIP in a  $100 \times 100 \mu\text{m}^2$  area. Hence, cell sizes of this order or lower are required. This implies an extremely large number of cells for an ECAL and hence requires a very high level of readout integration.

The digital ECAL design being studied within CALICE is implemented using a Monolithic Active Pixel Sensor (MAPS) which integrates the sensor and the readout into the same silicon wafer.

MAPS can be implemented using a standard CMOS process, available at many foundries around the world, and so is more readily available than the high resistivity silicon process needed for the diode pads wafers. This should allow any large-scale production to be sourced from multiple vendors and so is likely to be significantly cheaper per unit area than a diode pad wafer production.

MAPS are sensitive to charged particles through charge liberation in an epitaxial layer under the electronics circuit layer. This charge diffuses in the epitaxial layer and is subsequently absorbed by n-well structures in the circuit layer. N-well collection diodes are used to absorb this charge and serve as the inputs to charge-sensitive circuitry on the sensor. The charge-sensitive circuit then discriminates the level of charge collected and the output is stored on-sensor. However, unless the circuit design can be restricted to otherwise only use p-well diodes, then the circuit n-well diodes will also absorb charge, leading to a significant loss of signal.

To overcome this problem, a novel "INMAPS" process has been developed which isolates the circuit n-well diodes from the epitaxial layer using a "deep p-well" layer between the two.

## 4.7.1 Project status

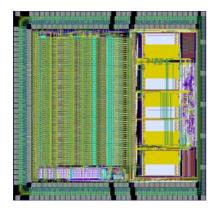

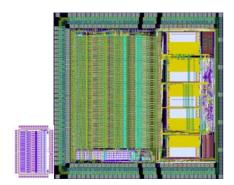

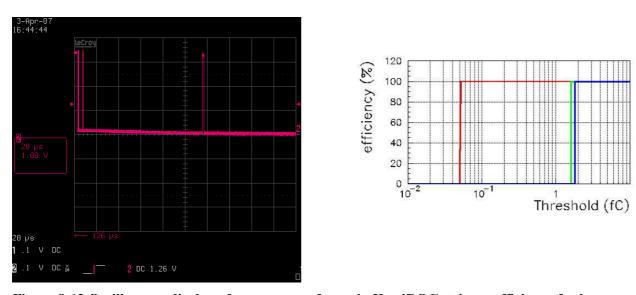

A first design of such a MAPS device has been completed and was submitted for fabrication using the INMAPS process in April 2007. It will be available in July for testing before a second sensor is fabricated in 2008. This first design is intended as a proof-of-principle and would not be suitable for use at the ILC. The sensor has an epitaxial layer thickness of 15µm and a pixel size of 50×50µm². The sensor will be  $10\times10\text{mm}^2$  in size and will contain a  $168\times168$  array of sensitive pixels, corresponding to approximately 28k pixels total. Four different versions of the pixel electronics have been implemented within each sensor to allow studies for further optimisation in the second fabrication round. The individual pixels operate asynchronously as distributing a clock across the whole sensor surface would have taken a significant amount of power. The discriminated output of each pixel is stretched to the bunch crossing period and tracked to a centralised memory bank column where pixels above threshold are timestamped with the bunch crossing number. The list of pixel locations and timestamps is available for readout following the bunch train. In the first sensor, the memory banks occupy the equivalent width of 5 pixels and occur every 47 pixels (approximately 2mm). Since they are not sensitive, this is a dead area and so contributes to the sensor inefficiency. Figure 4-7 shows the submitted design schematic diagrams for the whole sensor and one of the pixels.

Figure 4-7 Left: Schematic of complete MAPS sensor submitted for fabrication. The logic and memory storage areas are clearly visible as the four vertical stripes. Right: Schematic of a pixel layout. The electronics associated with a single pixel is highlighted in colour. The pixel boundary is shown by the dashed line.

A detailed sensor-level simulation of charge diffusion in a MAPS pixel and its immediate eight neighbours has been done using CENTAURUS, with the design GDS file being used to define the pixel geometry. This ensures the simulation is identical in structure to the real pixel. This has allowed optimisation of the sensor during the design as well as making predictions of the sensor performance. As an example, Figure 4-8 shows a simulation of the charge collected by the pixel for three collection diode sizes as a function of the distance of the particle position within the pixel, specifically along a diagonal near the pixel corner. (The corner is the most difficult region as, by symmetry, the average charge collected in each pixel around the corner is at most ¼ of the total liberated.) The 1.8µm diode size is seen to give the highest signal/noise (S/N) and this was the size chosen for the first sensor. Even for the case or a particle right at the corner, the S/N for a MIP deposit is predicted to be above 10 for all diodes. This will allow a threshold around half the MIP value, giving good noise rejection and high efficiency for the pixel discriminator. The target rate for noise hits is  $10^{-6}$  per pixel per bunch crossing. Note, even at this low rate, there would be  $10^6$  pixel hits per event throughout the whole ECAL.

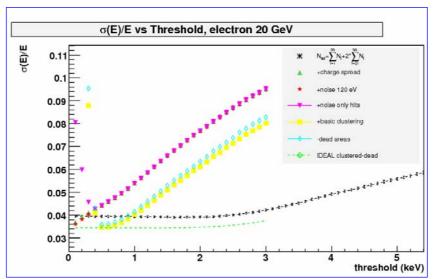

Figure 4-8: Simulated MAPS pixel signal/noise ratio for MIP deposits for three collection diode sizes as a function of the position of the deposited charge from the corner. The x axis values correspond to increasing distance from the corner of the pixel, with x=1 being at the corner and x=10 being the centre of the pixel. The diode sizes are  $0.9\mu m$  (green),  $1.8\mu m$  (blue) and  $3.6\mu m$  (red).

## 4.7.2 ECAL performance

The performance of a MAPS digital ECAL has been studied using the Mokka simulation followed by a digitisation step. The latter models the charge diffusion, noise and pixel discriminator output and so gives a list of pixels above threshold for each event, equivalent to the information which would be available in a real calorimeter. Following digitisation, a clustering step is performed to attempt to group neighbouring pixel hits which resulted from a single particle in the sensor. The resulting resolution of EM showers has been studied using this simulation. The effects on this resolution of various contributions are shown in Figure 4-9 as a function of the threshold used.

Figure 4-9: For the given sampling fraction used in the simulation, the ECAL resolution obtained from the MAPS with the sensor effects included is seen to be equivalent to that obtained from an ideal digital calorimeter and is around that obtained with the diode pads ECAL.

PFA studies using a MAPS digital ECAL are ongoing. The much finer granularity resulting from MAPS may allow a significant improvement in two shower separation, particularly in the front part of the ECAL before the shower has spread to the Molière radius. These studies are currently at a very preliminary stage and no quantitative results are available yet.

It is assumed that the response of particles to the MAPS silicon will be identical to that of the diode pads wafer silicon and so a physics prototype for data-simulation comparison studies is not required. However, as it is a novel design, it will be important to acquire operational experience of a MAPS calorimeter. The second fabrication round in 2008 will produce larger sensors of size  $20 \times 20 \text{mm}^2$  (limited by the size of a standard CMOS reticule without using stitching) in a dedicated run. Assuming a reasonable yield, this will give a sufficient number of sensors to produce PCBs for one (or possibly two) layers of the ECAL silicontungsten technical prototype. This could be swapped into the prototype to replace a diode pad layer at various depths into the structure during the technical prototype beam tests. This will allow a direct comparison of the response of the two types of ECAL at various positions in the shower depth and so allow a meaningful comparison of the performance of the two concepts. The MAPS PCB readout will use the same DAQ system as for the diode pads. Hence, the technical prototype and DAQ for the silicon-tungsten ECAL will be shared between the two designs.

#### 4.8 References

- 1. Calorimeter section, in Tesla Technical Design Report, DESY Report 2001-011, March 2001

- 2. A calorimeter for Energy Flow, J.C. BRIENT at LCWS2000, SITGES <a href="http://www.thep.lu.se/~torbjorn/Pythia.html">http://www.thep.lu.se/~torbjorn/Pythia.html</a>

- 3. CALICE collaboration, http://polywww.in2p3.fr/flc/calice.html

## 5 The Tile HCAL

#### 5.1 Introduction

In the particle flow paradigm, the HCAL must be an imaging detector: it must allow separating the energy depositions assigned to charged particles from those generated by neutral hadrons and thus eliminating the dominant part of hadronic jet energy fluctuations which is attributed to the charged hadrons. It must then measure the energy of neutral hadrons (mostly neutrons and kaons) and that of not resolved charged hadrons with very good precision. To optimise the particle flow measurement the HCAL should contain the hadronic showers, have a sufficiently high granularity both in the transverse and in the longitudinal direction to resolve the shower substructure, and provide very good hadronic energy resolution. In addition it would be desirable to measure the time of events precisely, to search e.g. for exotic signatures with long lived particles as they are predicted in some SUSY theories, or to help in the rejection of cosmic rays. It has also been suggested to use timing information in the shower reconstruction.

#### 5.1.1 The scintillator HCAL concept

With the advent of multi-pixel Geiger mode photo diodes - so-called SiPMs - the high segmentation required for PFLOW reconstruction can be realized with scintillators at reasonable cost. SiPMs have only recently become available in larger quantities from Russian and Japanese industry. With typically 1000 independently quenched pixels on a common load they provide a signal proportional to the number of pixels fired by impinging photons and a gain comparable to that of vacuum photo-tubes. The technology is investigated by several electronics companies around the world and is also driven by non-HEP applications, e.g. astrophysics or medical imaging.

The energy response of scintillators allows to trade amplitude resolution versus granularity and thus to optimize the cost of the readout electronics. In addition to the classical analogue readout, semi-digital concepts with few threshold bit information or a purely digital approach are also followed. A scintillator HCAL has thus become a promising candidate for all PFLOW based detector concepts.

The AHCAL is conceived as a sampling calorimeter, with a material of low magnetic permeability ( $\mu$ <1.01) like stainless steel, brass, lead or tungsten as absorbers, and scintillator plates as the active medium. The scintillator plates are subdivided into tiles. The millimeter-size SiPM devices can operate with moderate bias voltage in high magnetic field and are mounted on the tiles. The light is collected either directly from the tile or via embedded wavelength shifting fibres (WLS). This concept is different from existing tile calorimeters with long fibre readout; it allows integrating not only the photo-sensors but also the front end electronics into the detector volume.

## 5.1.2 Sampling structure and segmentation

The basic sampling structure consists of 20mm thick absorber plates interleaved with 6.5 mm deep gaps into which the 5 mm thick scintillator plates are inserted. The sampling structure is the same for barrel and for end cap regions; the total depth is still subject to optimization. In the LDC, for example, 38 layers are foreseen for the barrel 53 layers in the end cap. Each layer corresponds to  $1.15 X_0$ , or  $0.12 \lambda$  at normal incidence. The layers are subdivided into tiles of transverse dimension  $3 \times 3 \text{cm}^2$  which is considerably smaller than the hadronic shower size. Because of the possibility to implant the SiPM devices into the tiles, all longitudinal layers can be read out individually, which has been shown to significantly enhance the performance.

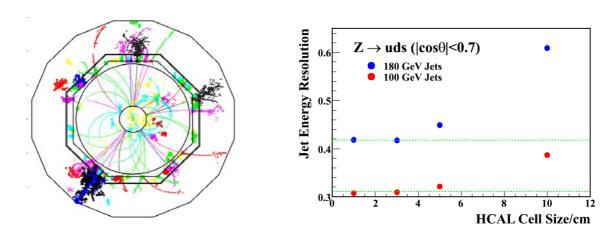

The segmentation has been optimized to allow for the separation of partially overlapping showers by reconstruction of their internal tree-like structure of sub-clusters, and was also found suitable for the semi-digital approach. Recently, in a full detector simulation and reconstruction study using the Pandora PFLOW algorithm, it could be shown that with such a calorimeter, integrated in the LDC detector environment, the performance goals of the ILC (in terms of W and Z dijet mass separation) can be met. Variation of the tile size between 1x1 cm<sup>2</sup> and 10x10 cm<sup>2</sup> has shown little impact on the performance for events at the Z resonance, but revealed that the choice of 3x3 cm<sup>2</sup> is close to optimal for jets at higher (180 GeV) energy, as shown in Figure 5-1. Further studies are needed to fully optimise the transverse cell (tile) sizes, possibly as a function of the depth in the calorimeter. However, this granularity is considered a reasonable starting point

to address integration issues. The studies also indicate that a larger depth of about 50 layers in the barrel would yield better containment and resolution. However, possibilities to estimate leakage from the measured shower shapes and the use of the muon system as tail catcher still need to be evaluated.

Figure 5-1 Left: Simulated multi-jet event in a tile HCAL with 3x3cm<sup>2</sup> cells. Right: Dependence of jet energy resolution on calorimeter cell size for scintillator tile.

#### 5.1.3 Readout and calibration

The scintillator HCAL being an analogue device like the silicon based ECAL, with a channel density about 10 times smaller, we follow an integrated approach to the ECAL and HCAL readout electronics, with many components in common and only the input stage of the analogue front end adapted to the different sensor types. With a scintillator based ECAL the read-out could be even further unified.

Thanks to the high granularity of the HCAL, which leads to of the order of 100 hits for a 10 GeV pion shower, the requirements on the statistical precision of the single cell calibration are rather moderate; 10-20% will be sufficient. However care must be taken to control systematic effects, which coherently may affect many cells, to an accuracy of a few percent, in order to keep the constant term in the energy resolution small. The absolute reference scale for the energy measurement will be set by MIP signals which can be obtained from cosmic rays, beam halo muons or from MIP-like parts within hadronic showers. The time needed to record such events in sufficient quantity is days or weeks. The sensitivity of the SiPM response to temperature and bias voltage fluctuations (typically 5% per 1 K or 100 mV) requires a monitoring system to follow more short-term variations by means of reference signals as provided by PIN stabilized LEDs or radioactive sources. The possibility to measure the SiPM gain directly via the single photo-electron signal separation provides an interesting means to auto-calibrate such variations. The calibration in terms of single photo-electron signals is also needed to apply corrections for the non-linearity of the SiPM response arising from the finite number of pixels.

#### 5.2 R&D programme

The test beam effort plays a key role for the validation of the simulations and the further development of the particle flow algorithms which form the basis for the optimal choice of the HCAL granularity. It will also help to identify the crucial operational aspects and guide the development of the calibration and monitoring systems.

Genuine R&D needs to be performed for the optimization and consolidation of the tile photo-detector system. This must be matched with the development of the electro-mechanical concept of the active layer. At present there is no example of a scintillator calorimeter with integrated photo-sensors and front-end electronics. The R&D of the highly integrated front end components is a very ambitious program in itself, which is expected to largely benefit from the synergies with the ECAL electronics development.

#### 5.2.1 The test beam prototype calorimeter

The goals of the AHCAL test beam prototype are twofold: on the technology side, the aim is to gain large-scale, long-term experience with a SiPM readout detector and to identify the critical operational aspects for further system optimization. On the physics side, the purpose is to collect the large data samples (order of 10<sup>8</sup> events) needed to explore hadron showers with unprecedented granularity, validate hadronic shower simulation models and develop energy weighting and PFLOW reconstruction algorithms. Due to the current large model dependence of predictions for PFLOW-relevant shower properties it is indispensable to base the final detector optimization on real beam data. In that respect the term "prototype" may be misleading: the aim is a "proof of principle". Technical solutions scalable to a full detector design are only partially addressed and will be a subject for future R&D.

#### 5.2.2 Detector structure

The AHCAL prototype is a 38-layer sampling calorimeter made of a plastic-scintillator steel sandwich structure with a lateral dimension of about 1 m<sup>2</sup>. Each layer consists of 1.6 cm thick steel absorber plates and a plane of 0.5 cm thick plastic scintillator tiles housed in a steel cassette with two 2 mm thick walls. The total thickness corresponds to  $4.5\lambda$ . The tile sizes vary from 3x3 cm<sup>2</sup> for 10x10 tiles in the centre of the module, to 6x6 cm<sup>2</sup> in an intermediate region and 12x12 cm<sup>2</sup> in the outer region, to limit the channel count and cost. In the last eight layers, the granularity is decreased to 6x6 cm<sup>2</sup> in the central region.

Each tile is coupled via a wavelength-shifting (WLS) fibre inserted in a groove to a SiPM via an air gap (Figure 5-2). The tile faces are covered with reflector foil; the edged were matted to provide diffuse reflection. Each tile has a 1 mm diameter wavelength-shifting (WLS) fibre inserted into a 2 mm deep groove. The fibre is coupled to a SiPM via an air gap. To increase the light yield, the other firer end is covered with a mirror (3M superradiant foil). The grooves have a quarter-circle shape in the smallest tiles and a full-circle shape in the other tiles. The sides of each tile are matted to provide a diffuse reflection and suppression of optical cross-talk between adjacent tiles, which is then limited to <2%. The tile faces are covered with 3M superradiant foil.

Figure 5-2 Left: Scintillator tile (3x3cm<sup>2</sup>) with SiPM. Right: Scintillator tile layer.

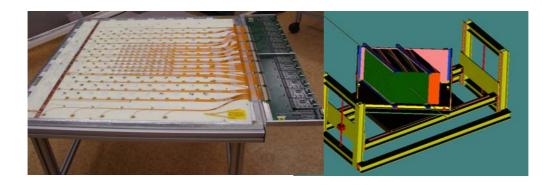

Figure 5-2 shows the tile array laid out in the steel cassette. The size of the active area is 90×90 cm<sup>2</sup>. In the next step of module assembly, the tiles are covered with a plastic (FR4) board which serves as a support for calibration light fibres and for the 1 mm micro-coax readout cables, which are connected to the SiPMs via small flexible PCBs. A fully assembled module with front end electronics connected is shown in Figure 5-3.

Figure 5-3 Left: Complete module with front end electronics. Right: HCAL absorber stack on its movable table

The complete modules are inserted into the absorber stack structure, which is shown mounted on top of a moving stage in the design drawing in Figure 5-3. The drawing shows the configuration set up for inclined beam incidence; the construction ensures that the beam still passes through the high granularity core in all layers for angles up to 35°. The stack and its support have been designed in a modular and flexible way which allows it to be adapted for beam tests with other active modules, for example with resistive plate chambers for tests of the DHCAL. A photograph of the fully assembled set-up is shown in the test beam section of this report.

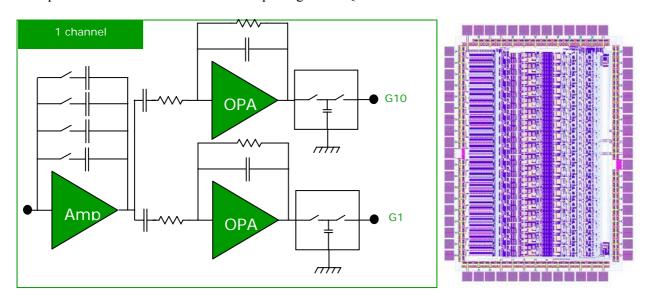

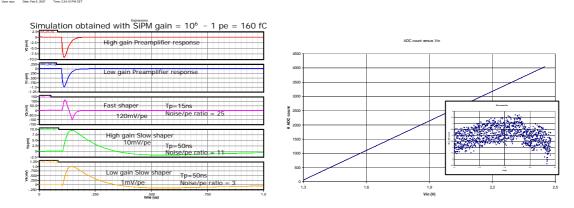

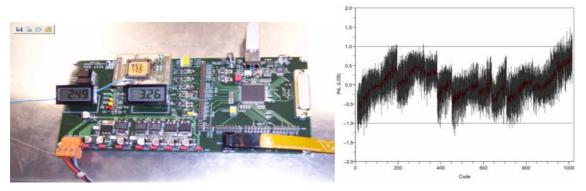

#### 5.2.3 Readout and calibration systems

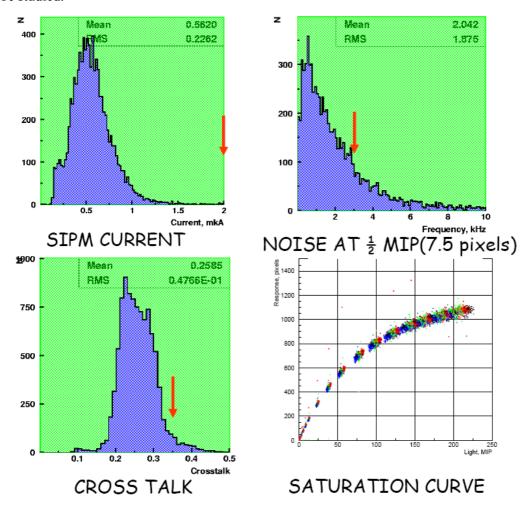

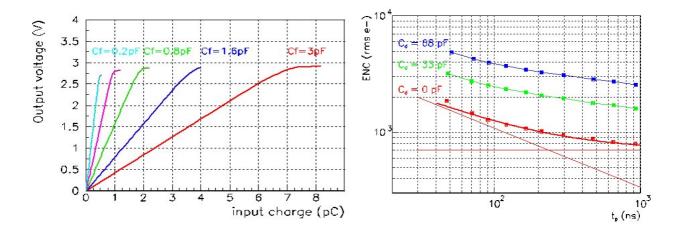

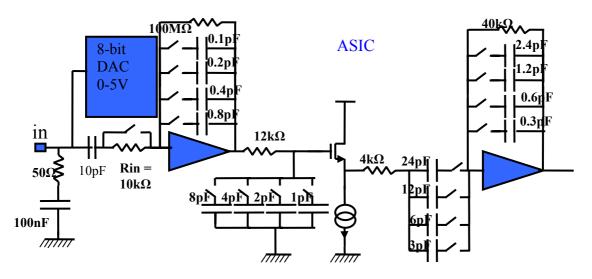

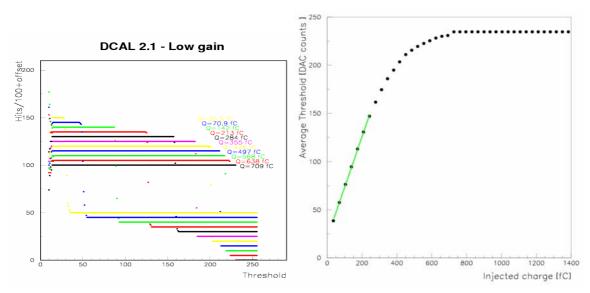

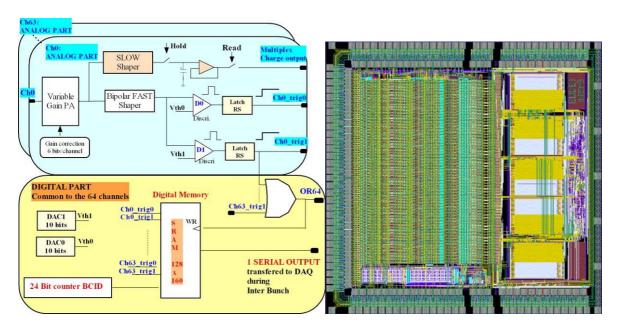

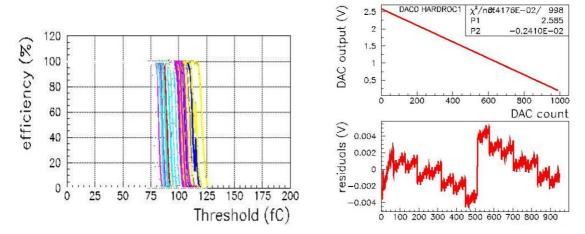

The readout electronics consists of 18 channel front end ASICs, developed at LAL, with preamplifier shaper and sample-and-hold chain mounted on the cassettes, multiplexed and read-out by an off-detector VME based ADC system which was common for ECAL and HCAL. The ASICs provide a high gain operation mode for auto-calibration of the SiPM gain by observation of single photo-electron signals (Figure 5-4), and include DACs for the channel-by-channel adjustment of the SiPM bias voltage. More details on the ASIC are given in the electronics section.

Figure 5-4 Left: SiPM pulse height spectrum with single pixel signals. Right: SiPM response to LED light as function of LED voltage (arbitrary units).

The test beam set-up has strongly benefited from the unified readout electronics concept for electromagnetic (ECAL) and hadronic calorimeter, which reduced the system integration effort to an absolute minimum and resulted in a combined and unified calorimeter system from the very beginning. This experience has lent strong support to the approach for future test environments and the final detector system.

An alternative option, based on fast digitization, is being developed at Dubna; its basic functionality was tested with a small scintillator cassette during the CERN test beam run.

A versatile LED calibration system (electronics developed at Prague) provides light signals up to an equivalent of 200 Minimum Ionizing Particle (MIP) to each tile (Figure 5-4). Low light intensities are used for gain calibration; intermediate intensities provide a PIN diode controlled reference for stability monitoring.

## 5.3 Silicon photo-multipliers

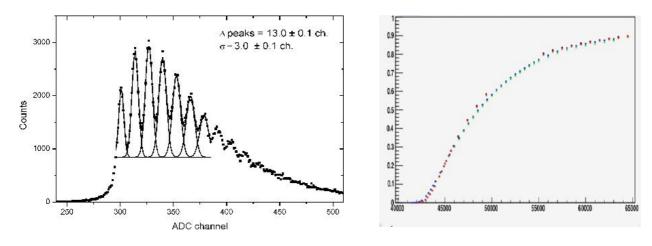

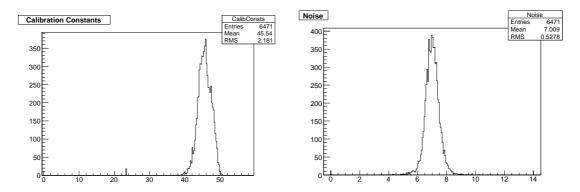

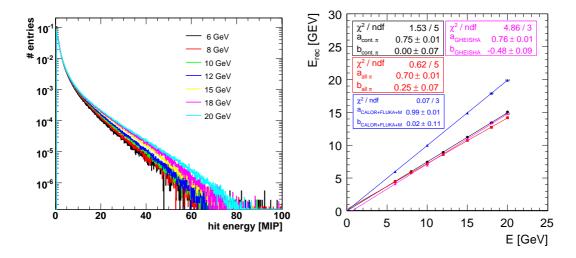

The SiPMs were developed, manufactured and tested in Russia. The photosensitive area (1.1x1 mm<sup>2</sup>) holds 1156 pixels, each with a quenching resistor of a few  $M\Omega$ . The detectors are reversely biased with a voltage of ~50 V and have a gain of ~10<sup>6</sup>. SiPMs are insensitive to magnetic fields; this was tested up to 4 Tesla, For the HCAL prototype, more than 10000 SiPMs have been characterized in an automatic setup, with calibrated LED light. The bias voltage working point was chosen as the one that yields 15 pixels for a MIP-like LED signal. We measure gain, relative efficiency, dark rate, inter-pixel cross-talk, noise above a threshold of ½ MIP and the non-linear response function of fired pixels vs light intensity over the full dynamic range. Some distributions are shown in Figure 5-5.

Radiation hardness tests of SiPMs have been performed using a proton beam at the ITEP synchrotron. The dark current was observed to increase with the accumulated flux, such that individual pixel signals could not be observed anymore after an irradiation with about 10<sup>10</sup> protons/cm<sup>2</sup>. At the ILC, fluxes above this value are only expected very close to the beam pipe. Ageing effects of long-term low-dose irradiation still need to be studied.

Figure 5-5: Distributions measured during SiPM characterization: current, inter-pixel cross-talk and noise above nominal threshold of ½ MIP, response functions.

## 5.4 Operational experience and calibration

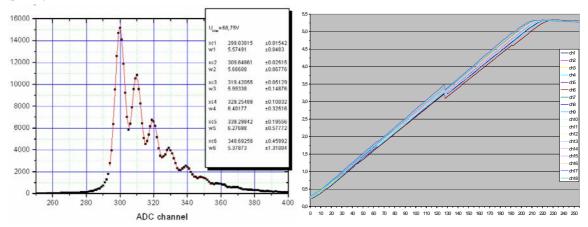

The HCAL was assembled and commissioned at DESY, where also an initial calibration of the active layers was obtained in the electron test beam. In 2006, together with ECAL and TCMT, the stack with 23 instrumented layers was exposed to electron and hadron beams of 6-45 GeV and 6-120 GeV, respectively, in the H6 beam line at the CERN SPS, In addition high intensity muon beams were available for calibration. Detector operation proved very stable, with up-times above 90%, and more than 70 million events were collected in 2006.

All calorimeter cells have been calibrated with muons. The MIP signal  $A_{\text{MIP}}$  is used as a scale for the deposited energy and to set the noise suppression threshold of ½ MIP, which yields a MIP hit efficiency of about 95%. The noise hit occupancy is then about  $10^{-3}$ , corresponding to  $\sim 0.5$  GeV on the electromagnetic (em) energy scale. The gain  $A_{\text{pixel}}$  is measured with low intensity LED light and used for non-linearity correction. The energy per cell in units of MIPs is then obtained from the formula

$$E[MIP] = A/A_{MIP} * F(N_{pixel})$$

with  $N_{pixel} = A/A_{pixel}$

where A are amplitudes measured in ADC counts. The non-linearity correction F depends only on the amplitude in units of pixels and is 1 for small amplitudes (all scale factors are absorbed in the MIP calibration factor). The function F is the inverse of the normalized response function and can be approximated as  $F = -N/N_{pixel} * \log (1-N_{pixel}/N)$  for a total of N active pixels on the SiPM. In practice F is obtained from the test bench measurements. The conversion from MIPs to deposited energy depends on the incident particle type and is taken from simulations or using the known beam energy as reference.

MIP and pixel scale are subject to temperature variations of a few percent per Kelvin. The redundant monitoring system offers various possibilities for correcting these effects, using gain, LED reference signals or direct temperature measurement. The procedures are under development and not yet applied for the first analyses which use data from sufficiently stable periods.

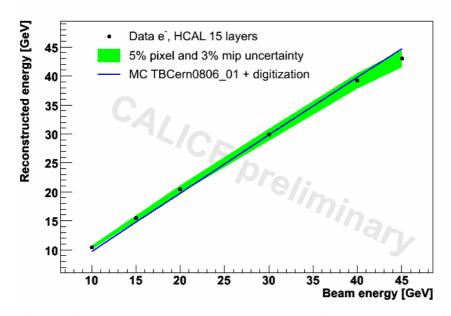

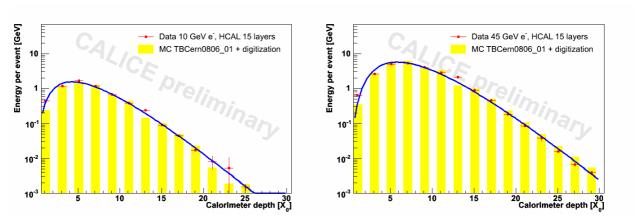

The em shower data are used to validate the calibration and the detector understanding in terms of simulations. For this reason dedicated electron runs have been taken with the AHCAL alone. After correcting the non-linear response of the SiPM using the test bench data and the *in-situ* channel-by-channel gain calibration, the calorimeter response is shown to be linear up to 45 GeV, which is by far sufficient for the hadron shower measurement, see analysis section.

The hadron analysis has just started, data show reasonable qualitative agreement with expectations. Thanks to the high granularity a rich substructure can be observed, which can e used, for example, to determine event-by-event the electromagnetic energy fraction for weighting procedures, and to test particle flow reconstruction algorithms.

#### 5.5 Future test beam programme

We presently envisage a continuation of the AHCAL prototype test beam programme including the following steps:

- In 2007 at CERN, the prototype ECAL and AHCAL will be fully instrumented and mounted on the movable stage for scans of the beam incidence angle; data taking will continue in the same beam line as used in 2006.

- In 2008, the same configuration will be exposed to test beams at FNAL, which will extend the energy range down to values as low as 1 GeV and provide the reference sample for comparison with gaseous active layers, e.g. RPCs, which can be installed in the same absorber structure later-on.

- The AHCAL can be tested with the scintillator ECAL in 2008. Production of the necessary additional AHCAL electronics components is under preparation.

- It is foreseen to exchange the steel absorber plates against lead sheets in order to test a compensating scintillator HCAL option, as proposed in the GLD concept.

• The time-sensitive very front end electronics under development for the next generation technical prototype can be used to also equip the present test beam module in order to test simulations of the time dependence of the response to neutrons in hadronic showers.

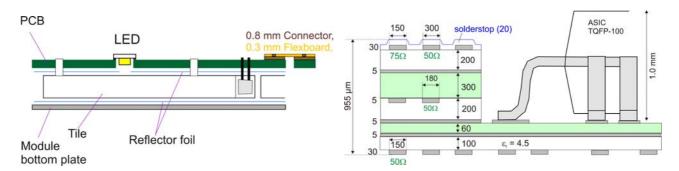

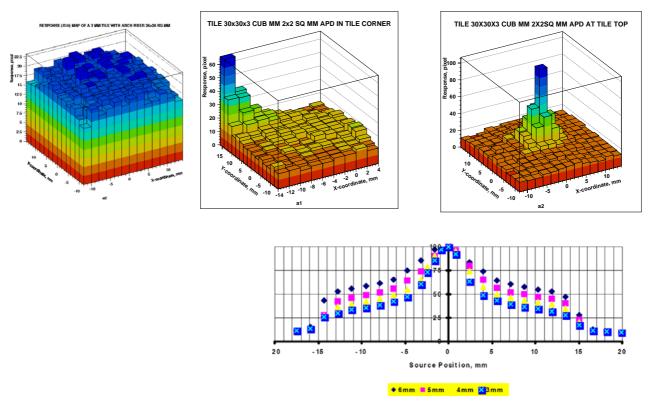

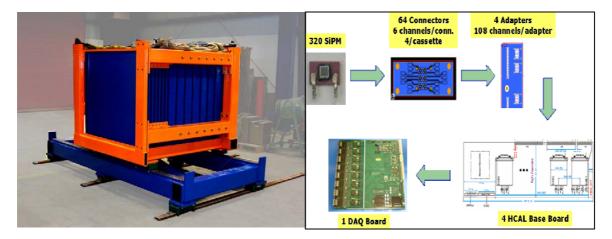

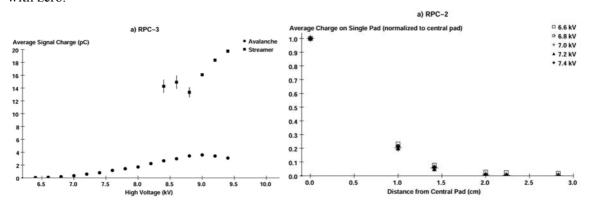

## 5.6 R&D towards a realistic tile HCAL for the ILC